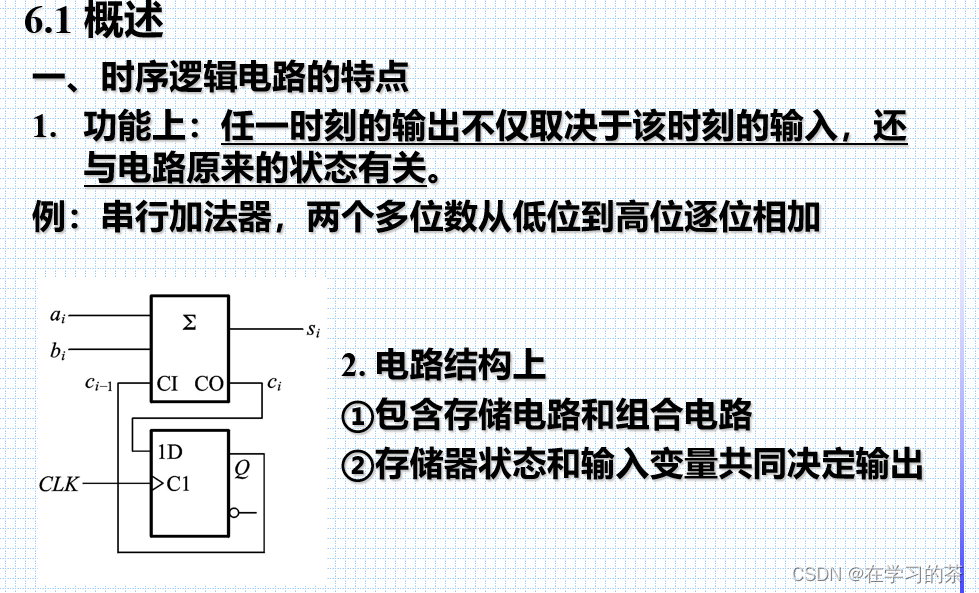

n位全加器,对串行加法器的修改

缺点还是慢,以及数据输入和输出都是串行

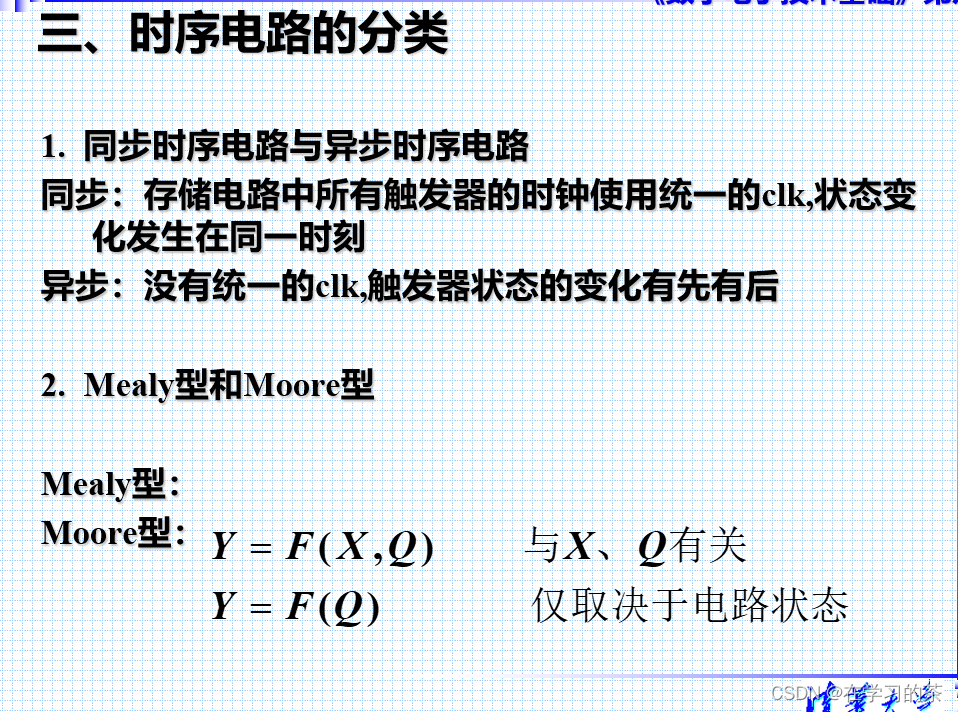

同步时序电路虽然好,简单易分析,但是由于芯片在同一时刻变化,势必造成芯片功耗升级

所以在小规模使用同步电路而大范围使用异步电路就可以使系统整体分时工作,降低尖峰电流

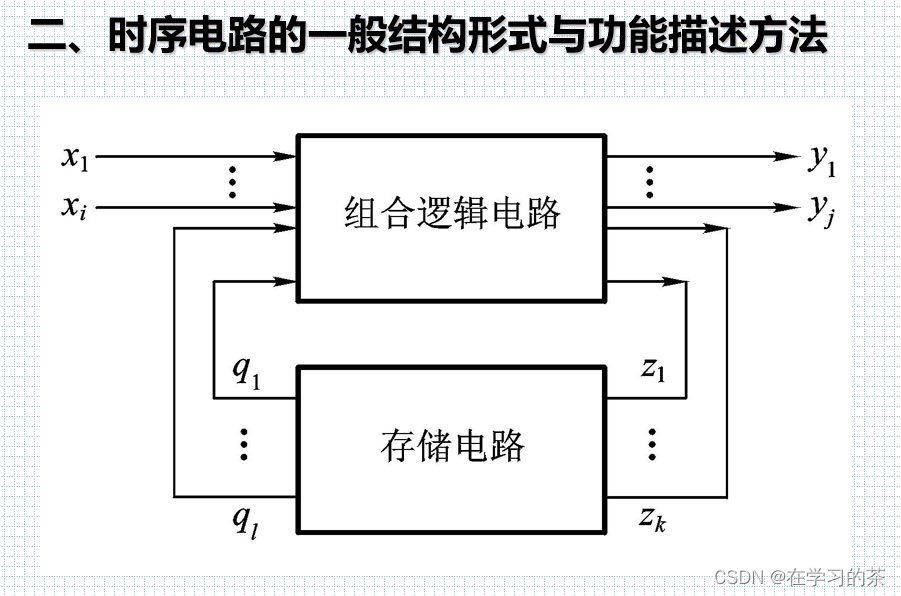

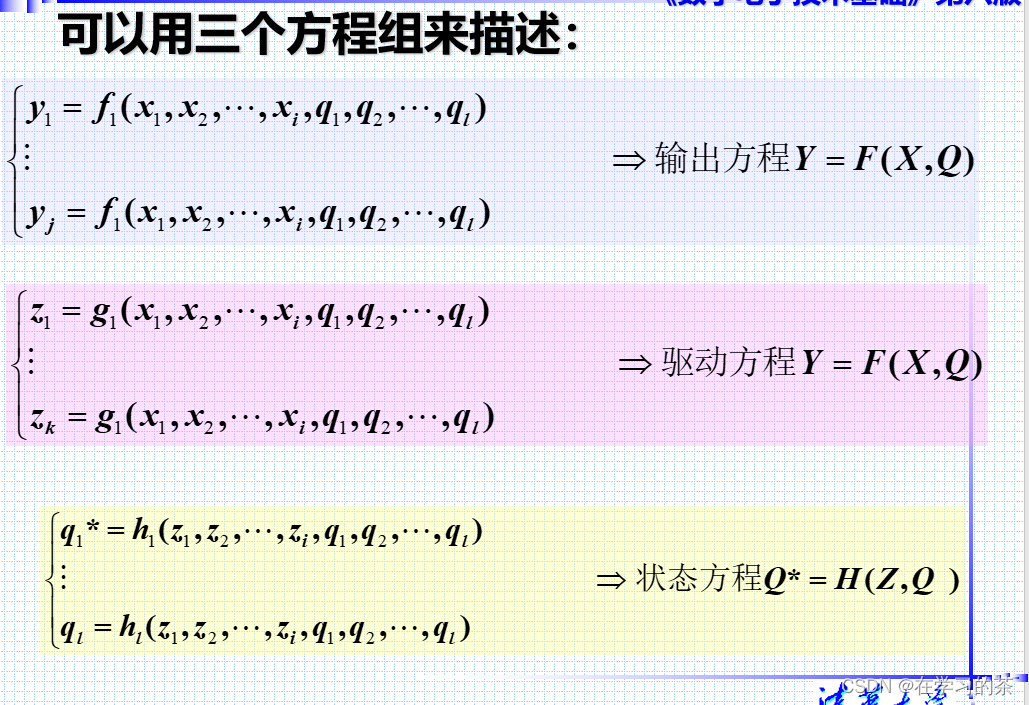

Mealy型不但取决于Q时钟,还取决于输入X,Moore就和X无关,只和时序有关

所以说时序电路是可以没有输入的

注意:

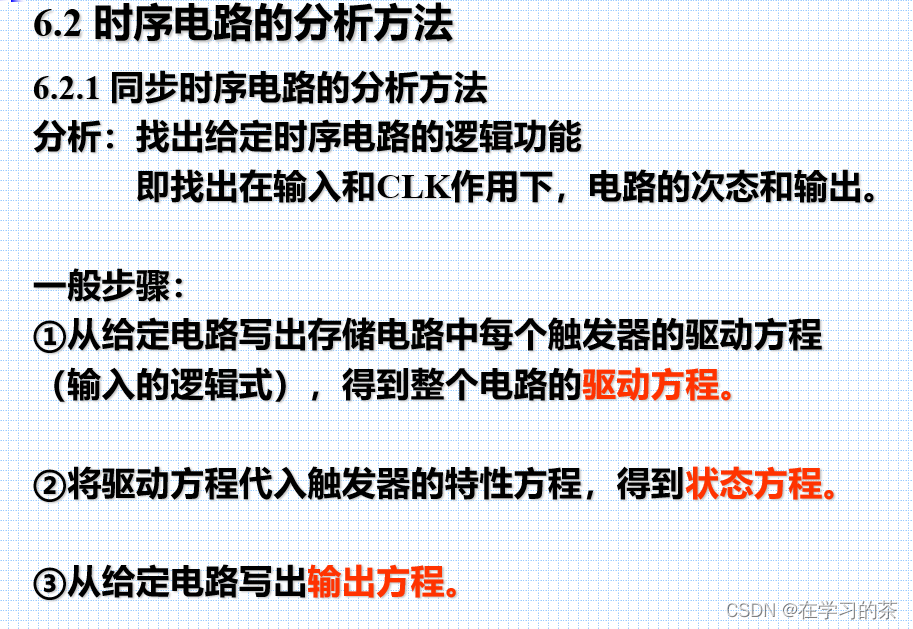

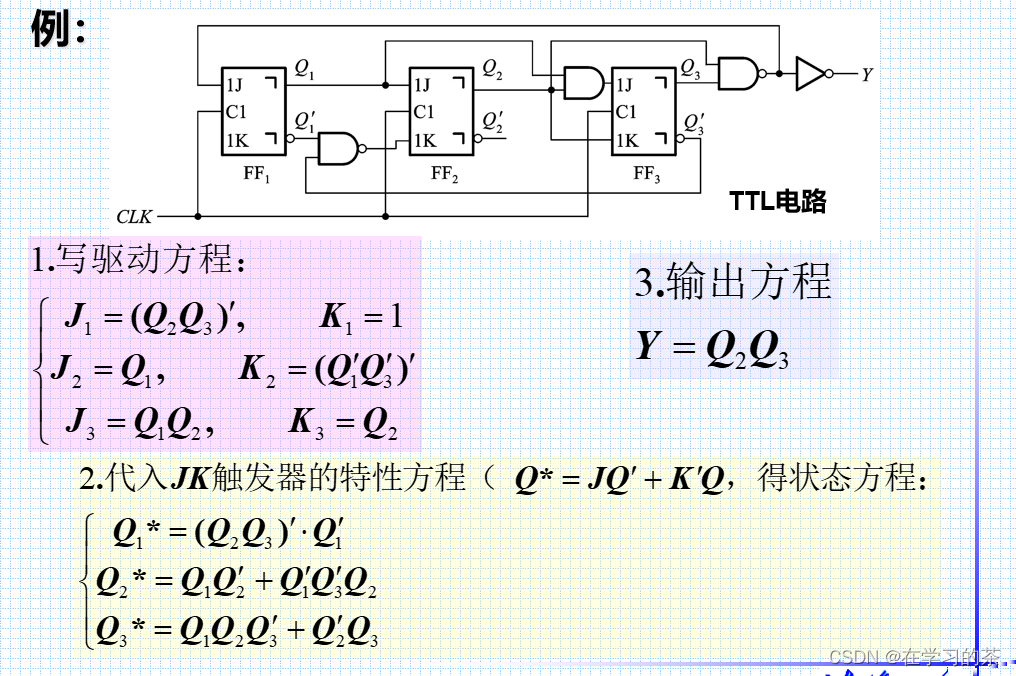

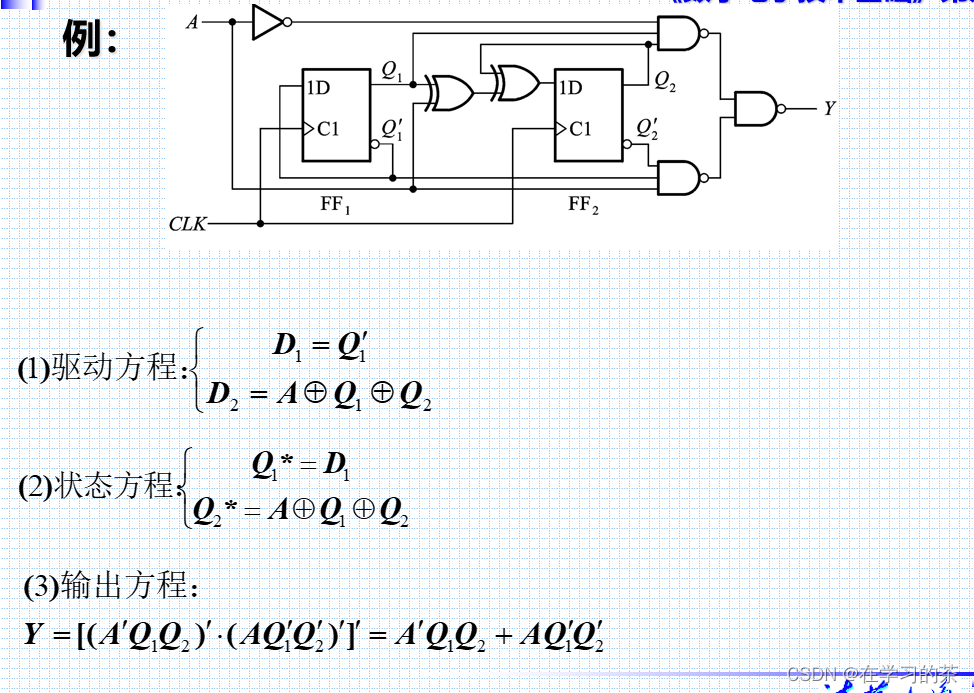

①我们驱动方程只考虑触发器的输入输出,不细扣触发器内部。驱动方程都是组合电路!可以一起写

②把驱动方程带入特性方程

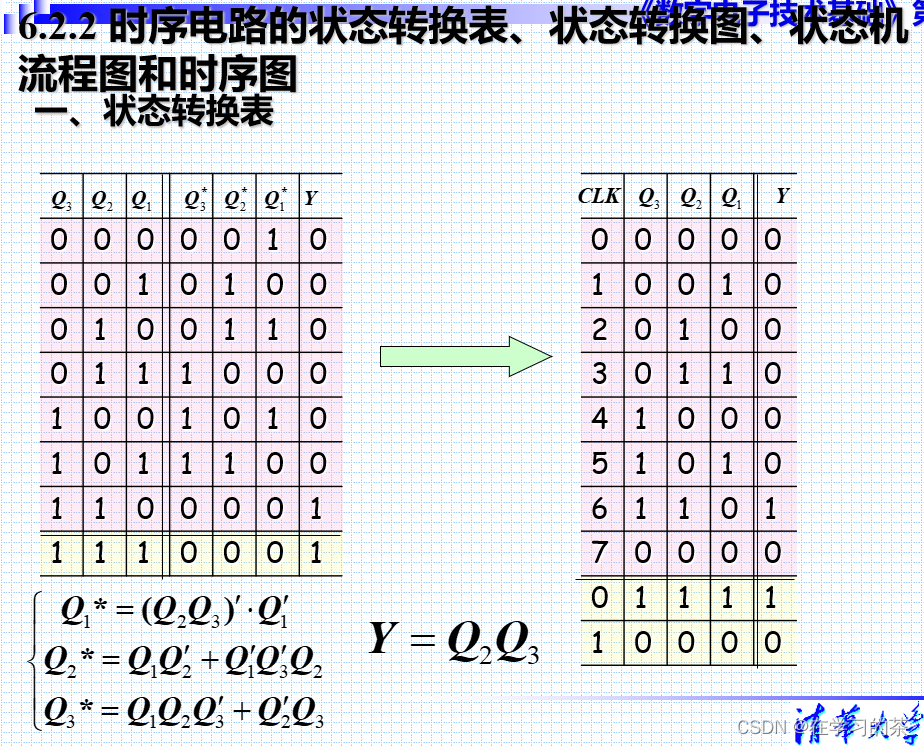

左边最后一行我们可以得出,实际上不可能出现111,但是111可以作为初态使用,比较好的是,这个电路可以在异常态后进入正常的有效循环。

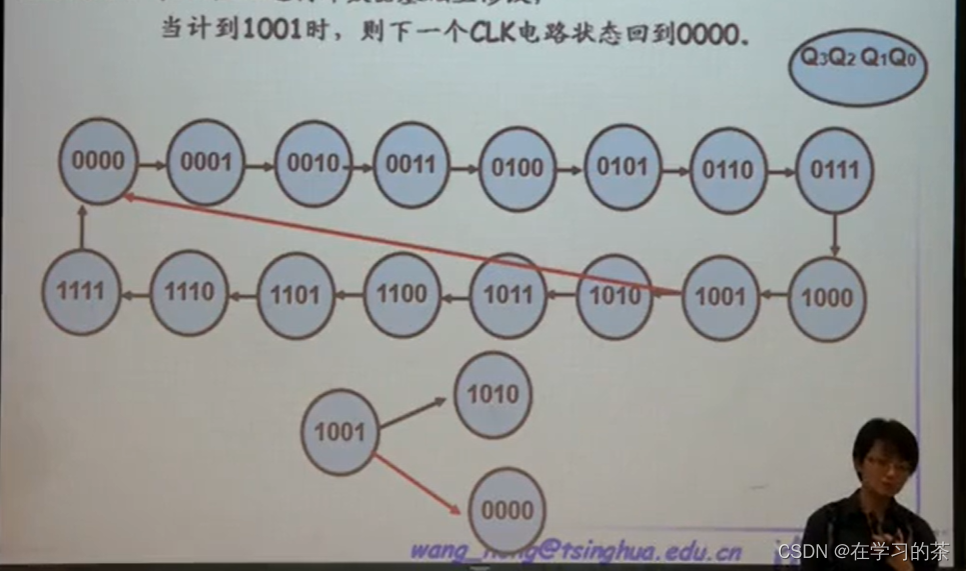

因为当我使用n位编码的时候,极大可能存在冗余编码,这些无效编码很有可能使系统死机

右边这个表就是按CLK的顺序来取值,最下面两行指的是异常的初态

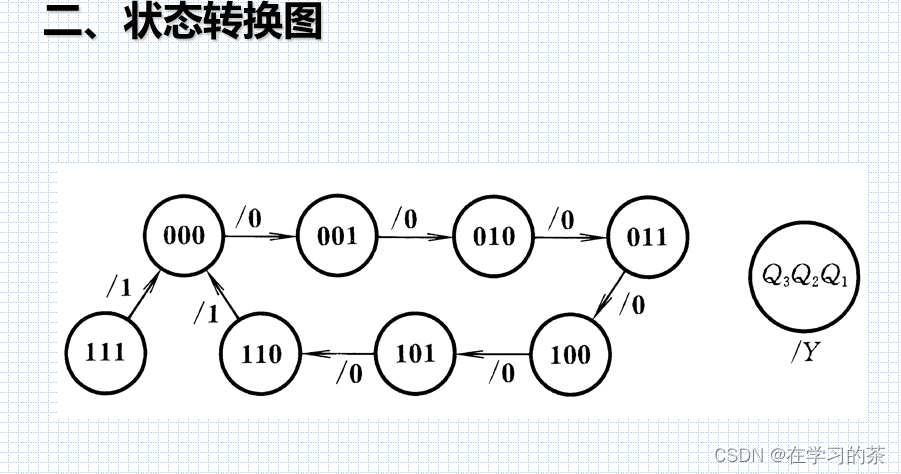

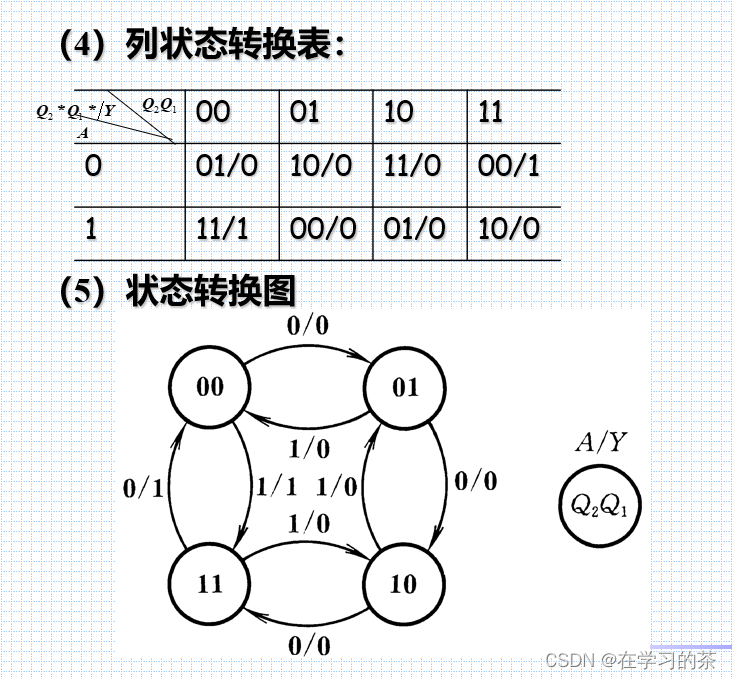

写出状态图就十分显而易见了。

箭头下方的数字是: x/y的类型,左边的x表示输入,右边的y表示输出,如果没有输入x空着就可以

在Moore型,Y取决于现态Q,非次态Q*

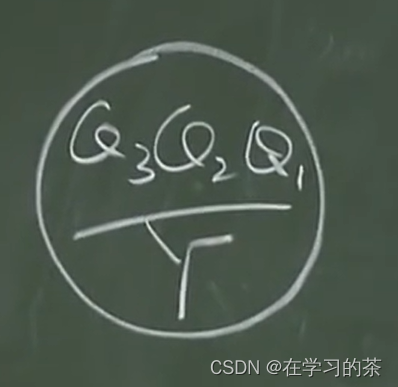

也就是moore放在圈里更直观,如下图

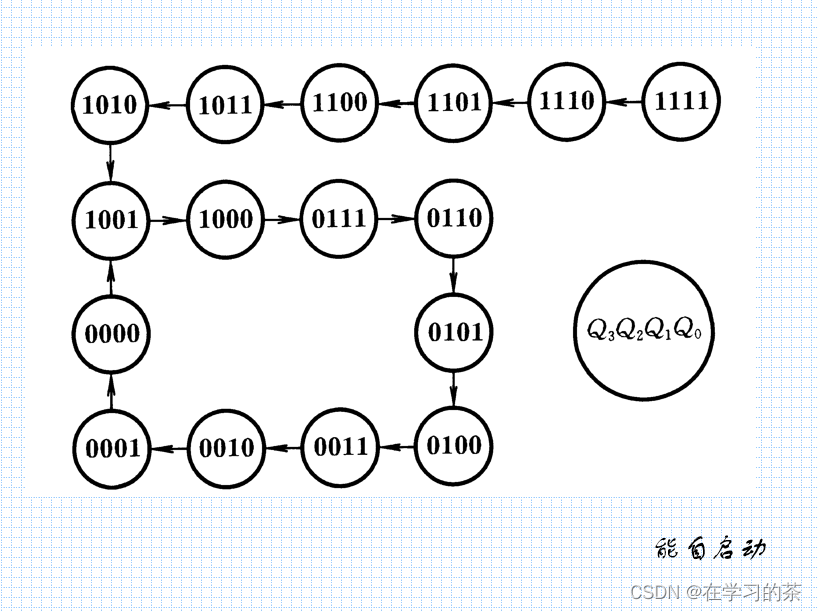

总之我们尽量保证电路可以自启动:无效态回到有效态

再来看一个

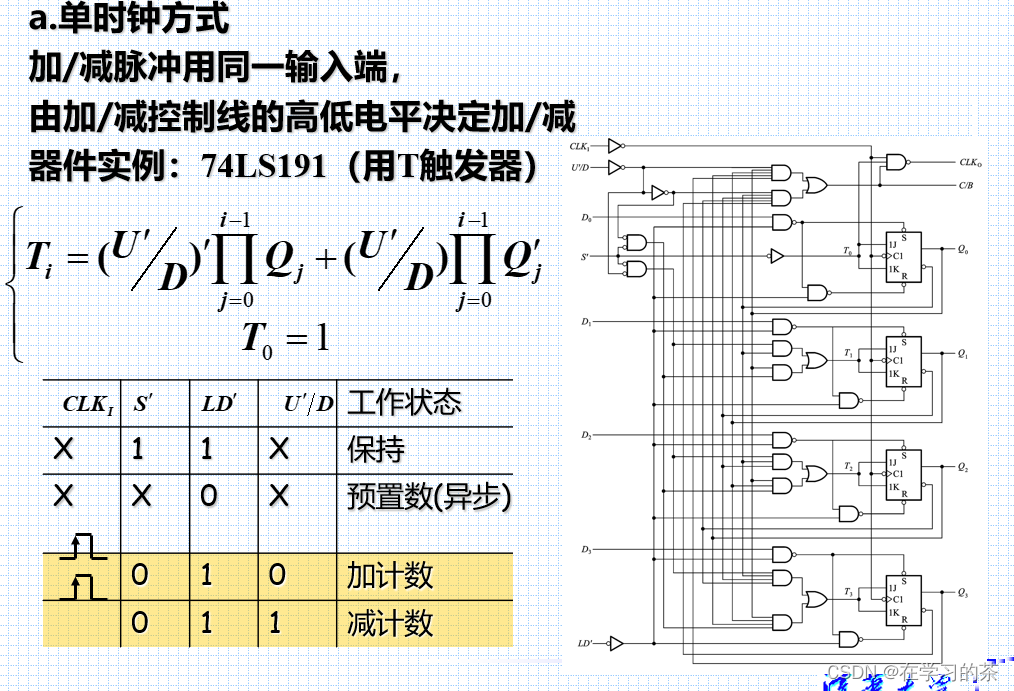

这是一个可逆的计数器,当输入是0,正向计数,反之逆向

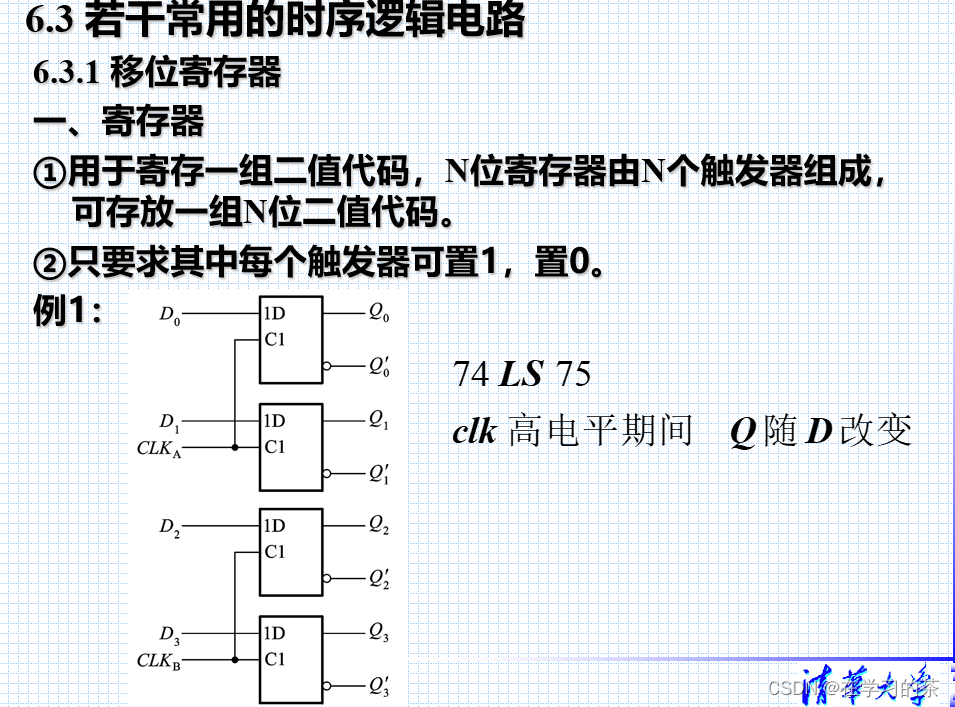

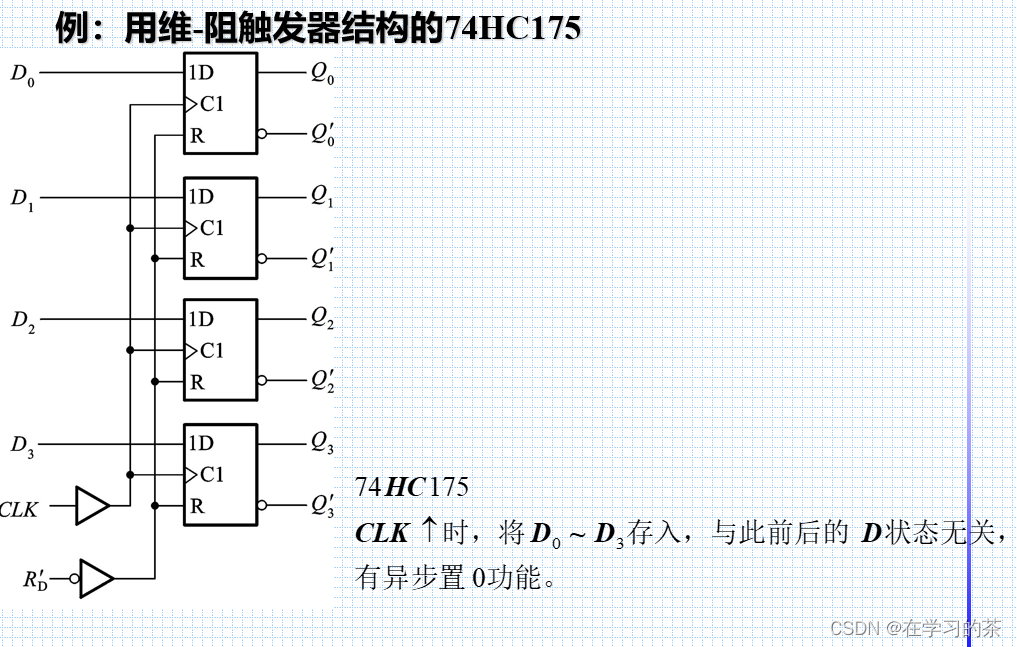

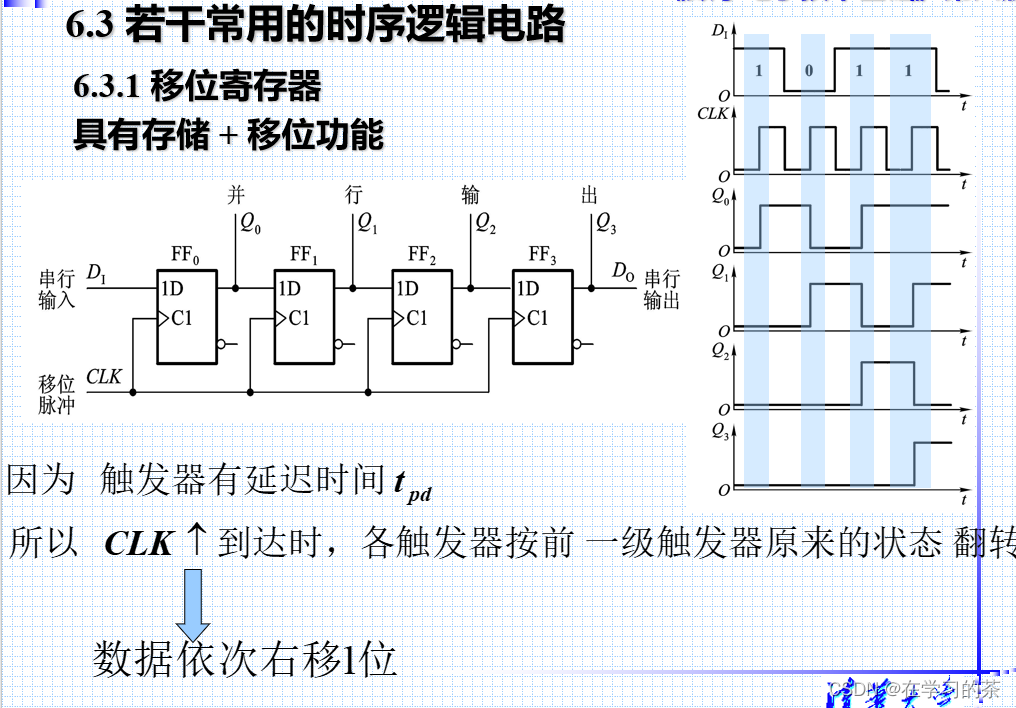

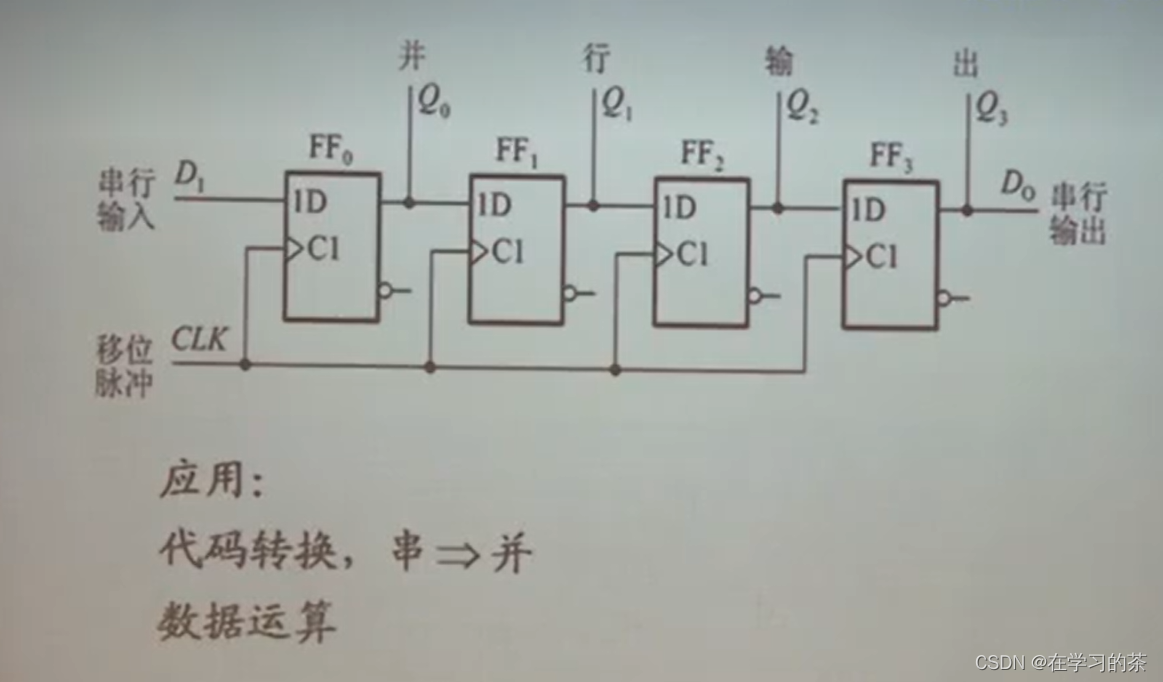

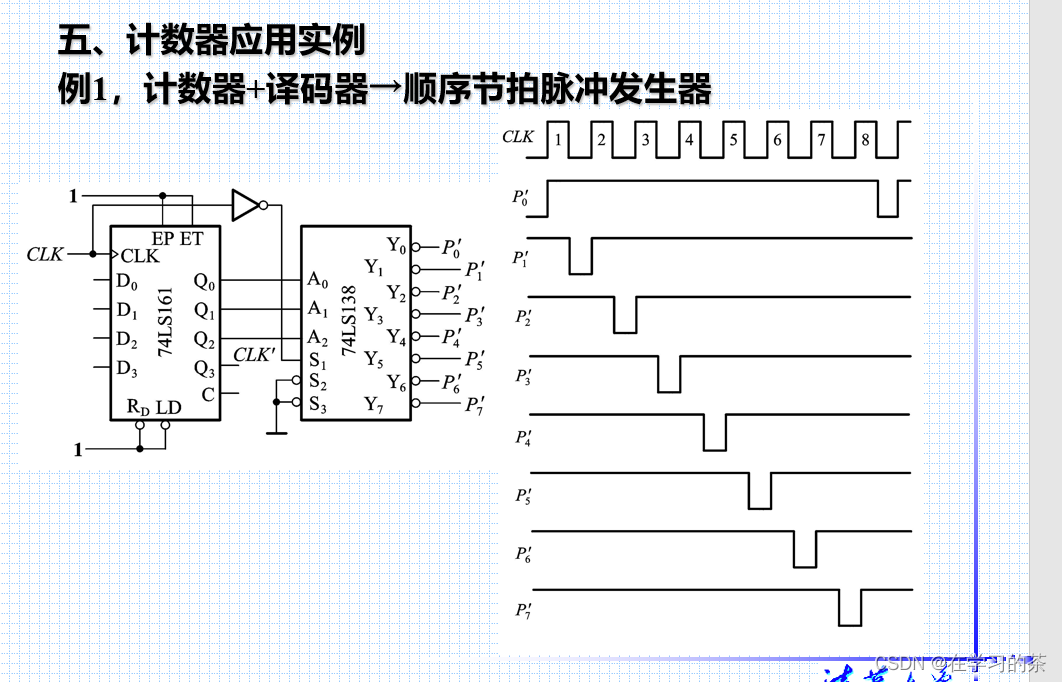

时序电路大体分为:寄存器、计数器

电平触发!

边缘触发!三角就可以看出来

R是置零端

我如果换成JK触发器,就需要把输入再加一个反相器,分别给JK构成T触发器,也可以达到同样的效果

这个触发器不可以换成电平触发,因为电平触发的话,一股脑直接跑完了,

下面四个触发器,就等价于D触发器

下面四个触发器,就等价于D触发器

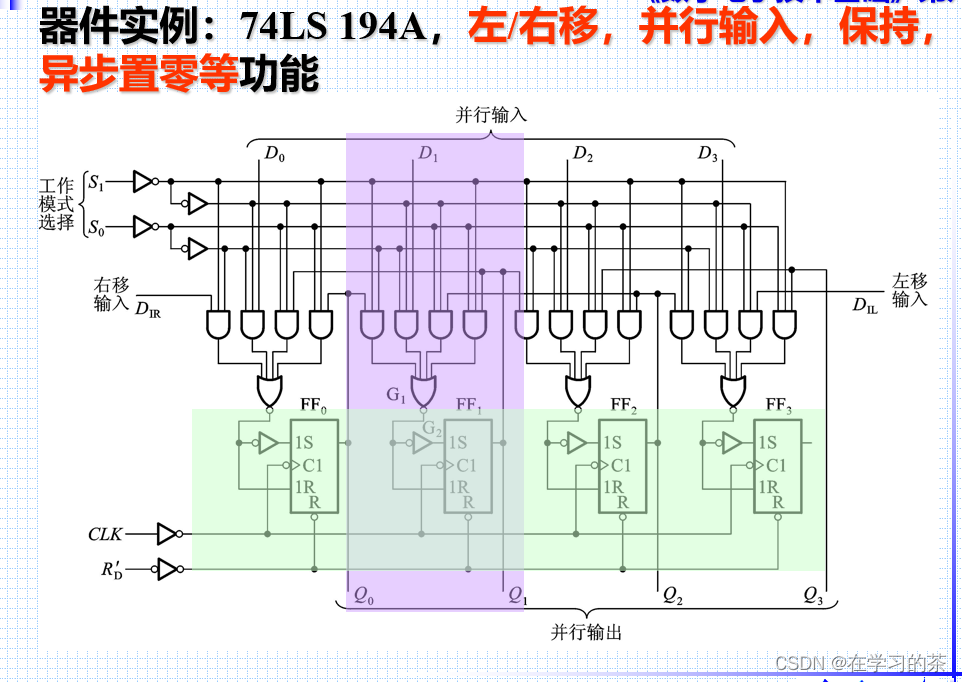

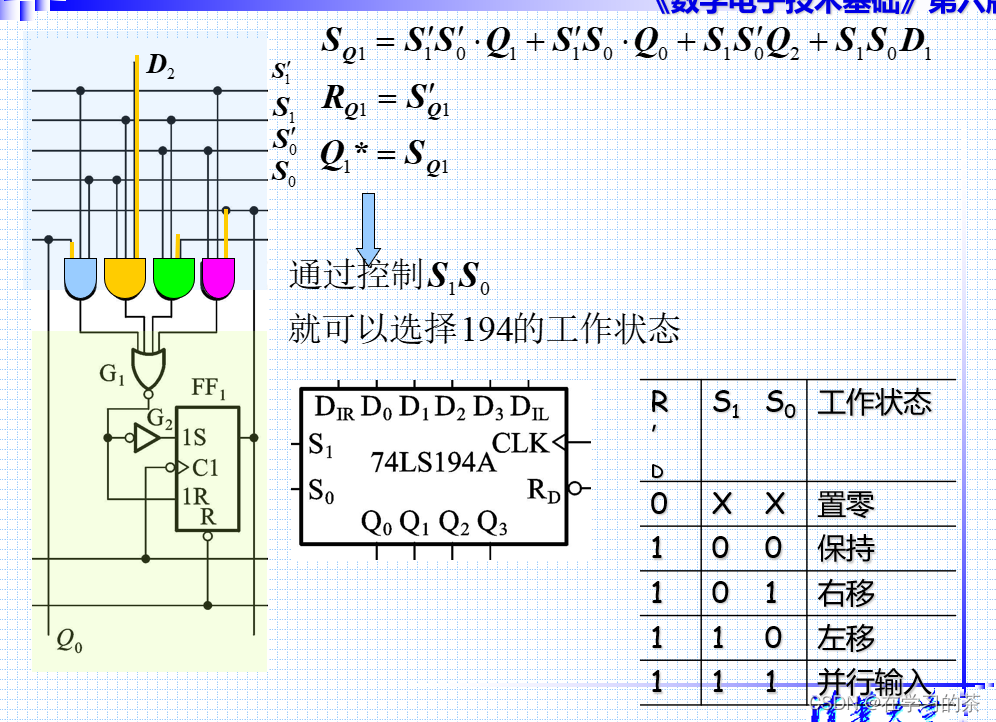

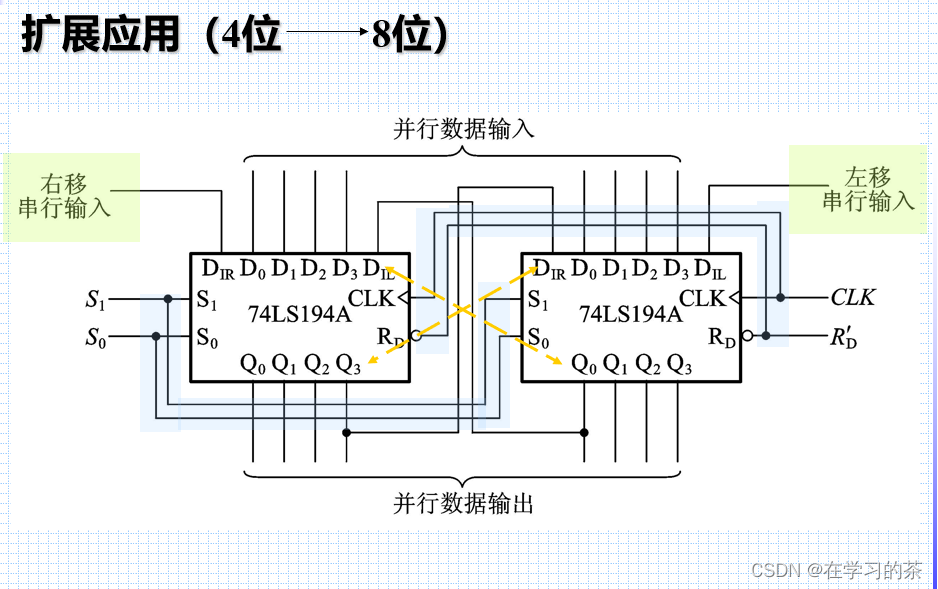

S1,S0控制左移或者右移

这个蓝、黄、绿、粉分别对应着左移、输入、右移、保持,整体这四个构成了一个数据选择器,选择工作模式(蓝、黄、绿、粉)

所以说,S0、S1代表着选颜色

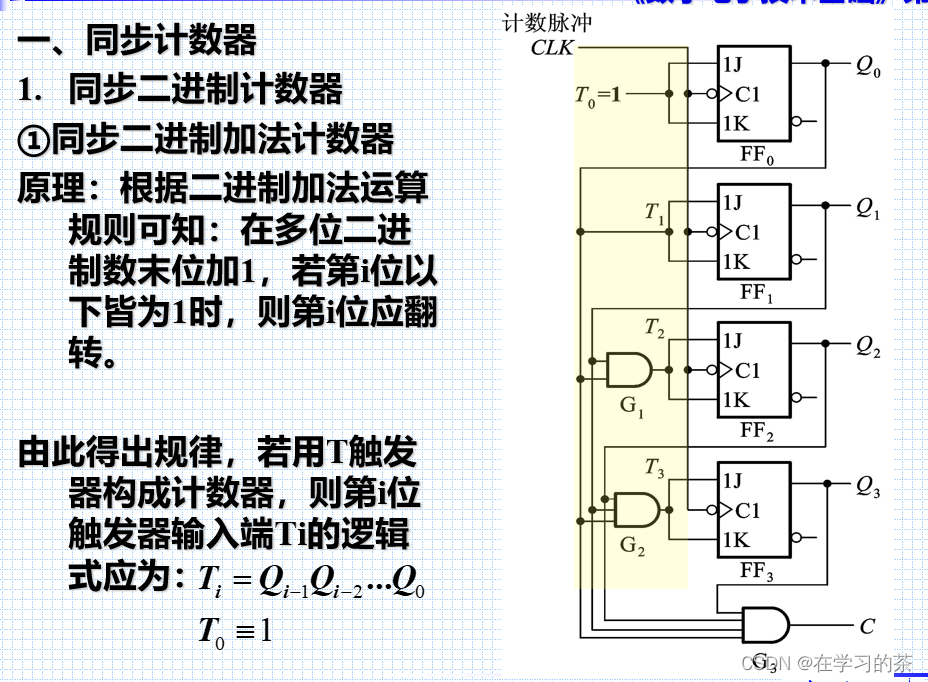

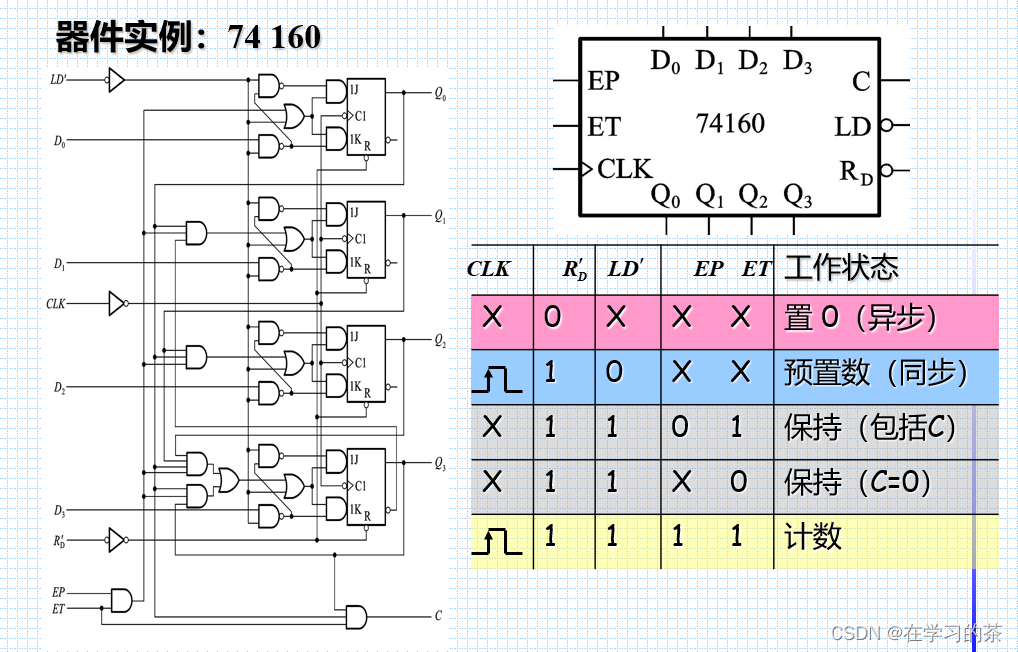

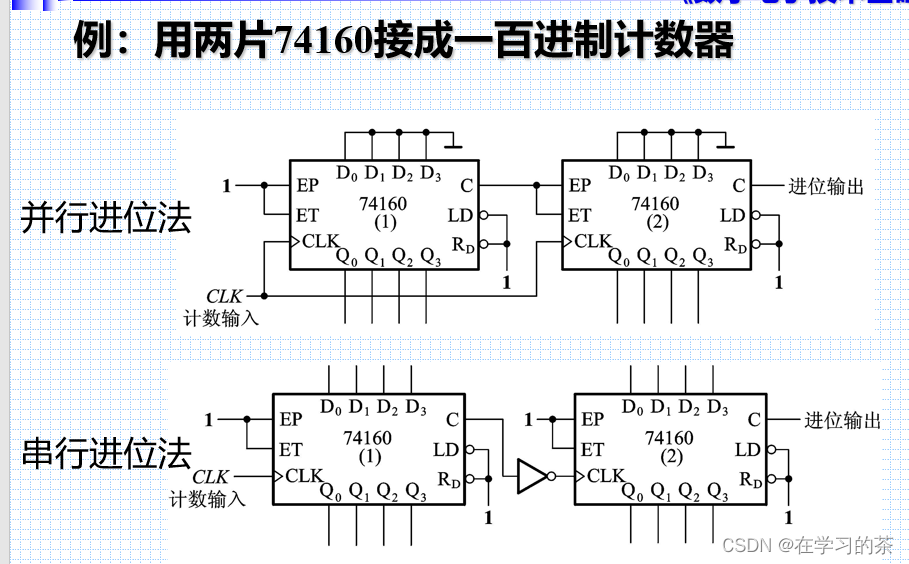

计数器

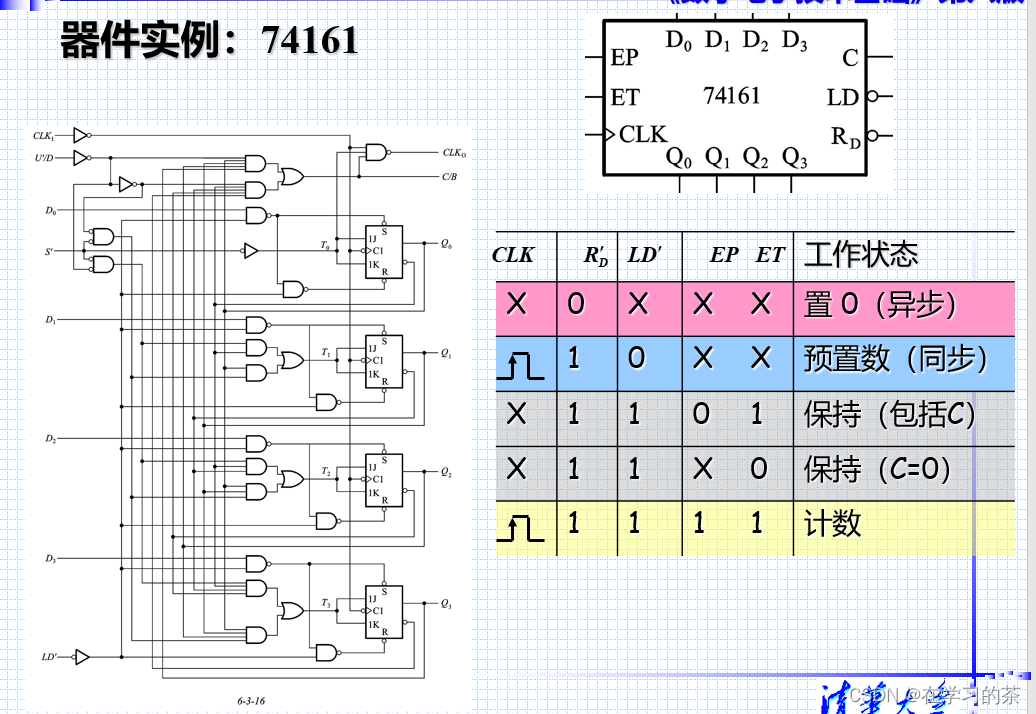

C属于进位信号

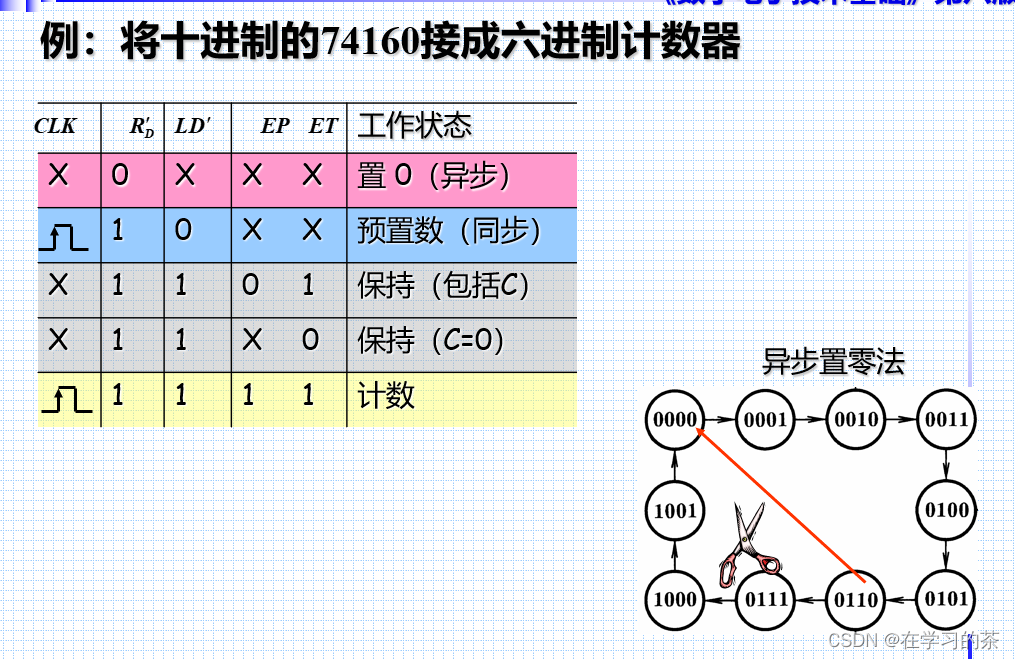

预置数同步,就是把D0-D3写道Q0-Q3

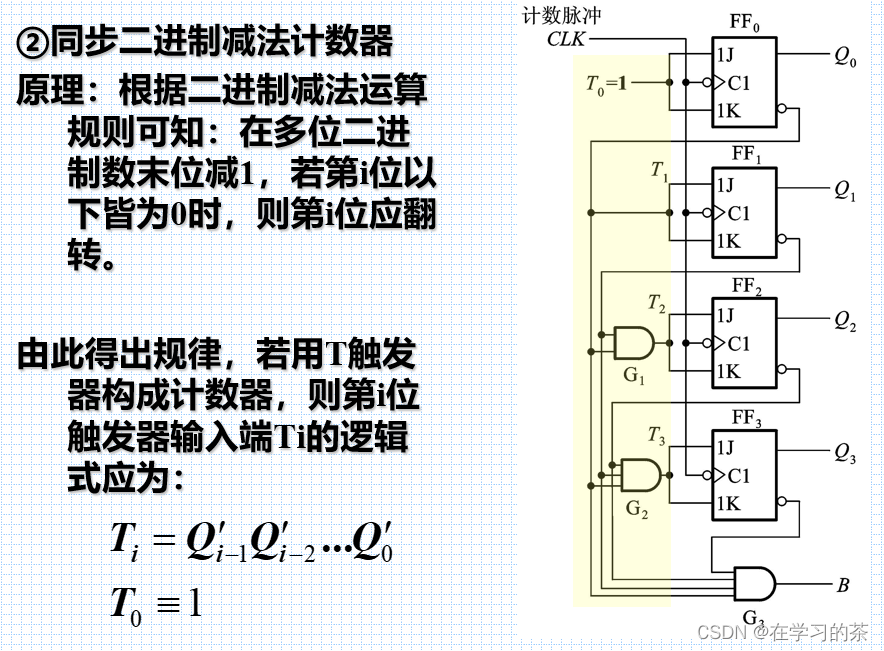

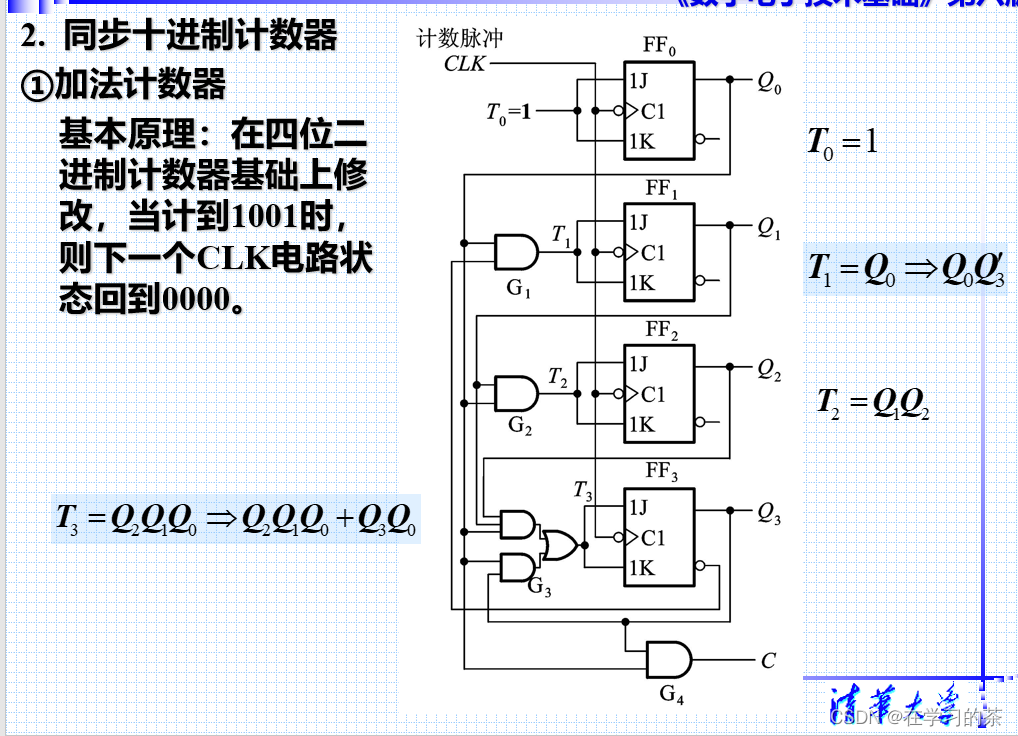

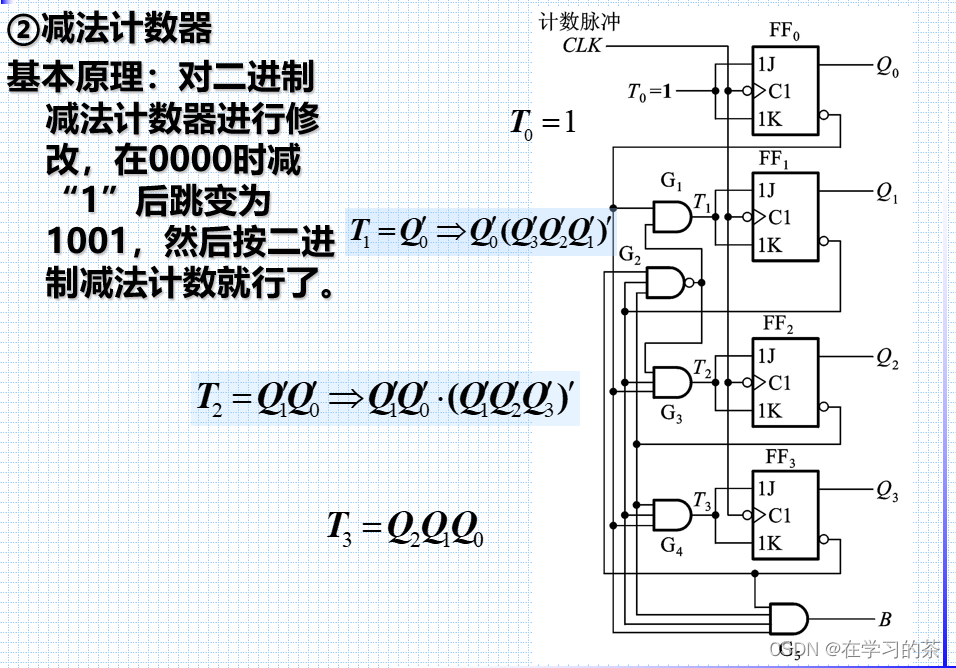

T3的逻辑式就是为了跳变新规则

我们期望的状态。

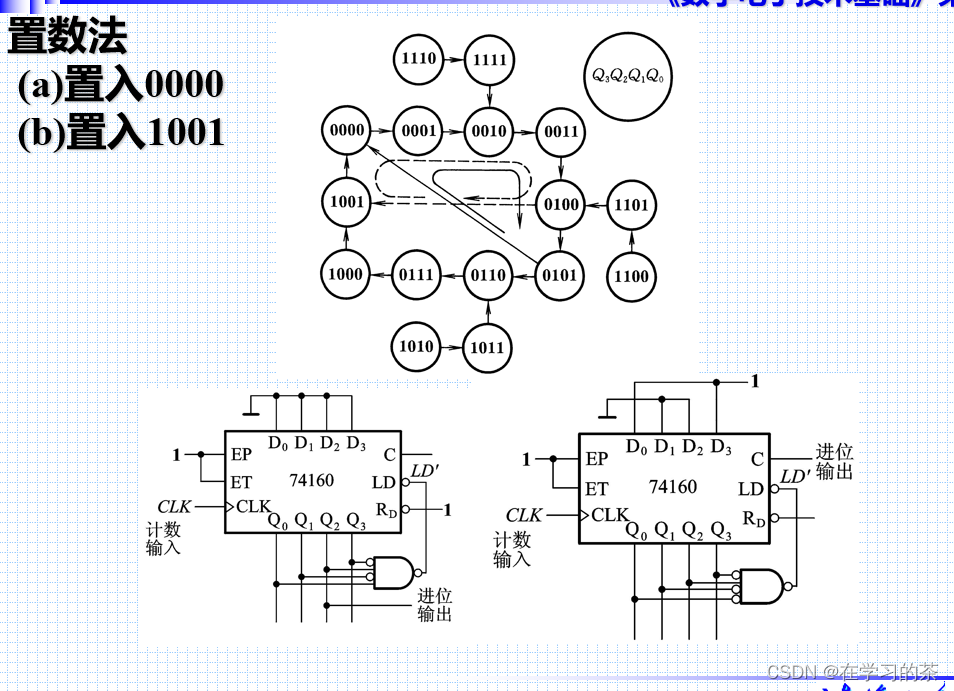

①1001到0000,改T3

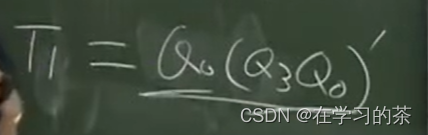

②1001不到1010,,改T1

这个1001不到1010的推到是:在Q0=1的同时,Q3和Q0不同时为1才能进位,如此才能限制。

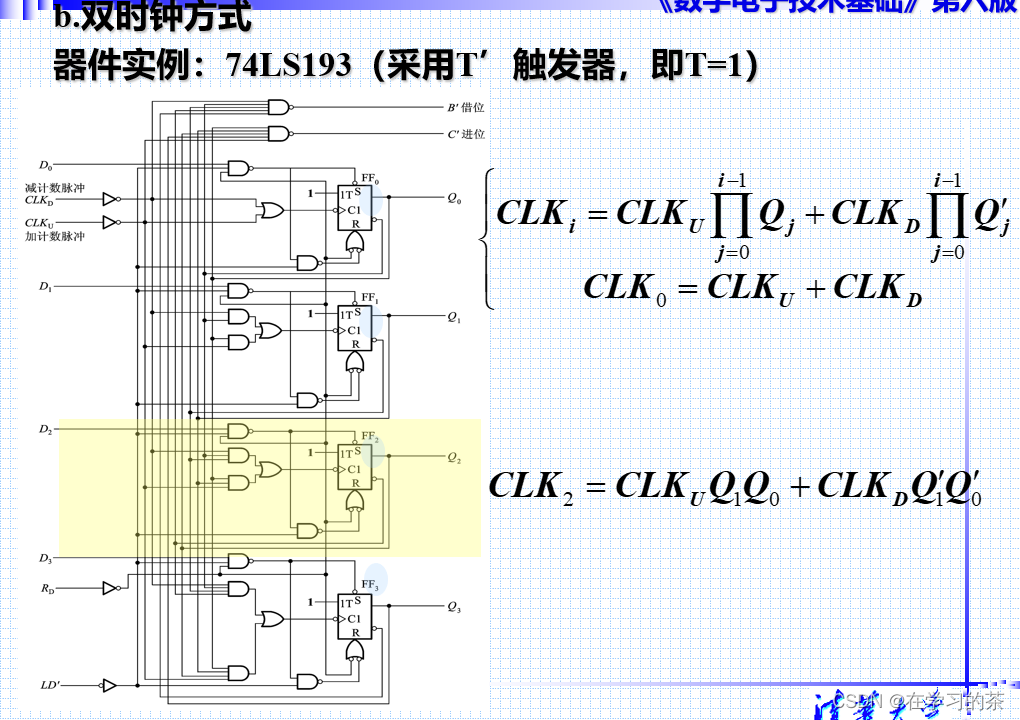

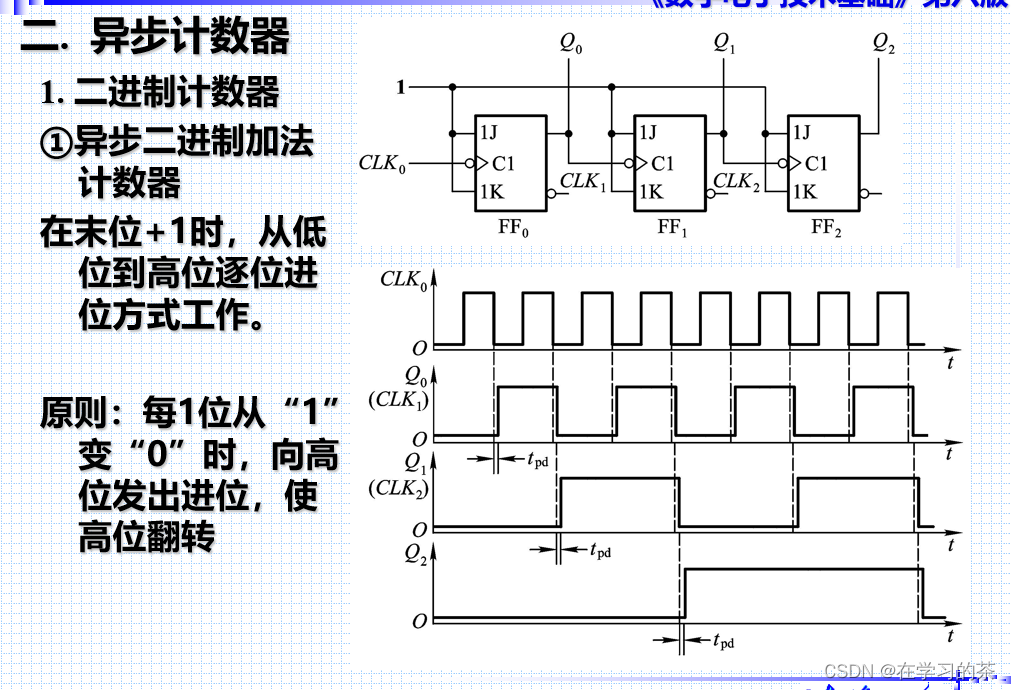

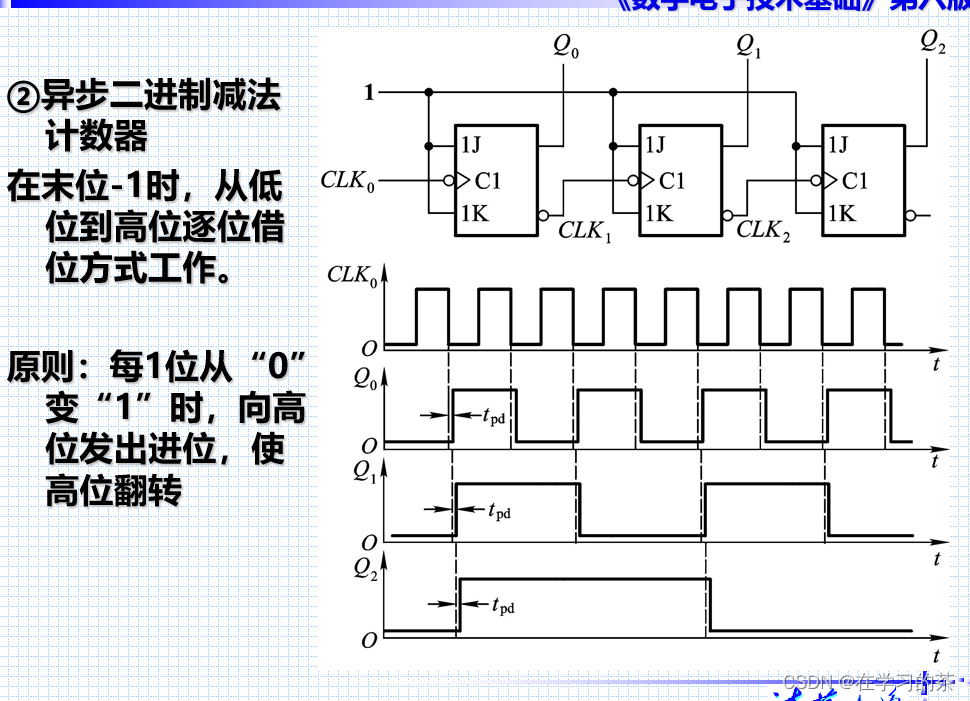

把Q反接到CLK

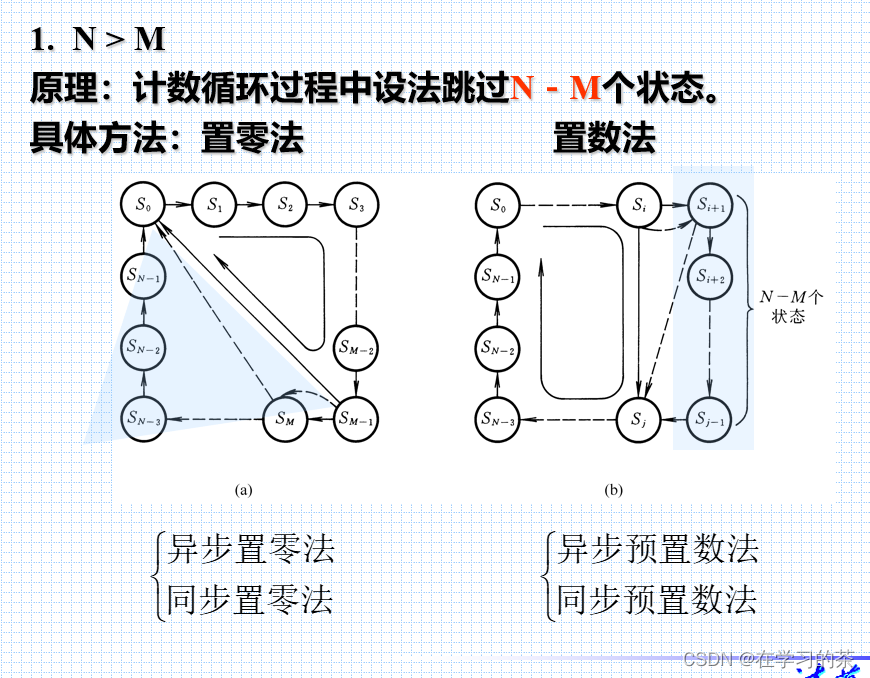

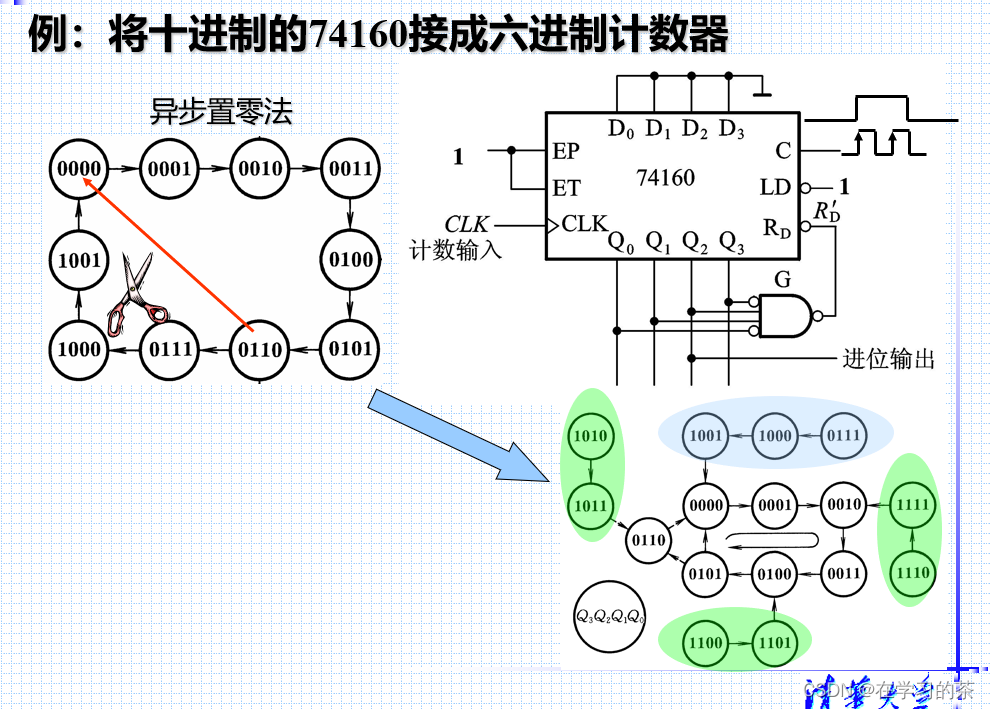

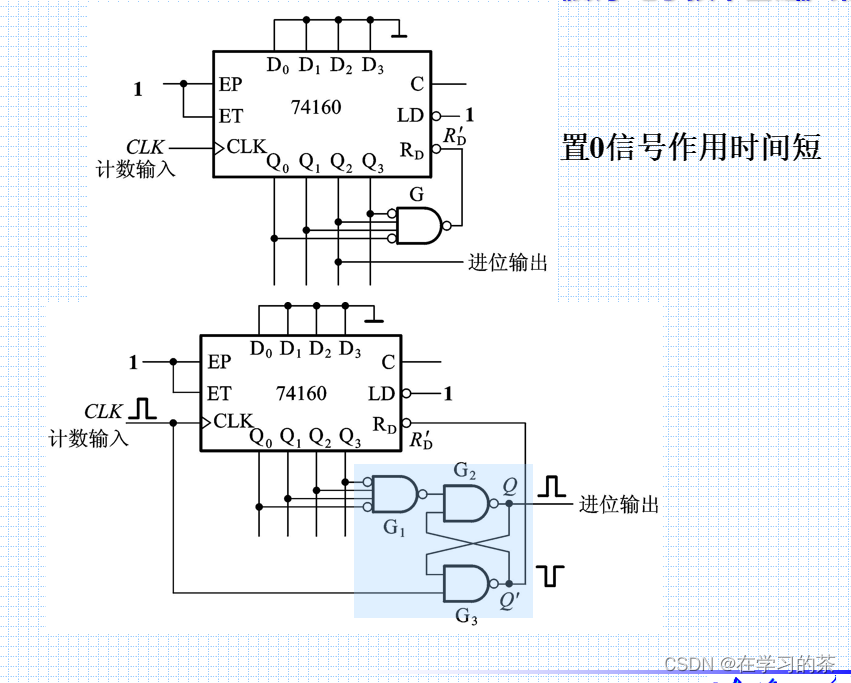

还有一个点,如果使用0101跳转0000的话,当到达0101就一瞬间把输出给到置零端,瞬间跳到0000不合适,因为其他都是闪一个时钟

所以要用下一个 状态

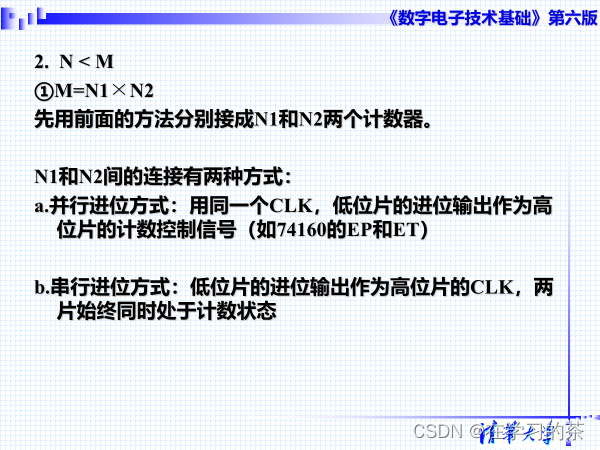

这个时候,若是直接接在CLK上,因为CLK原本是0的,C接过来变成1,因为CLK是上升沿,他就会直接计入这个信号,那么在这一瞬间,显示器可能会显示19

循环检查各个引脚

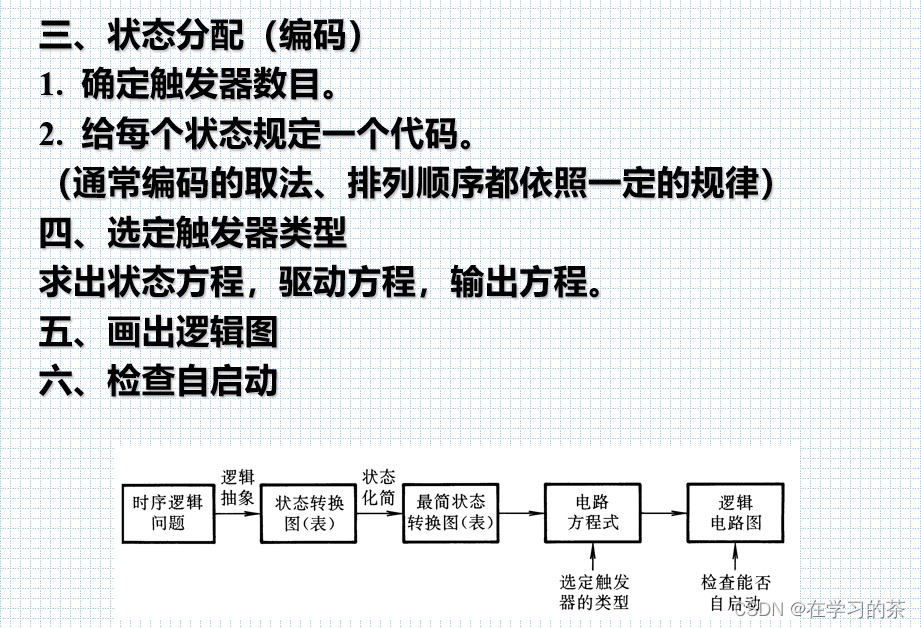

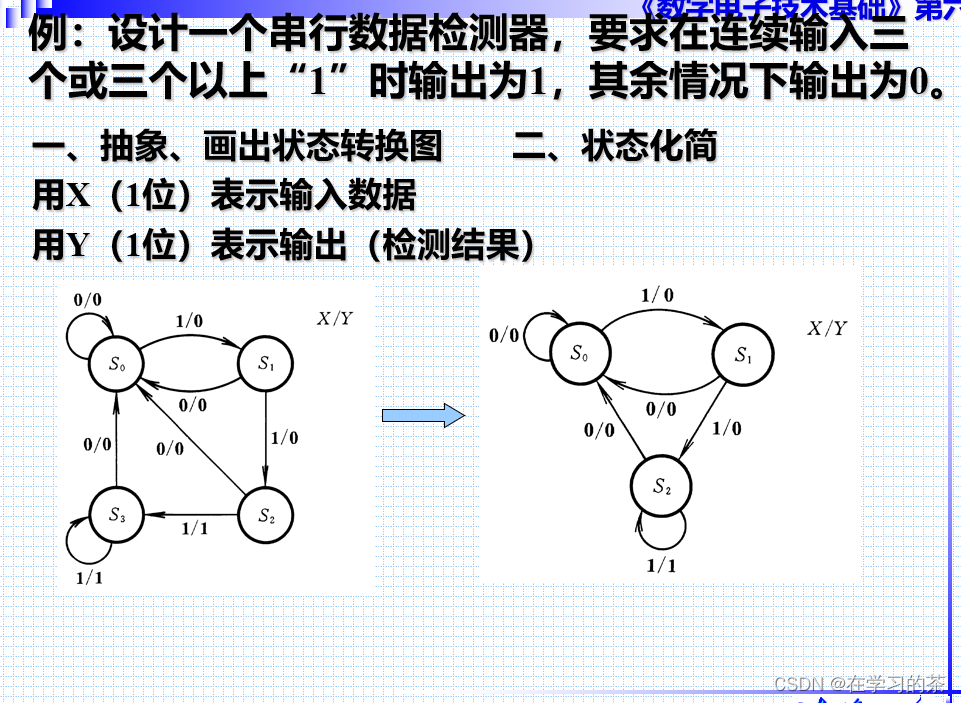

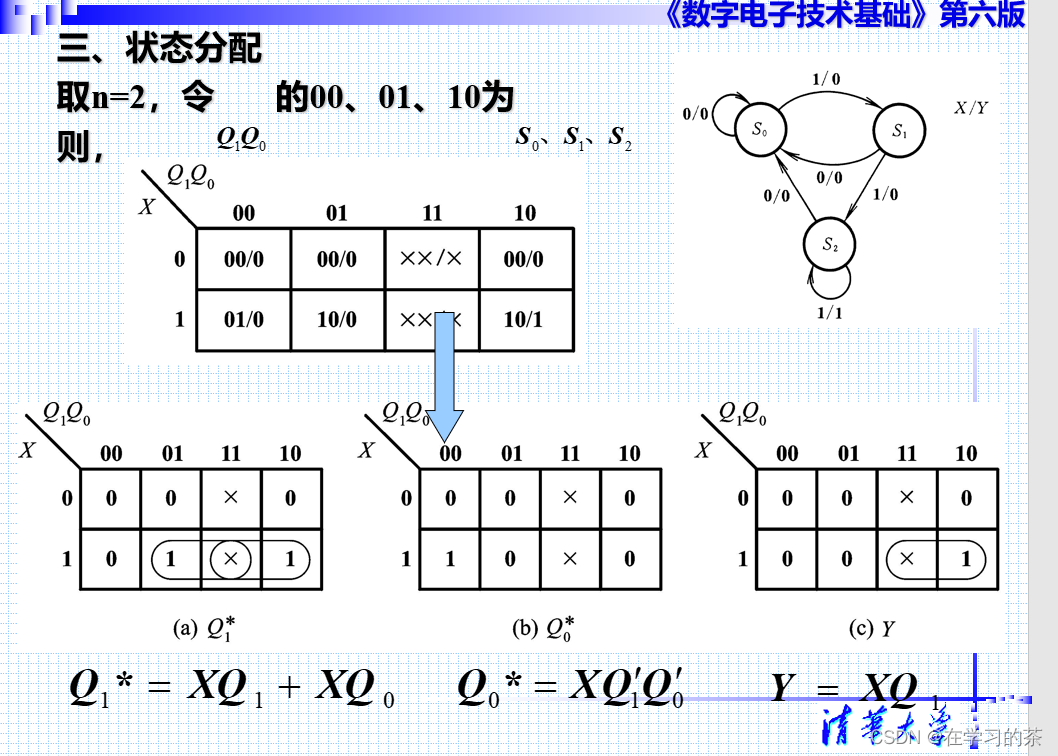

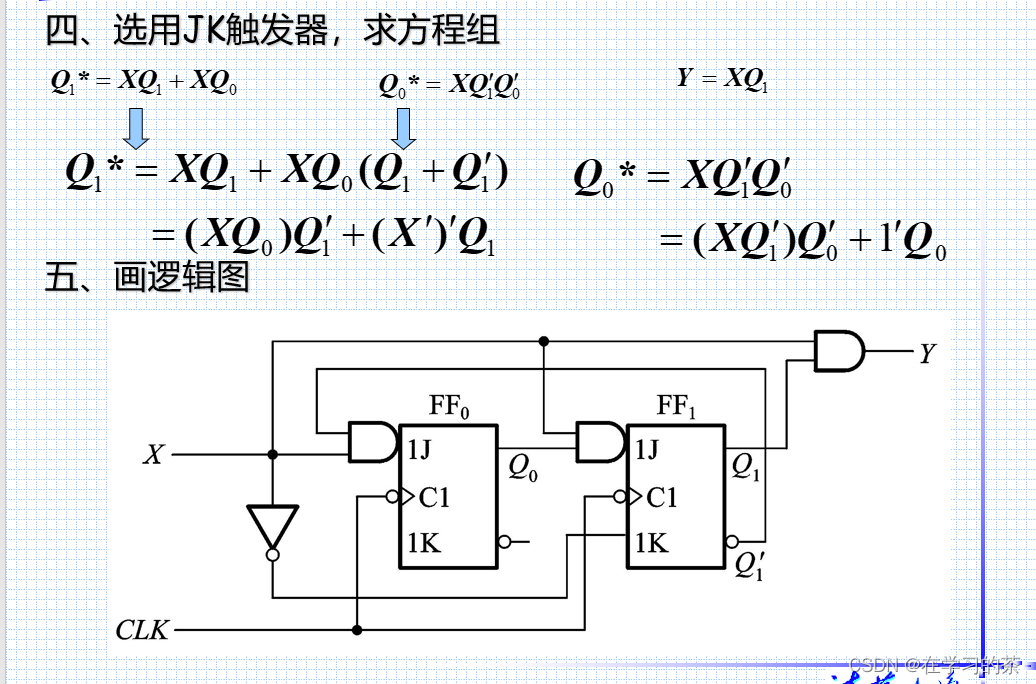

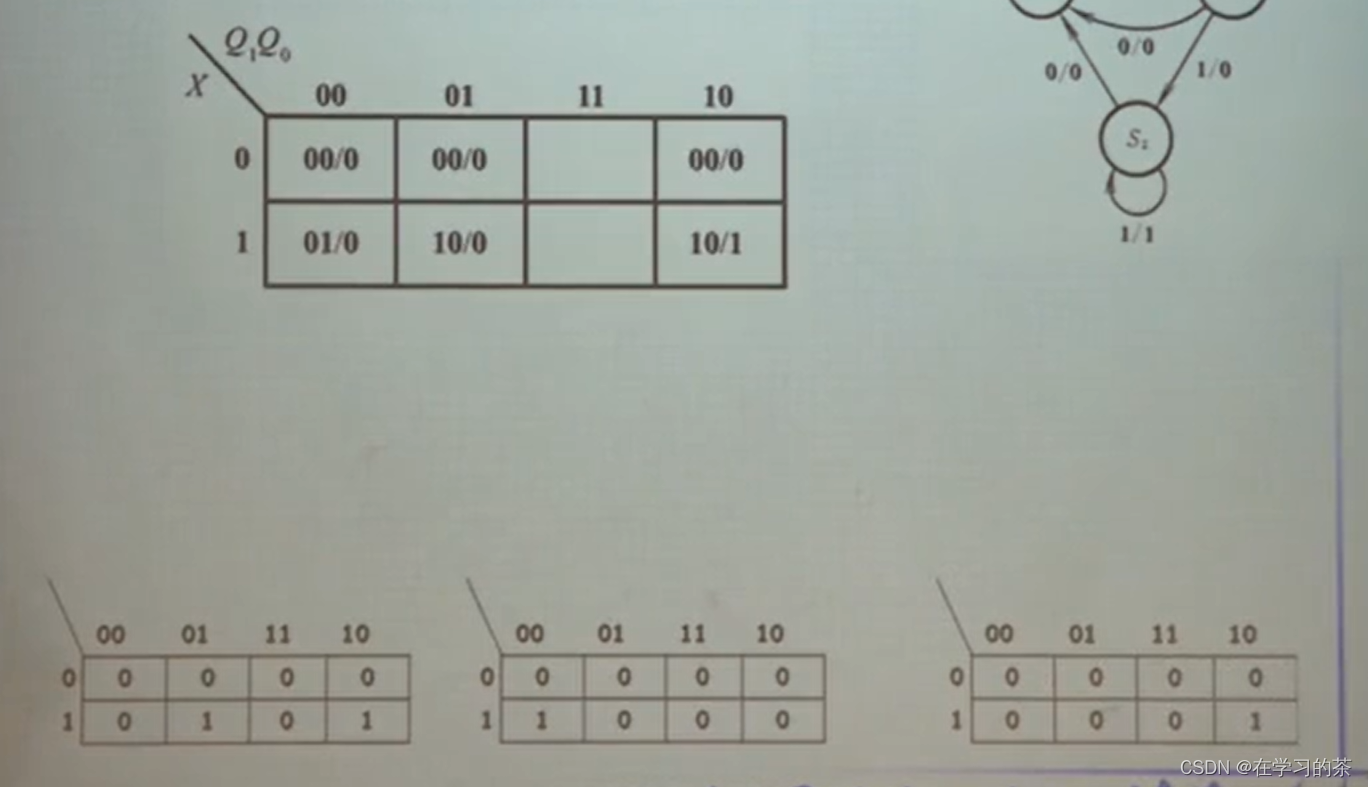

时序电路的设计

例子

这里的化简是,两个状态有相同的输入下,有相同的输出和次态

我们特地把电路搞复杂,目的是使无效态回到初态

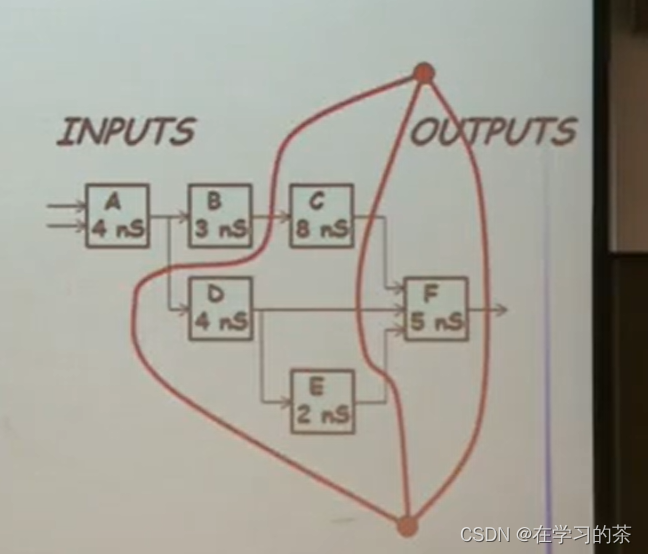

加流水线

①画输出,与电路相交的地方加触发器,意思就是此处数据都要准备好

②继续分流水

③本来应该画DE之间,但是你看D+E和C的时间差不多,那就这样画

把8ns的C改成2流水线的4nsC

最后

以上就是爱笑故事最近收集整理的关于数字电路-06 时序电路计数器 时序电路的设计加流水线的全部内容,更多相关数字电路-06内容请搜索靠谱客的其他文章。

发表评论 取消回复