文章目录

- 基本RS-FF

- 与非门构成的RS-FF

- 或非门构成的RS-FF

- 同步FF/时钟FF

- 同步RS-FF

- 同步D-FF

- 同步JK-FF

- 同步T-FF

- 同步触发器的缺点

- 主从触发器

- 主从RS-FF

- 主从JK-FF

- 主从D-FF

- 题型十:根据输入曲线画输出曲线

- 主从T-FF

- 主从触发器的问题

- 正边沿触发器

- 正边沿触发D-FF(维持阻塞D-FF)

- 正边沿触发JK-FF

- 正边沿触发T-FF

- 触发器的应用

- 分频电路

- 消除噪声电路

- 触发器的分类

组合逻辑电路的基本单元是逻辑门,其并没有记忆功能。

而时序逻辑的额基本单元是触发器FF,其具备了记忆功能。

其能够存储一位二进制信息,也被称为锁存器。

我们规定 Q Q Q是触发器的状态。

基本RS-FF

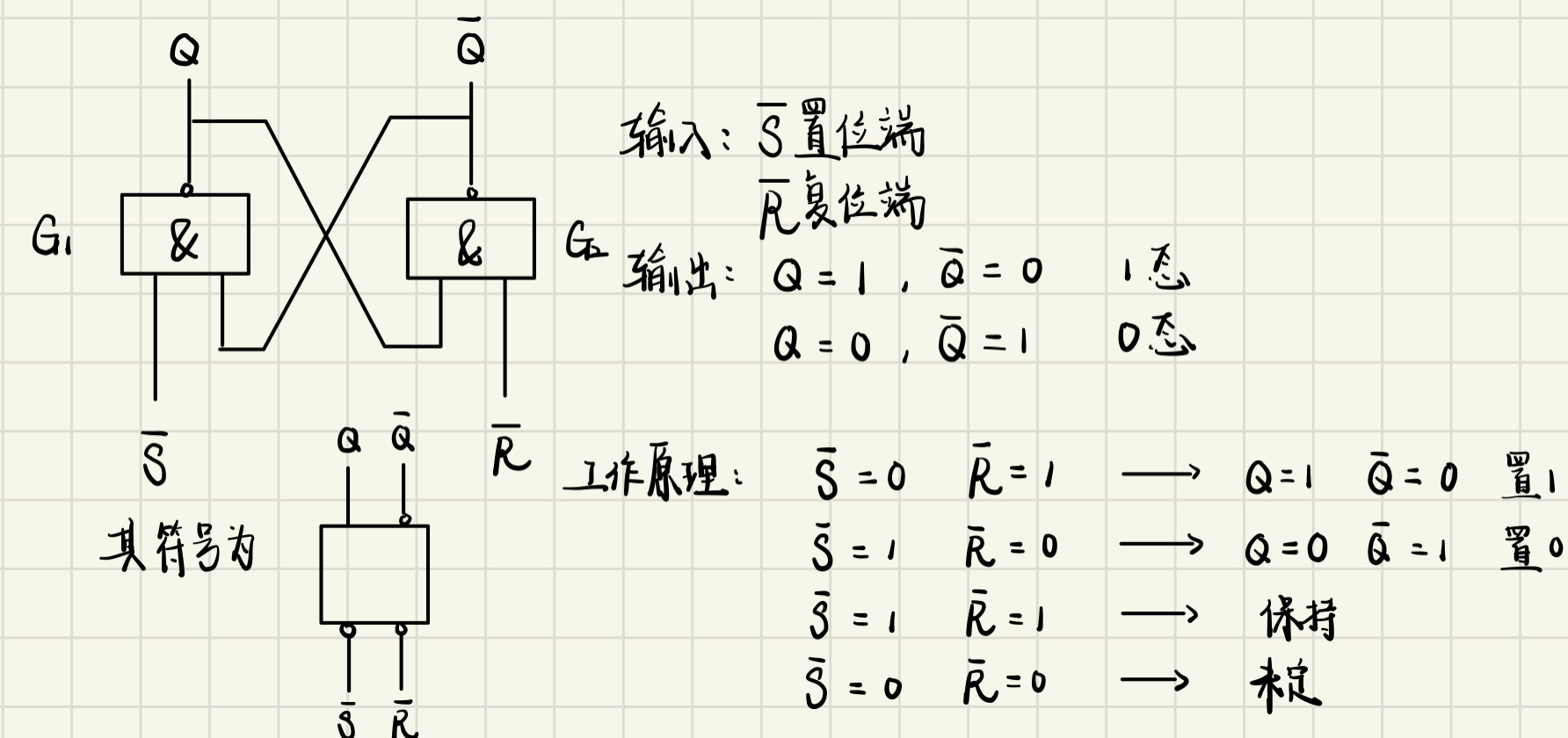

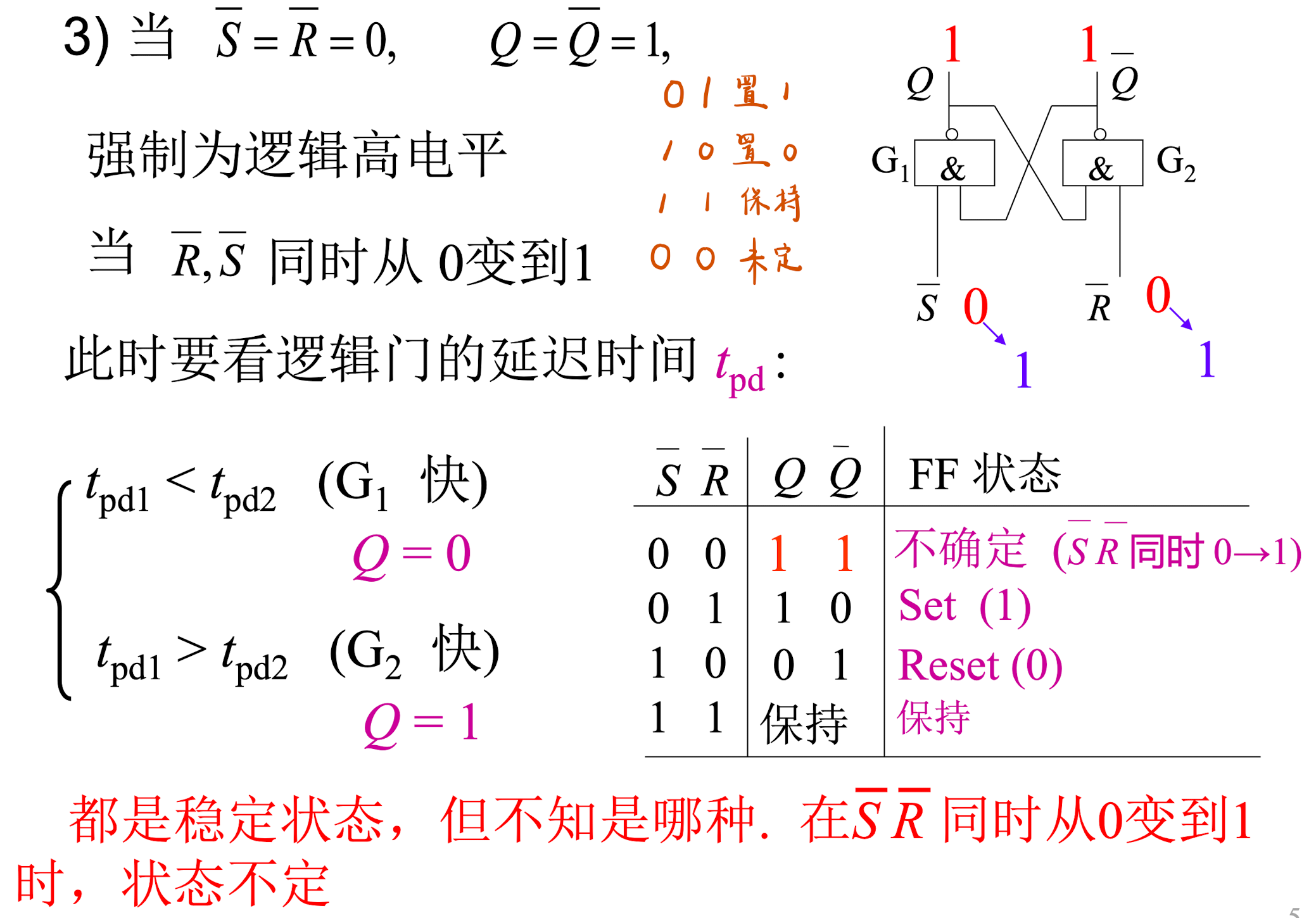

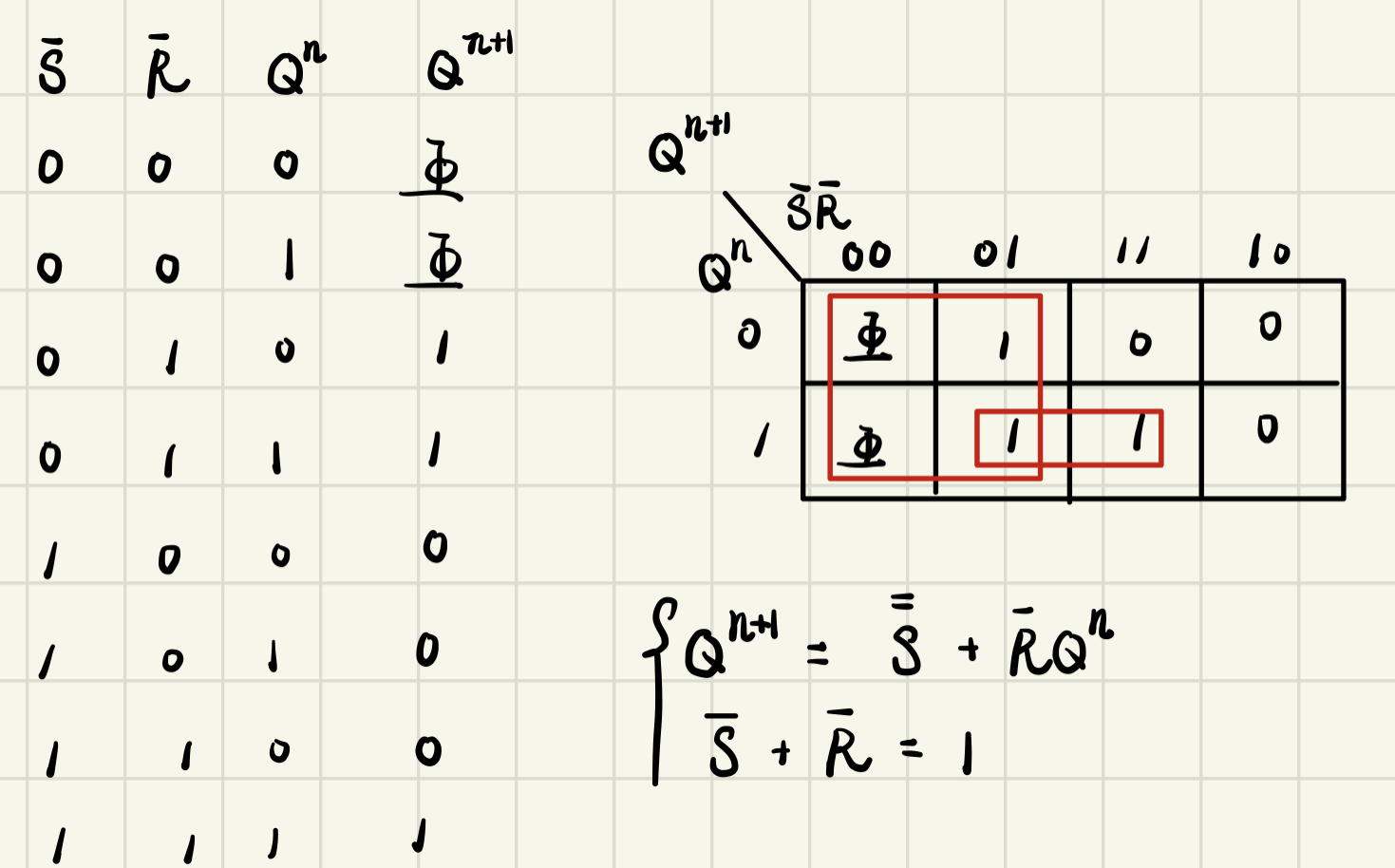

与非门构成的RS-FF

输入是低有效的,所以说当输入0的时候,对应输入端的功能生效。

其特征方程,或者说状态方程,也就是状态与输入的关系可以通过真值表求出。

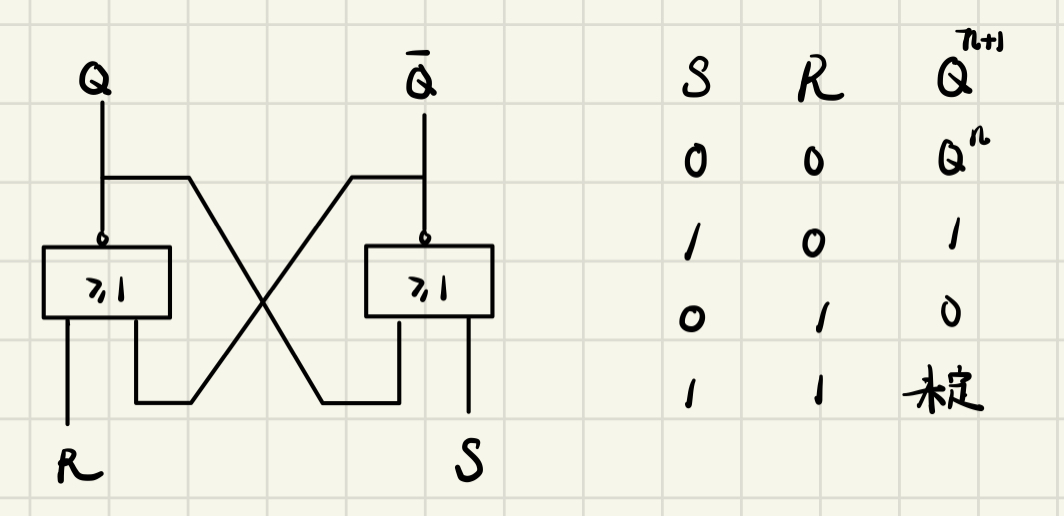

或非门构成的RS-FF

R和S与Q的对应关系交叉了。同时变为了高有效。但是彼此之间的作用还是没变的。

同步FF/时钟FF

同步FF只有在同步信号到达时才按输入信号改变状态。

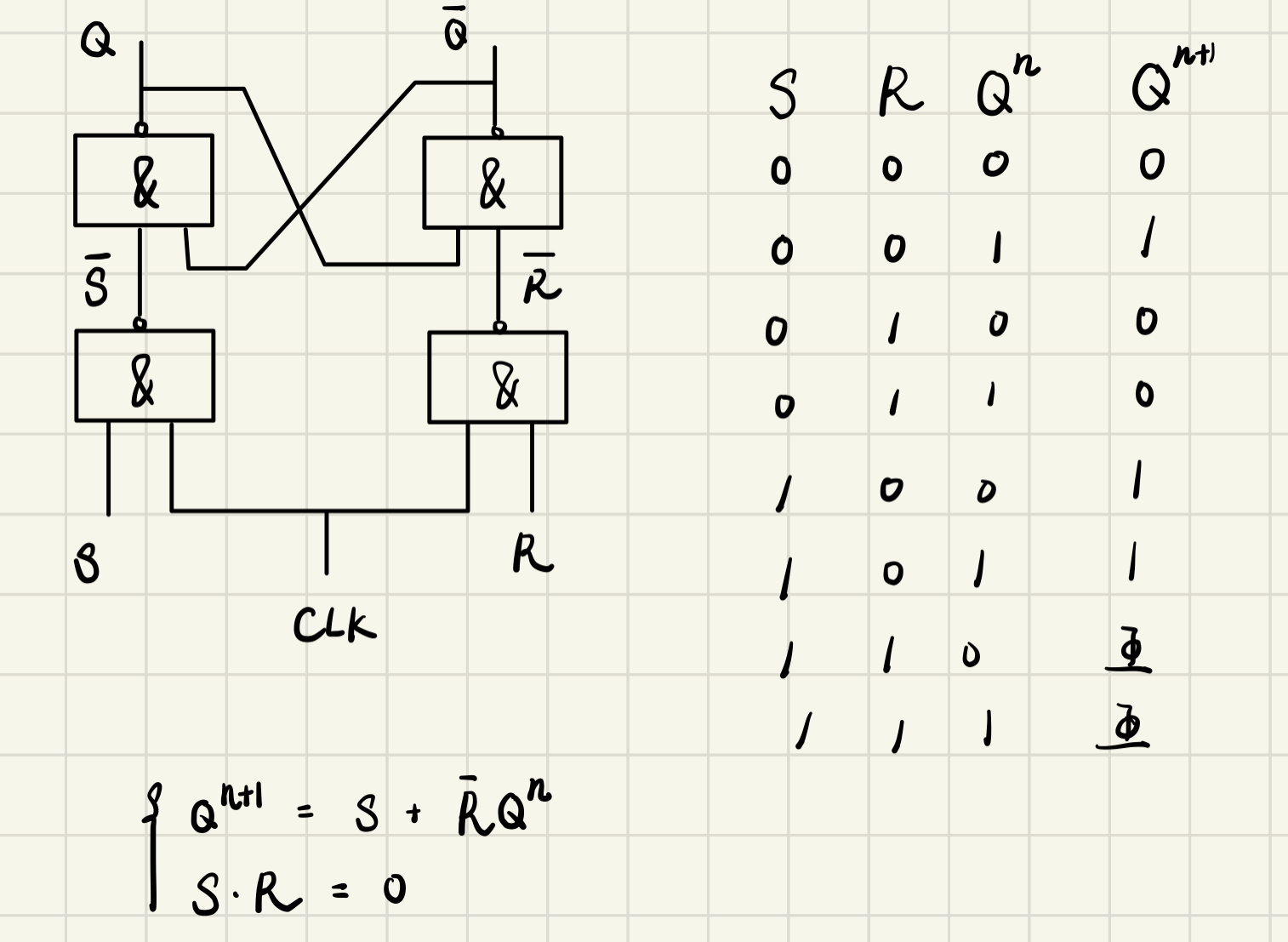

同步RS-FF

采用与非门构成的RS-FF。

时钟RS-FF的缺点在于存在不确定状态。

在CLK=1时,同步RS-FF存在四个状态,当CLK=0时,相当于保持。

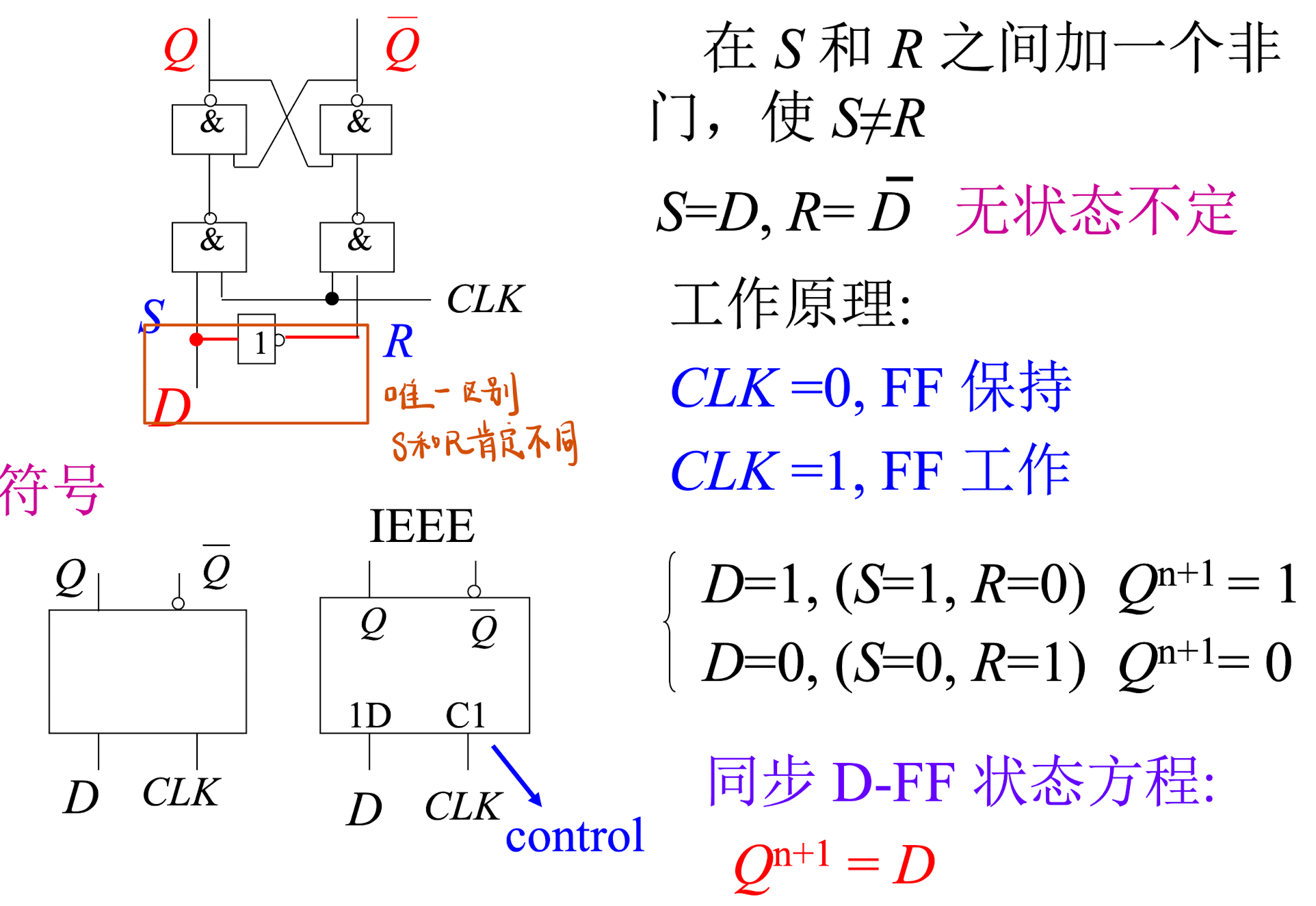

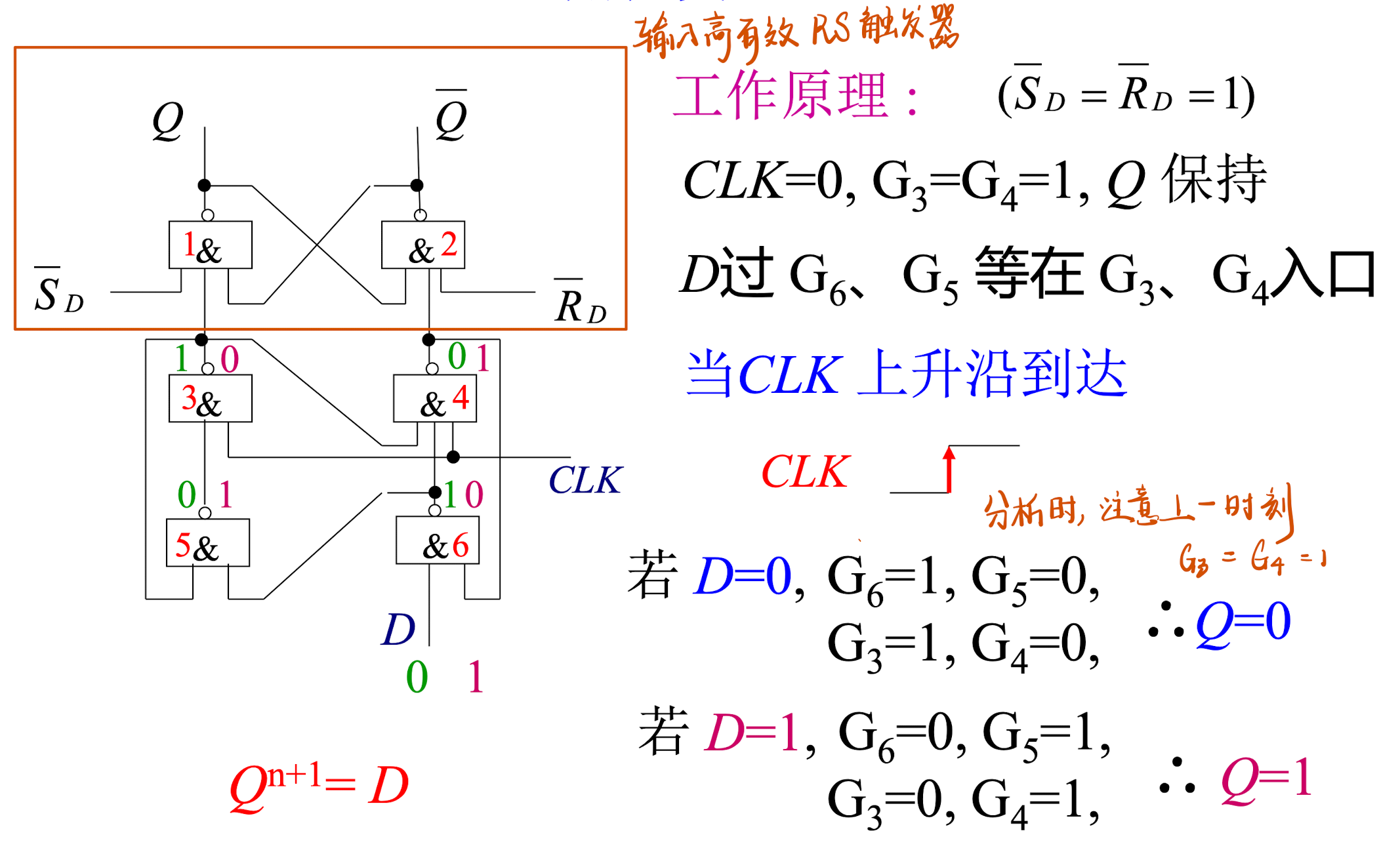

同步D-FF

也就是说,同步D-FF只存在不同的输入,不存在相同的输入,而状态的保持通过CLK来控制。

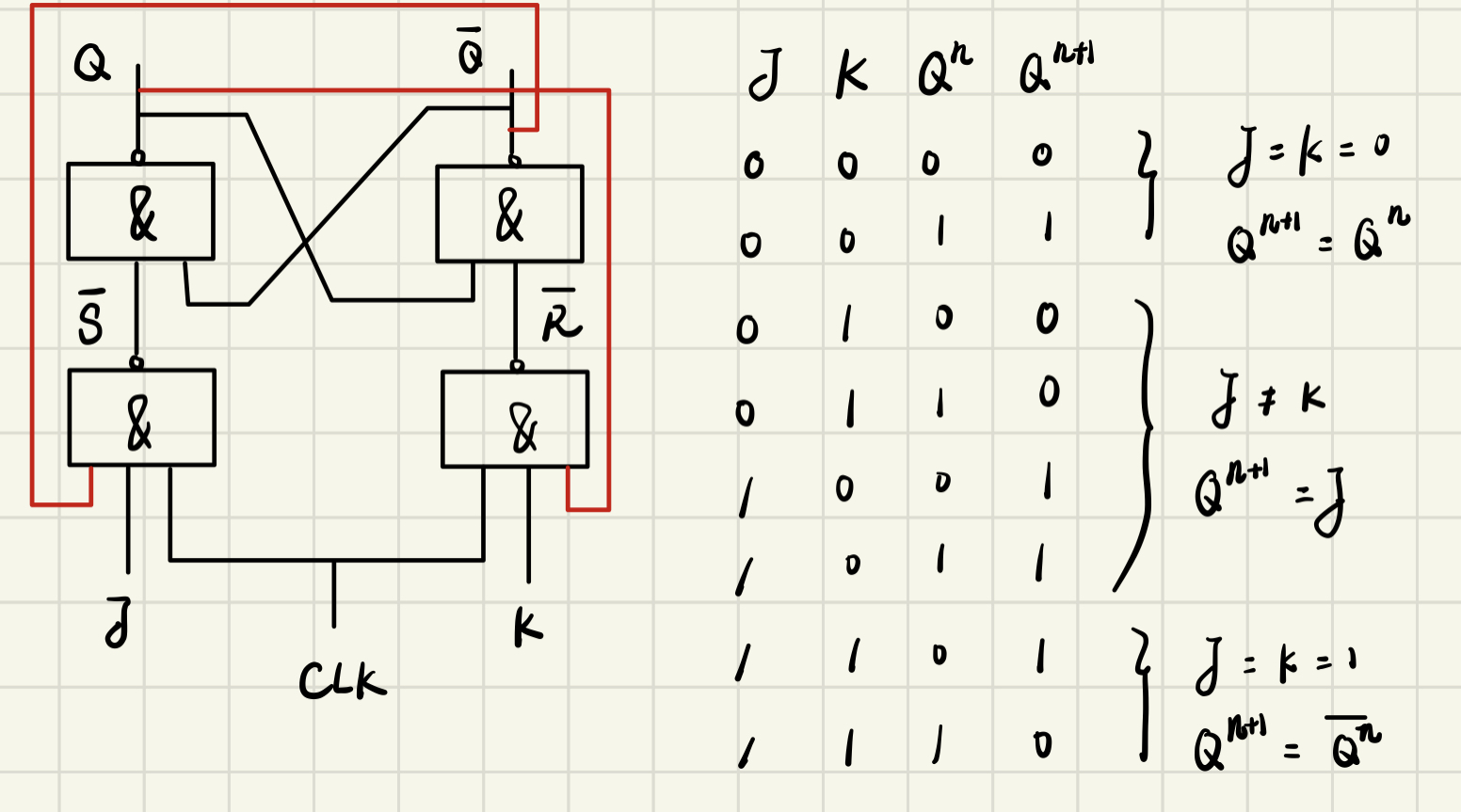

同步JK-FF

S

=

J

Q

ˉ

n

,

R

=

K

Q

n

S=Jbar{Q}^n,R=KQ^n

S=JQˉn,R=KQn

于是,根据同步RS-FF,有

Q

n

+

1

=

S

+

R

ˉ

Q

n

=

J

Q

n

ˉ

+

K

ˉ

Q

n

Q^{n+1}=S+bar{R}Q^n=Jbar{Q^n}+bar{K}Q^n

Qn+1=S+RˉQn=JQnˉ+KˉQn

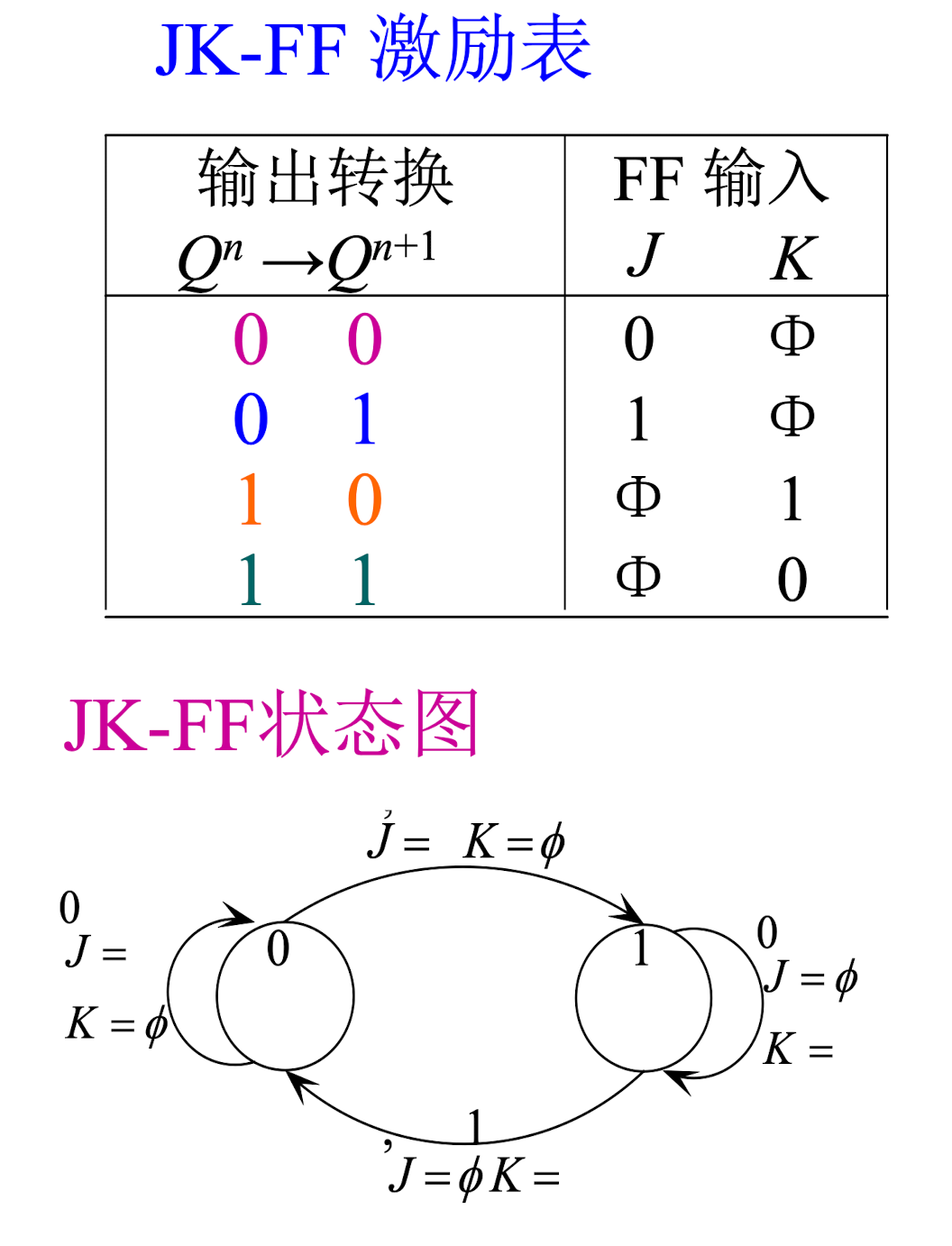

激励表描述了状态发生变化时,输入是什么,等价于状态图。

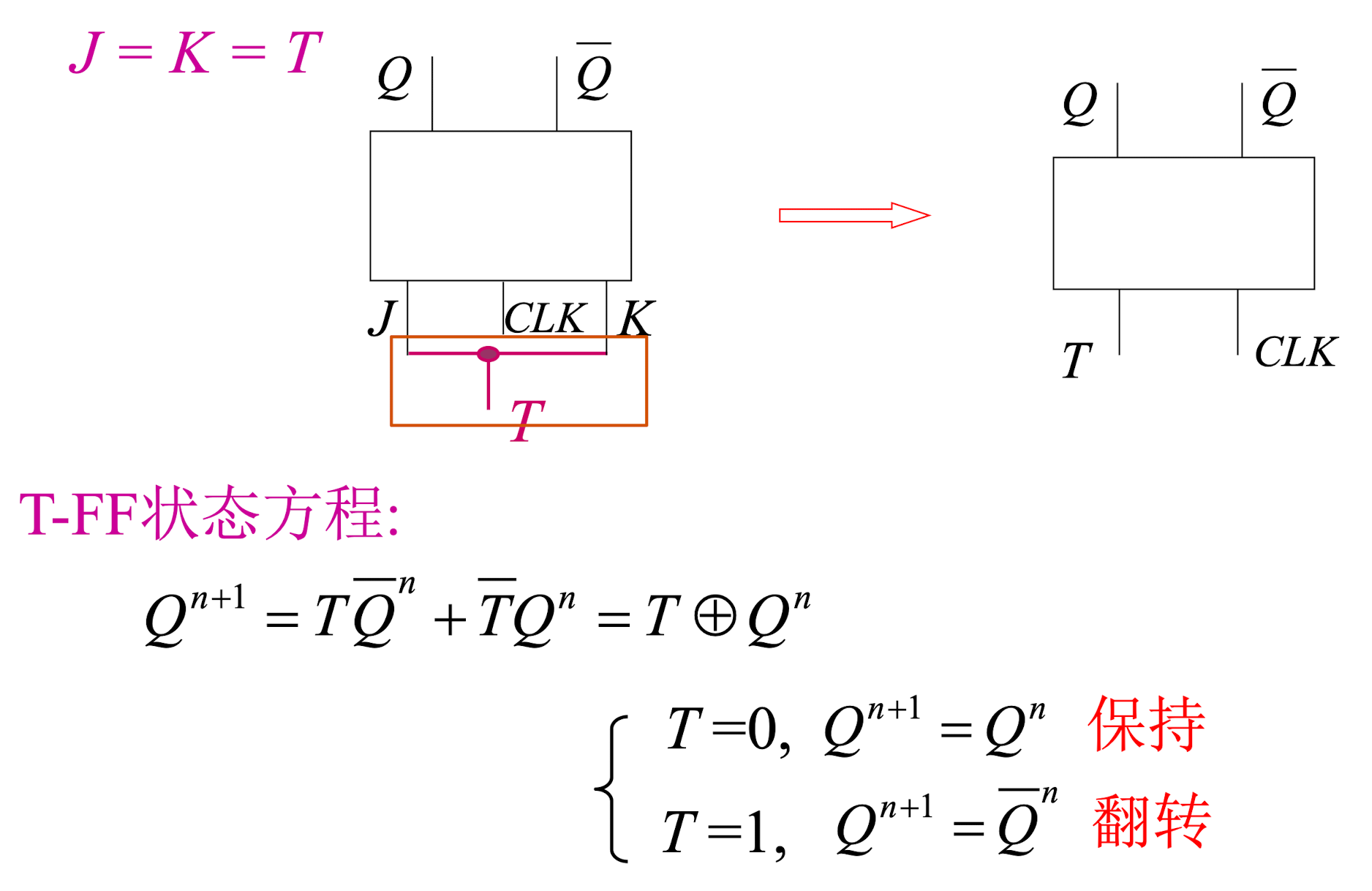

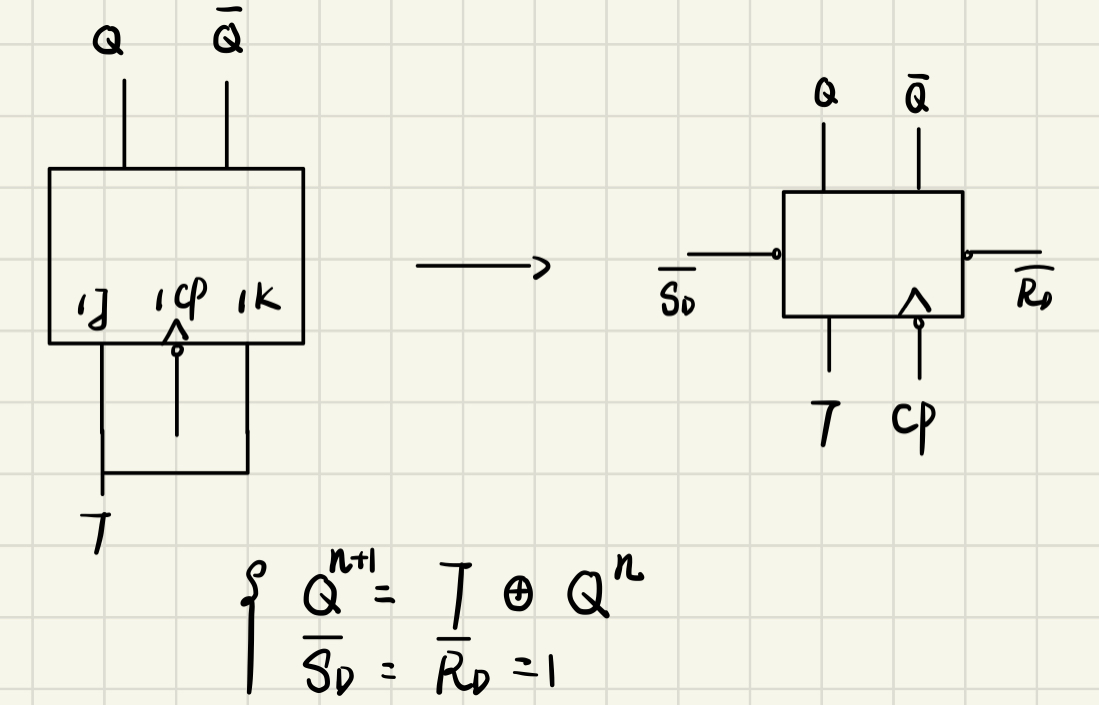

同步T-FF

将JK触发器的J和K相连,转化为T输入。

同步触发器的缺点

在CLK=1期间,FF处于触发状态,

Q

n

+

1

Q^{n+1}

Qn+1随着输入信号

R

,

S

,

D

,

J

,

K

,

T

R,S,D,J,K,T

R,S,D,J,K,T的变化而变化,出现

空翻现象:一个CLK周期内,

Q

Q

Q端只能变化一次,变化一次以上称为触发器的空翻。

就是说,只要时钟信号为1,输出会受到毛刺影响,一直在改变。

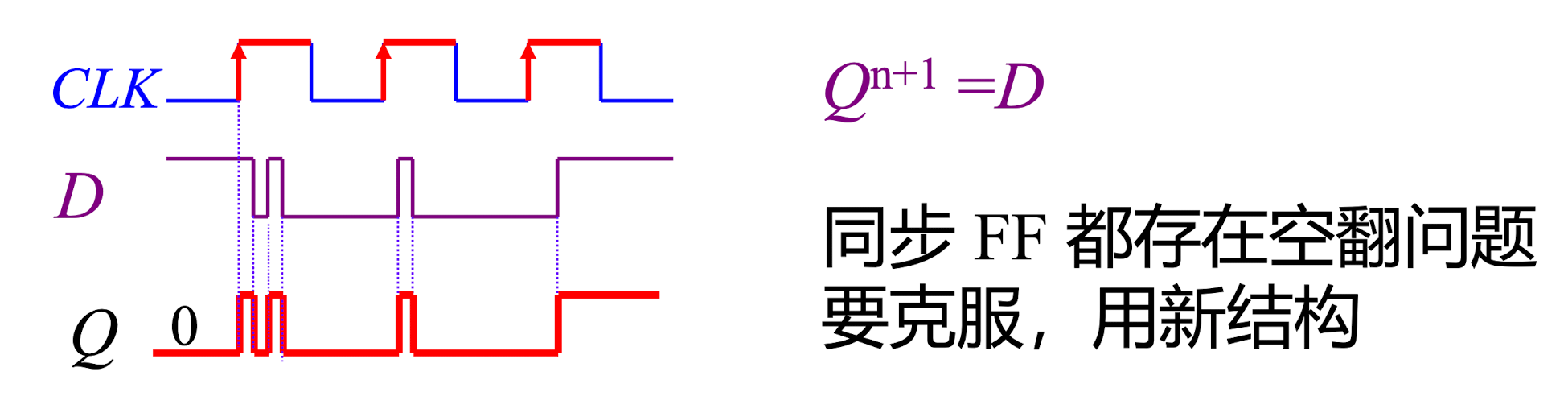

主从触发器

为了避免空翻,只要让输出的改变只取决于一个时刻即可,这也是主从触发器的思想。

主从触发器分为主触发器和从触发器,前者在CLK=1时工作,后者在CLK=0时工作,由于输入是从主触发器传入,所以显得输出是在下降沿触发。

主从RS-FF

主从SR-FF的结构就是两个同步SR-FF结合在一起,但分别输入两个相反的时钟信号。

其符号也与同步RS-FF相似,只是上面的符号变了。

特征方程为

Q

n

+

1

=

S

+

R

ˉ

Q

n

Q^{n+1}=S+bar{R}Q^n

Qn+1=S+RˉQn

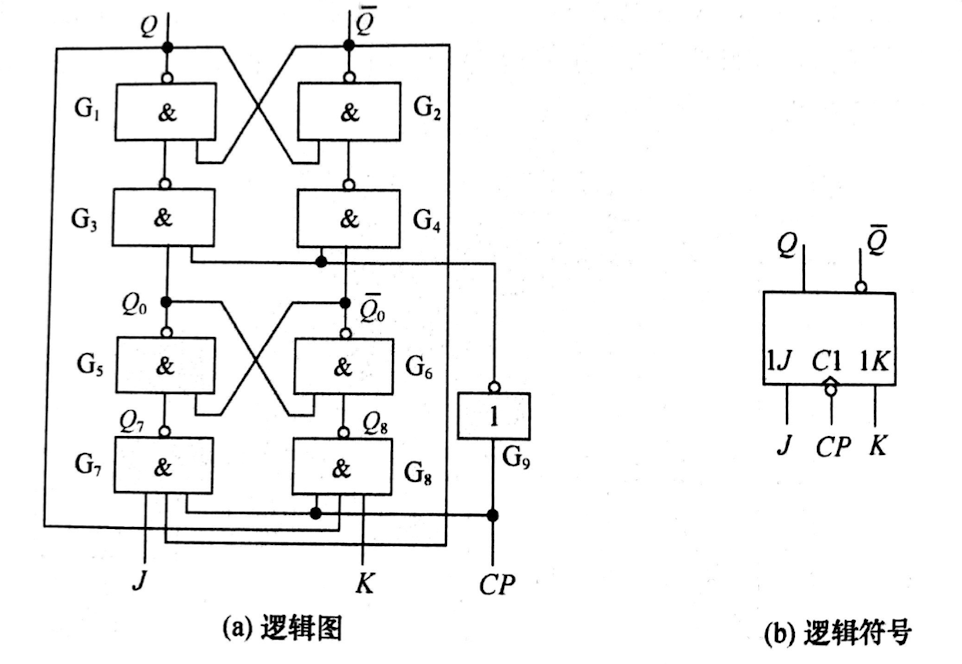

主从JK-FF

输出在主触发器的输入处交叉。

特征方程为 Q n + 1 = S Q ˉ n + K ˉ Q n Q^{n+1}=Sbar{Q}^n+bar{K}Q^n Qn+1=SQˉn+KˉQn

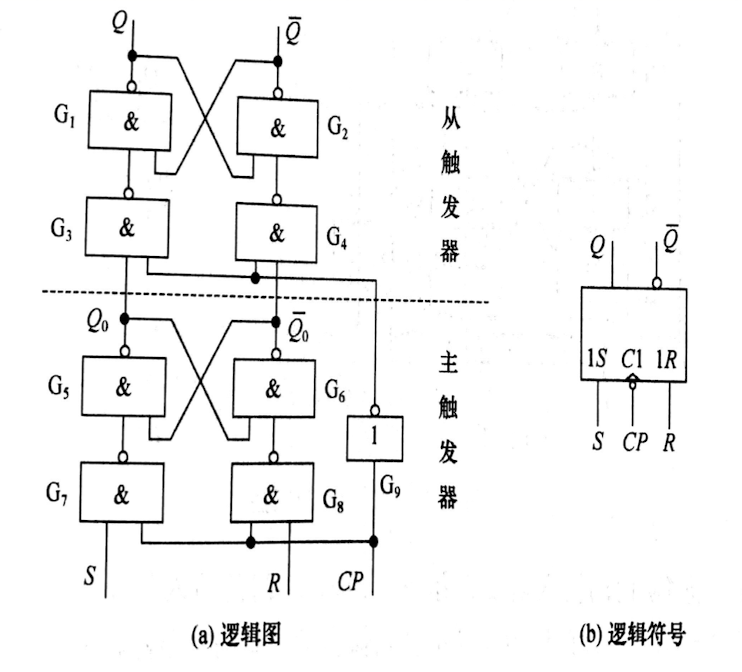

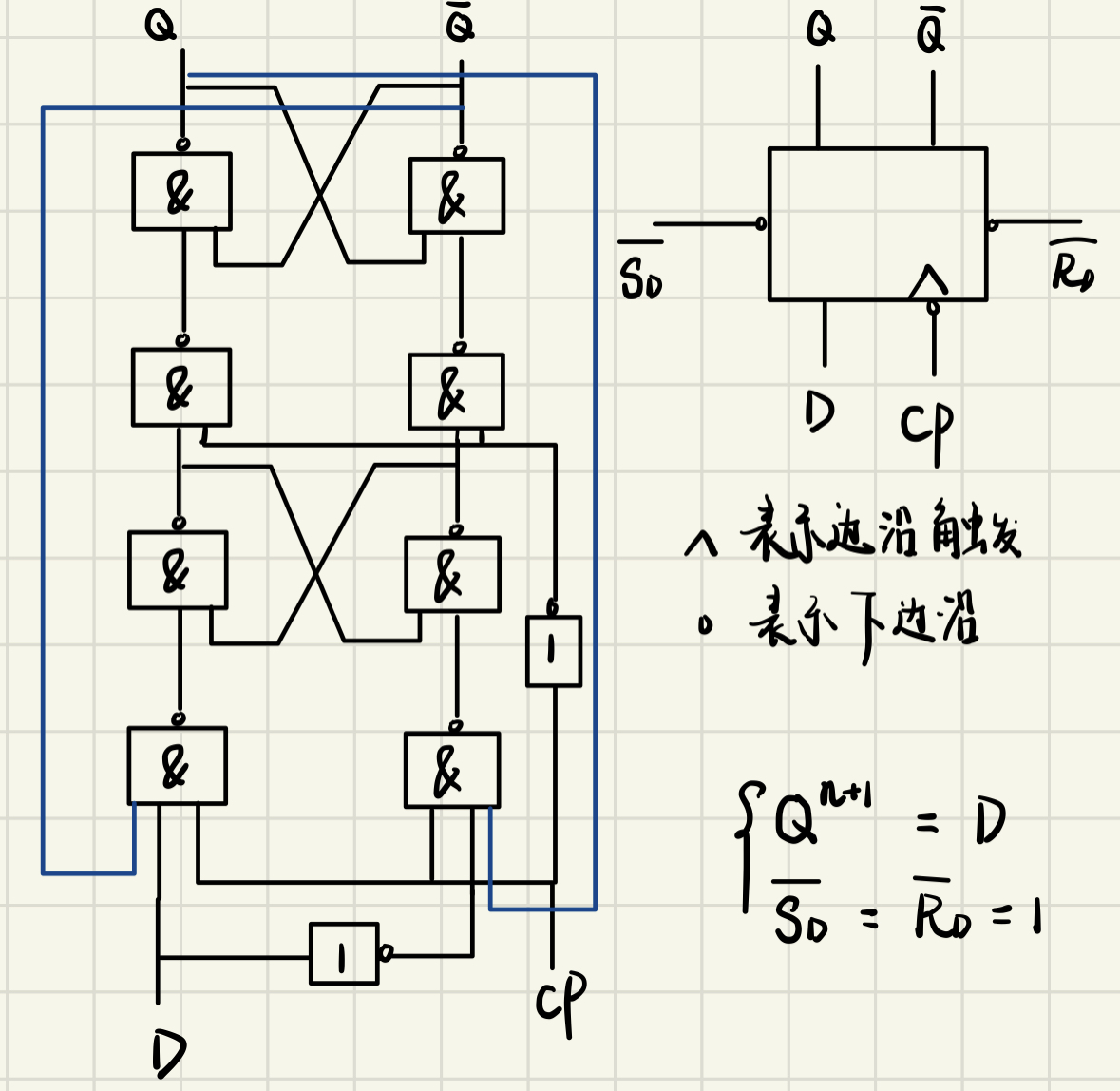

主从D-FF

R ˉ D , R ˉ D bar{R}_D,bar{R}_D RˉD,RˉD分别代表着直接置位端和直接复位端,有着最高的优先级。

主从D-FF是主从JK-FF衍生而来。

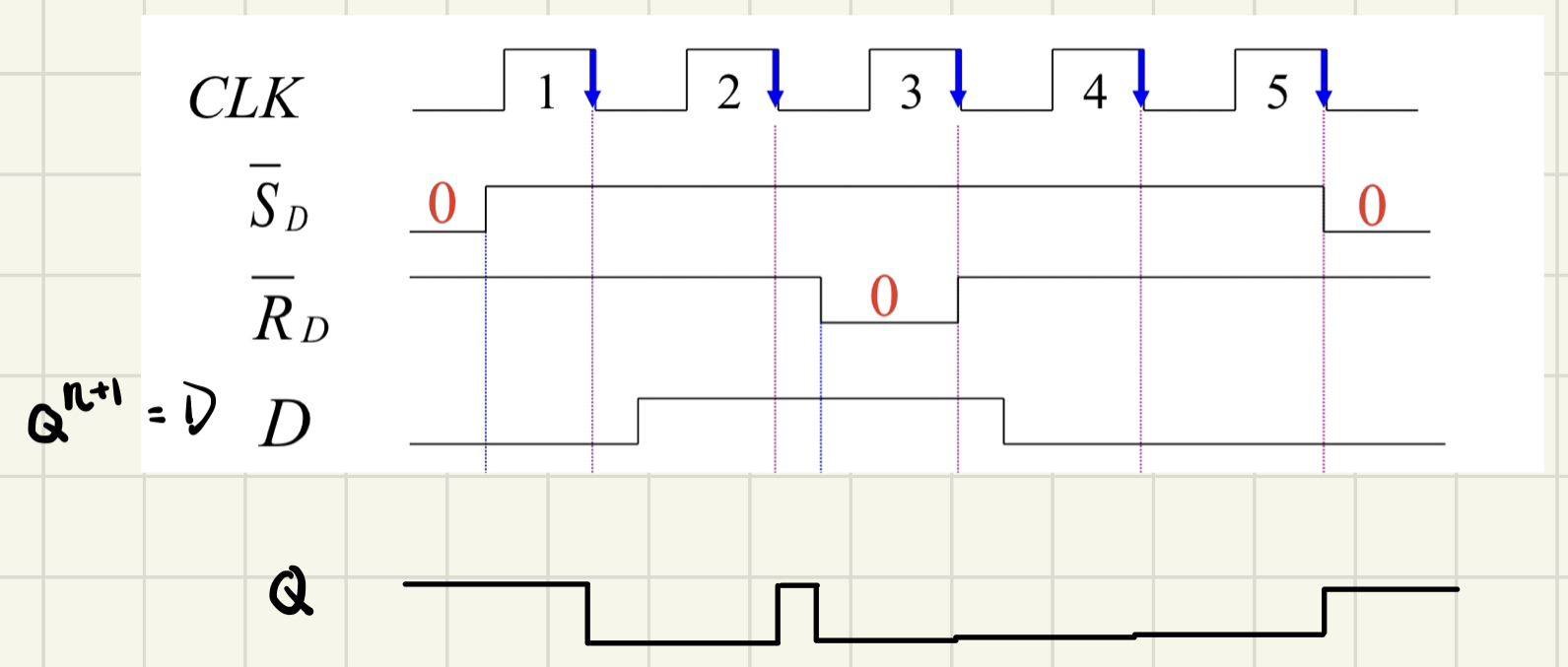

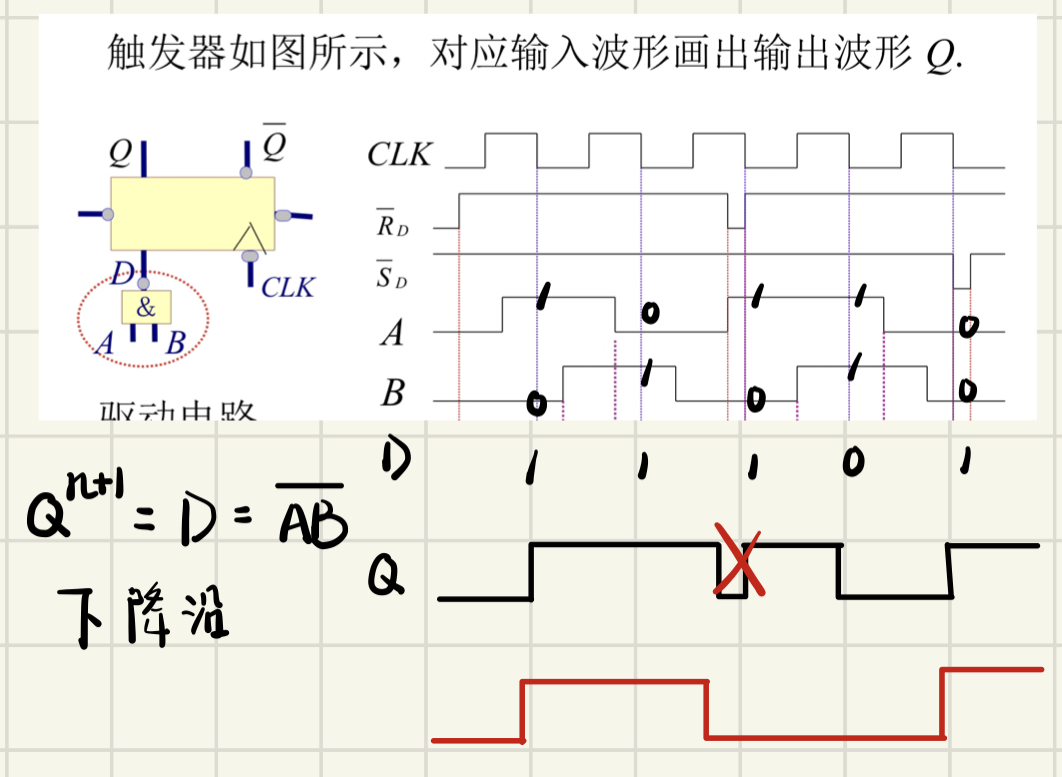

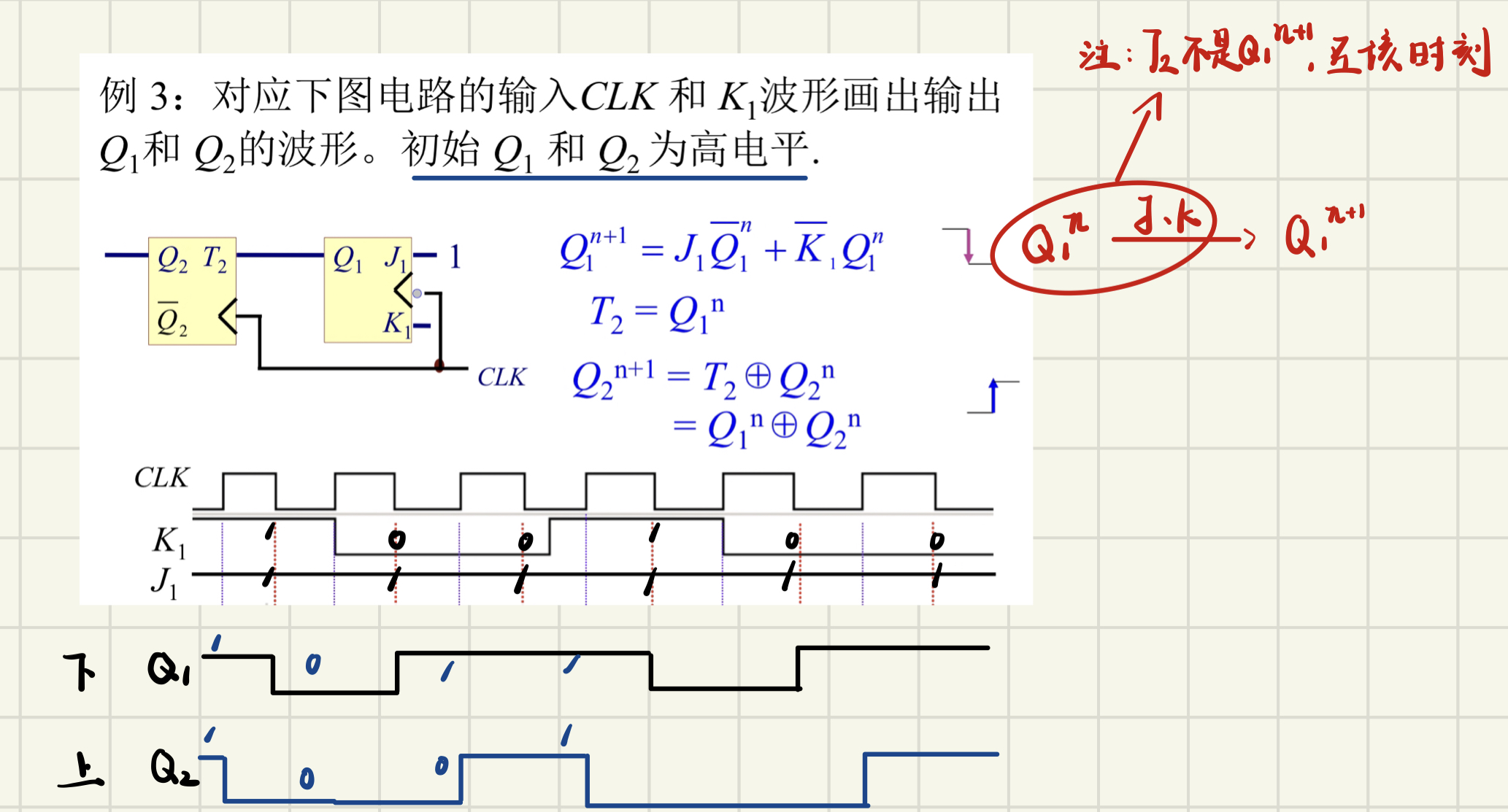

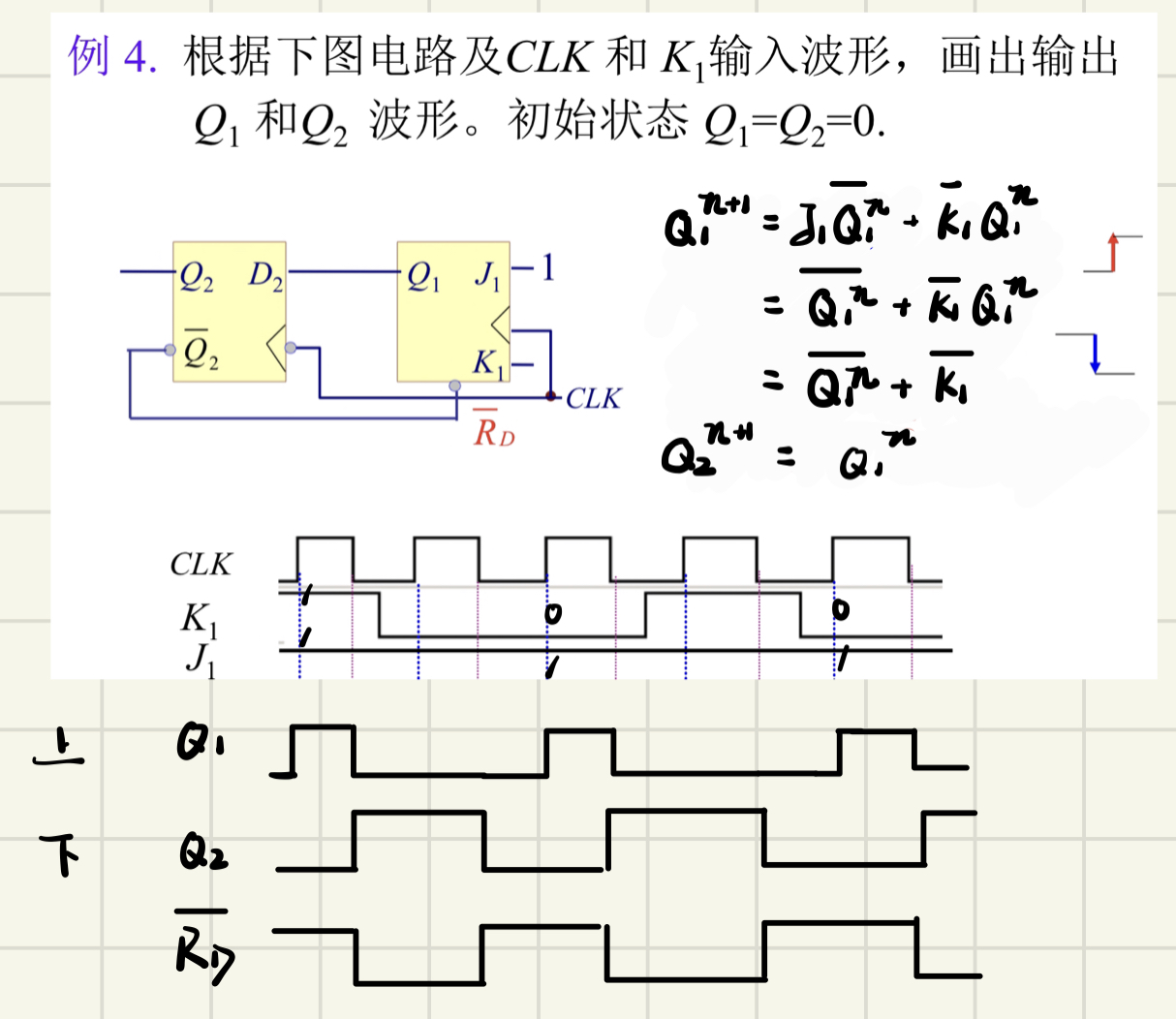

题型十:根据输入曲线画输出曲线

画主从触发器曲线的核心要义是只关注下降沿前一时刻的信号。

一般不考虑一次变化现象。

对于画图来说,正边沿触发也好,负边沿触发也好,只用在乎前一瞬间的状态即可,不用管缺点。

前一瞬间的D是1,但是前一瞬间的复位端是0啊!。

- 明确输入;

- 有必要的话画出输入波形;

- D、JK、T都直接按公式画就行。

后者对前者有影响,于是走一段画一段;

首先确定是上升沿还是下降沿。

在边沿处,关注:

- 输入

- 复位端、置位端。

在边沿内,关注:复位端、置位端。

主从T-FF

主从触发器的问题

CLK=1期间,输入信号(J、K、T)不允许变化,否则会出现"一次变化"现象,使得FF输出状态不能反映CLK在下降沿瞬间,J、K端的状态,破坏了逻辑关系。(J和K总计只变化一次的话其实没影响,但还是不允许变化)

所以说,主从FF只适用于在CLK信号很窄的情况。

这个问题的意思就是,JK-FF和T-FF的特征方程可知,该时刻(第 n + 1 n+1 n+1个下降沿)的状态和上一时刻(第 n n n个下降沿)的状态有关,但是吧,在CLK=1期间,状态发生变化的话,这个 Q n Q^n Qn就可能不能再是第 n n n个下降沿时的状态了。

正边沿触发器

主从触发器出现一次变化现象的本质原因,还是因为在存入状态(CLK=1)时,有毛刺,输入对状态造成多次影响,存了好几次状态,导致锁住的状态和当时的输入对不上号。所以说,接下来的解决方案都是迫使输入只能存一次状态。

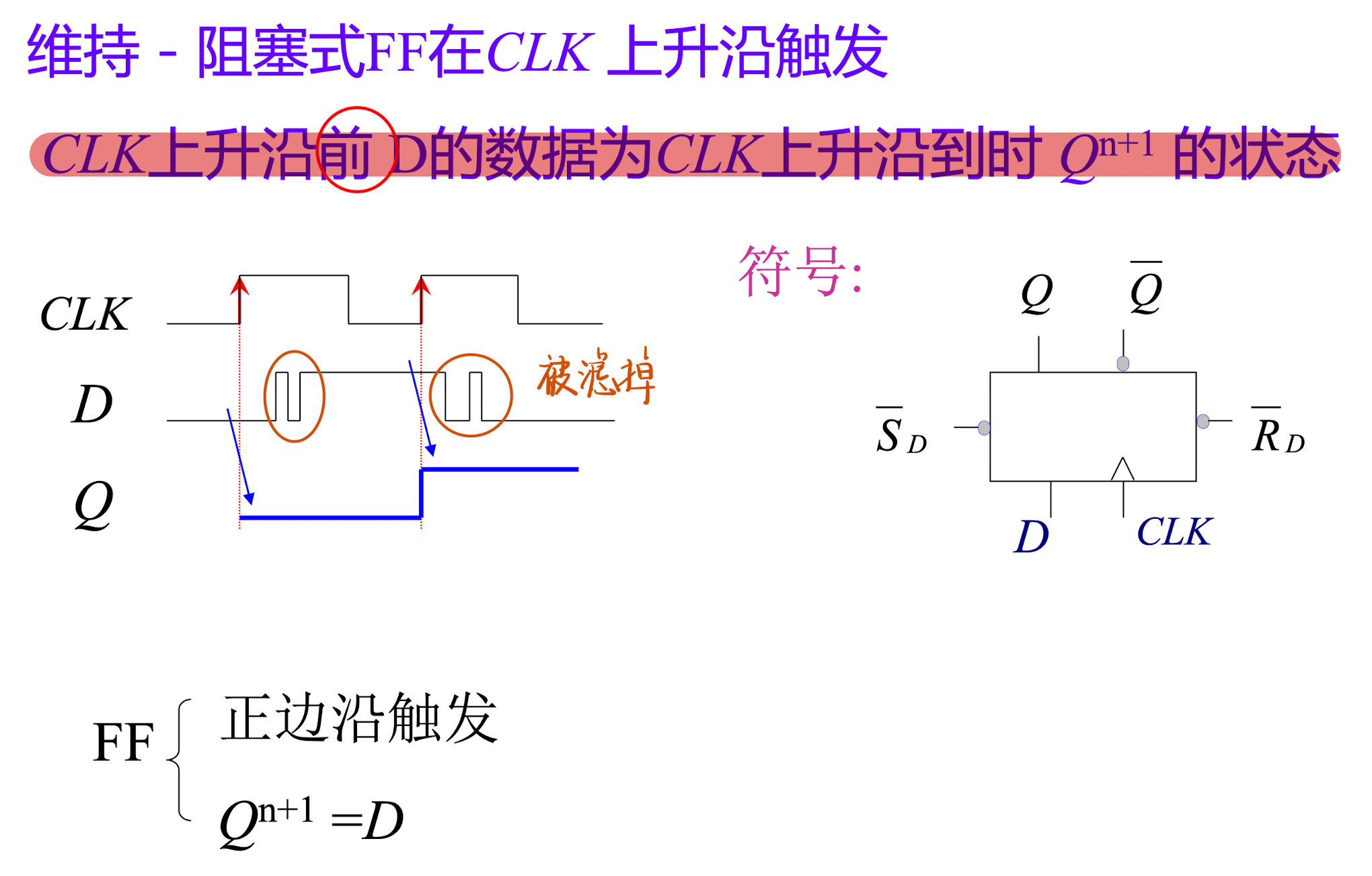

正边沿触发D-FF(维持阻塞D-FF)

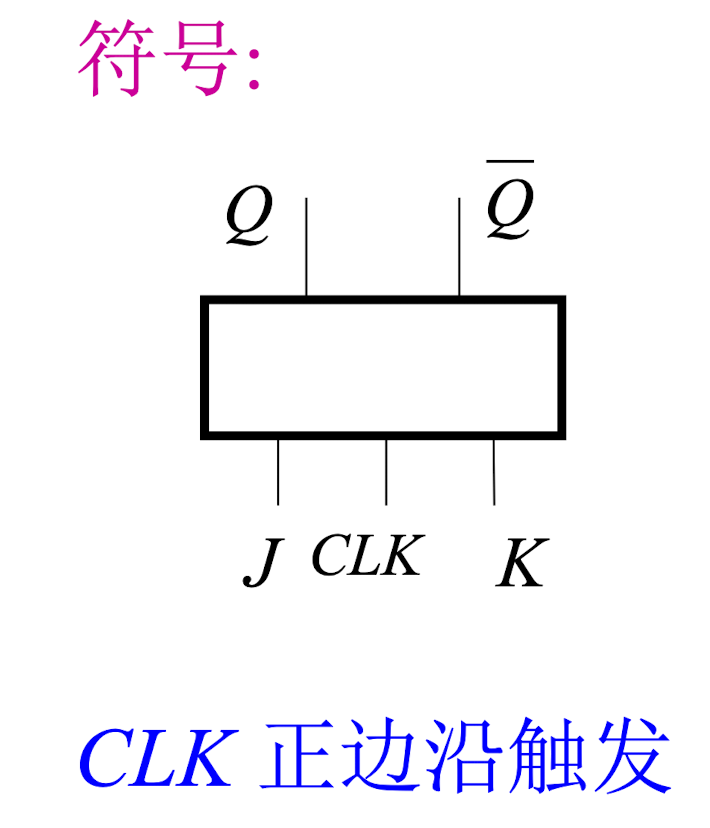

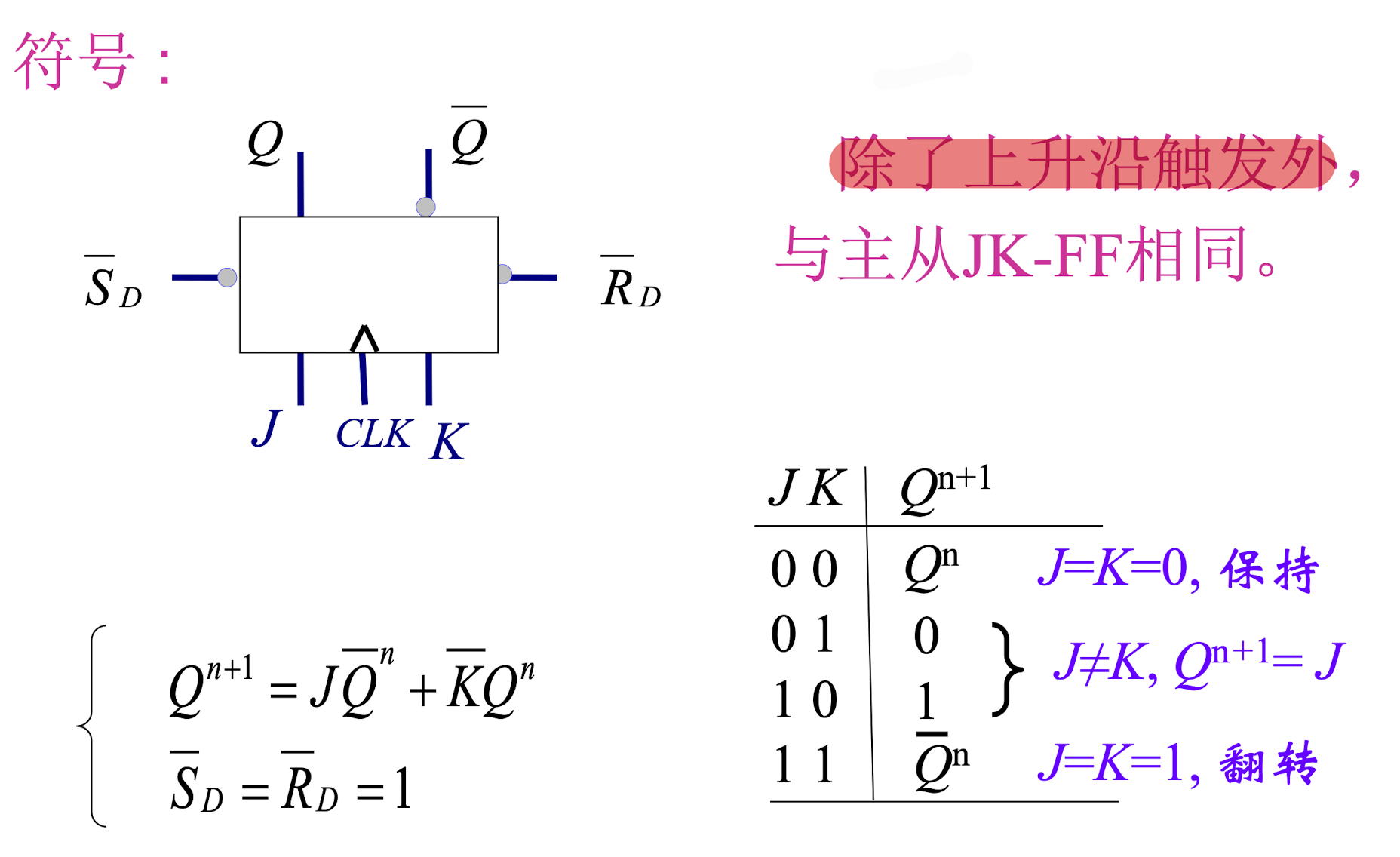

正边沿触发JK-FF

具体结构可以不联想主从JK-FF,只要记住它是正边沿触发的,且不存在空翻即可。

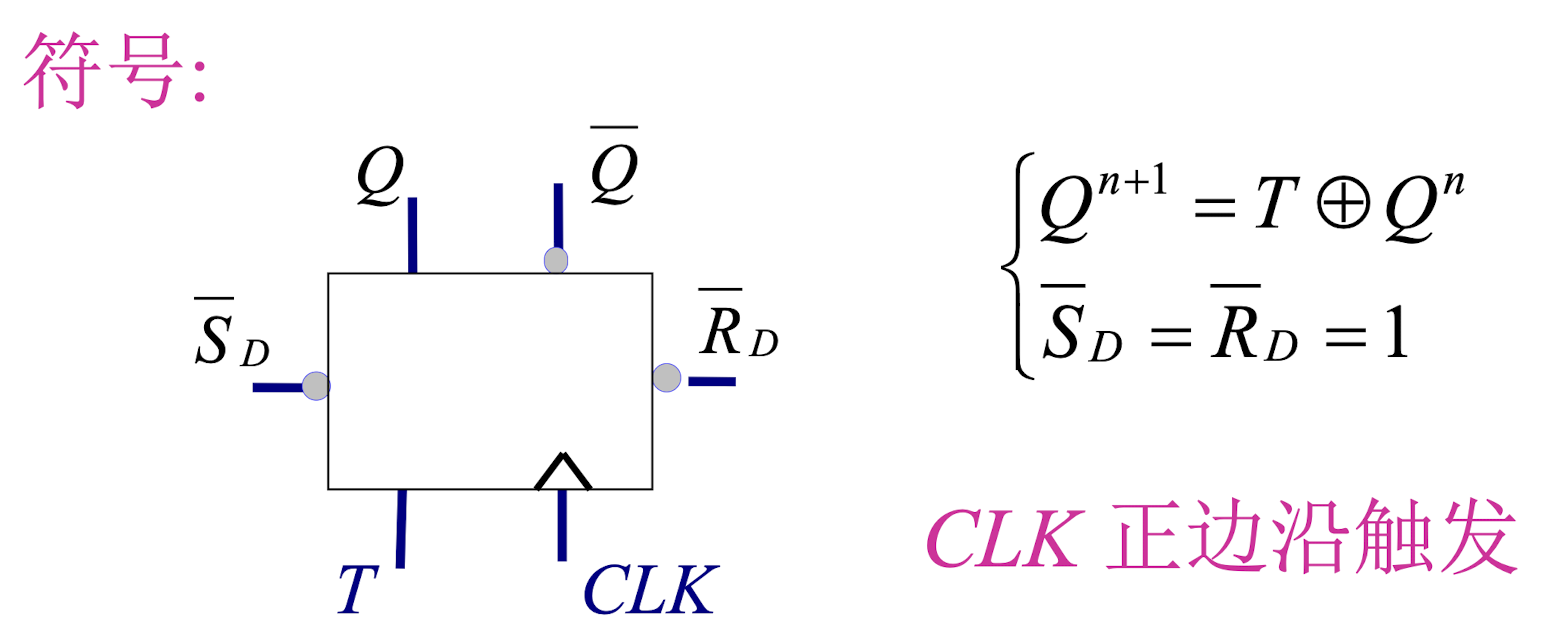

正边沿触发T-FF

触发器的应用

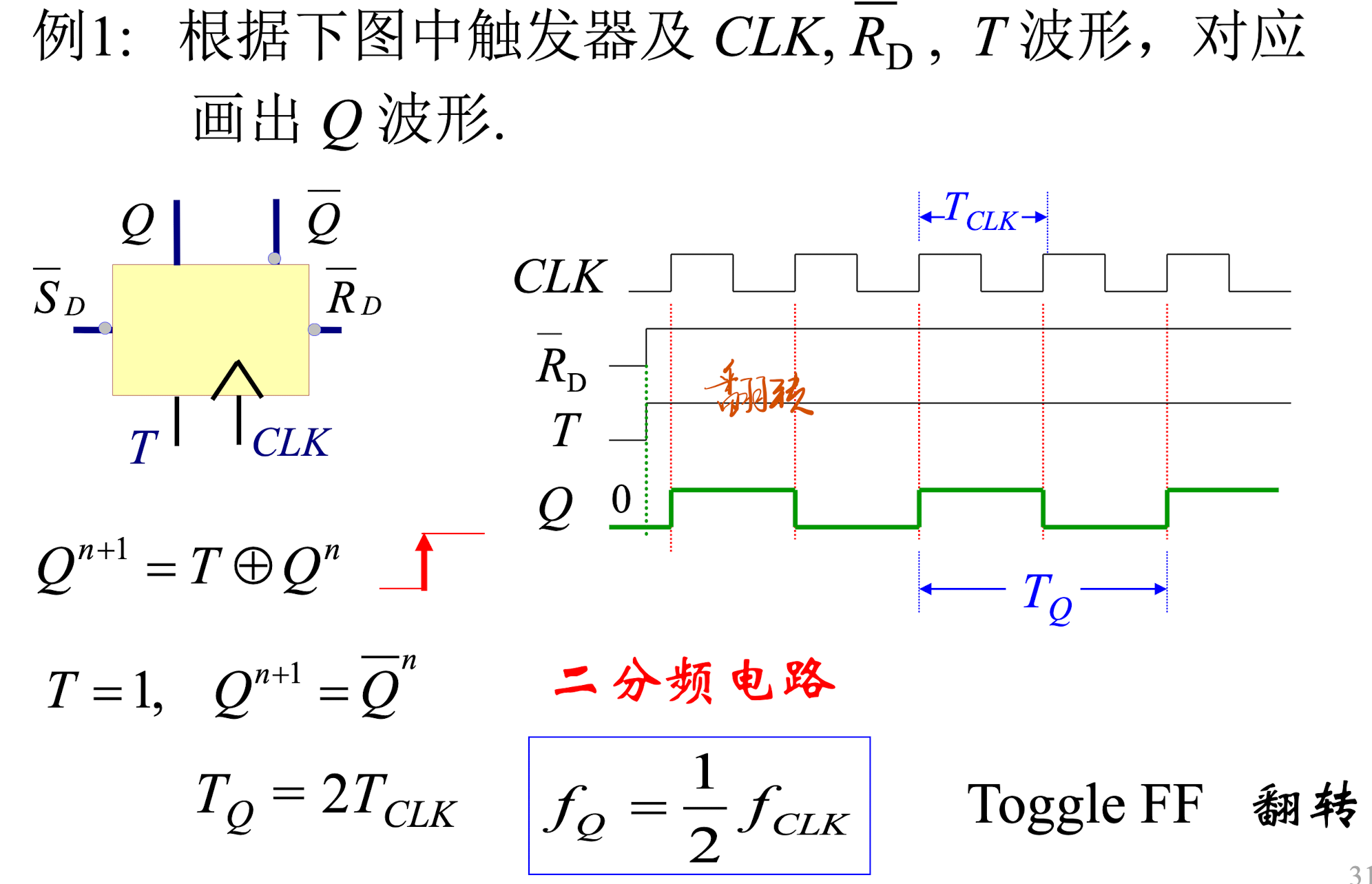

分频电路

正边沿T触发器与时钟信号可以组建起二分频电路。

因为只在正边沿时触发一次,所以说,周期变为了原来的两倍。

消除噪声电路

当一个开关闭合时,在开关完全闭合之前的几毫秒时间内,有时会发生金属接触点之间的碰撞和跳动,然后逻辑在0、1之间疯狂切换。

可以使用基本RS-FF,开关闭合时,输入为01,输出为高电平,跳开时,输出为11,保持。

触发器的分类

按工作状态分:

- 双稳态触发器;

- 单稳态触发器;

- 无稳态触发器。

按结构分:

- 基本RS触发器;

- 同步触发器;

- 主从触发器;

- 边沿触发器。

按逻辑功能分:

- RS触发器;

- JK触发器;

- D触发器;

- T和T‘触发器

最后

以上就是朴素煎蛋最近收集整理的关于数电_第五章_触发器基本RS-FF同步FF/时钟FF主从触发器正边沿触发器触发器的应用触发器的分类的全部内容,更多相关数电_第五章_触发器基本RS-FF同步FF/时钟FF主从触发器正边沿触发器触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复