我是靠谱客的博主 愤怒小虾米,这篇文章主要介绍Verilog语法基础HDL Bits训练11:CountersCircuits:Sequential Logic:Counters,现在分享给大家,希望可以做个参考。

文章目录

- Circuits:Sequential Logic:Counters

- 一、Four-bit binary counter

- 二、Decade counter

- 三、Decade counter again

- 四、Slow decade counte

- 五、Counter 1-12

- 六、Counter 1000

- 七、4-digit decimal counter

- 八、12-hour clock

Circuits:Sequential Logic:Counters

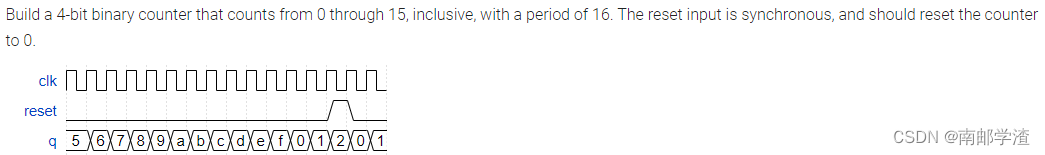

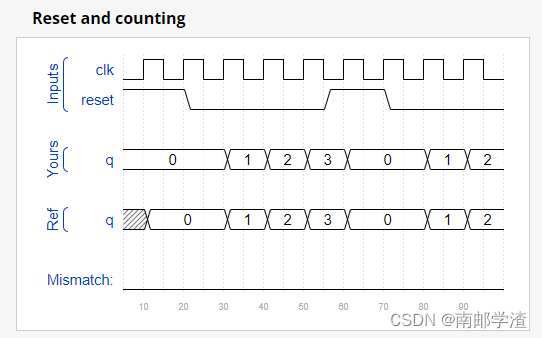

一、Four-bit binary counter

设计一个四位的计数器,从0计数到15,并且有同步复位。

- RTL代码

module top_module (

input clk,

input reset,

// Synchronous active-high reset

output reg[3:0] q);

always @(posedge clk)

if(reset)

q <= 1'b0;

else if(q == 4'd15)

q <= 1'b0;

else

q <= q + 1'b1;

endmodule

- 仿真波形图

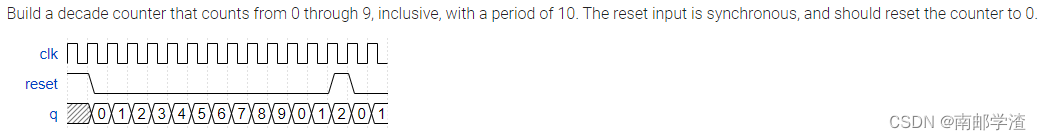

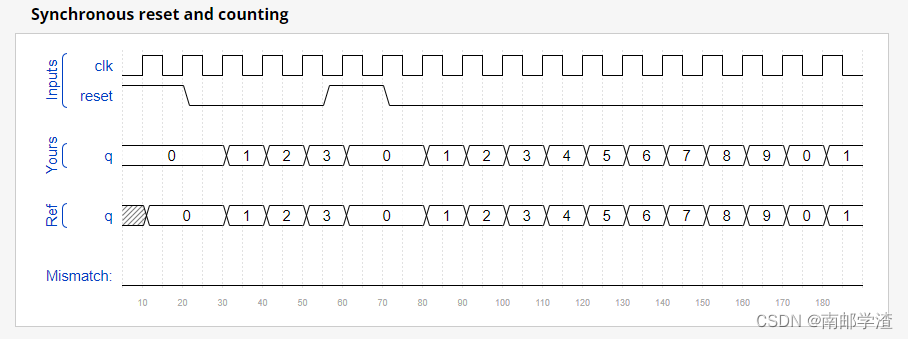

二、Decade counter

设计一个计数值为10的十进制计数器,从0计数到9,并且有同步复位

- RTL代码

module top_module (

input clk,

input reset,

// Synchronous active-high reset

output [3:0] q);

always @(posedge clk)

if(reset)

q <= 1'b0;

else if(q == 4'd9)

q <= 1'b0;

else

q <= q + 1'b1;

endmodule

- 仿真波形图

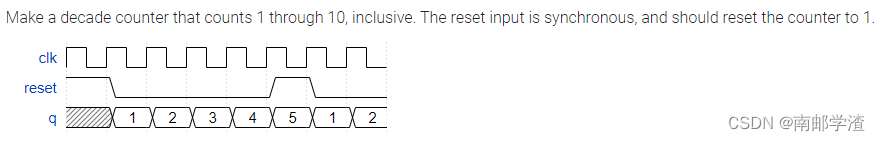

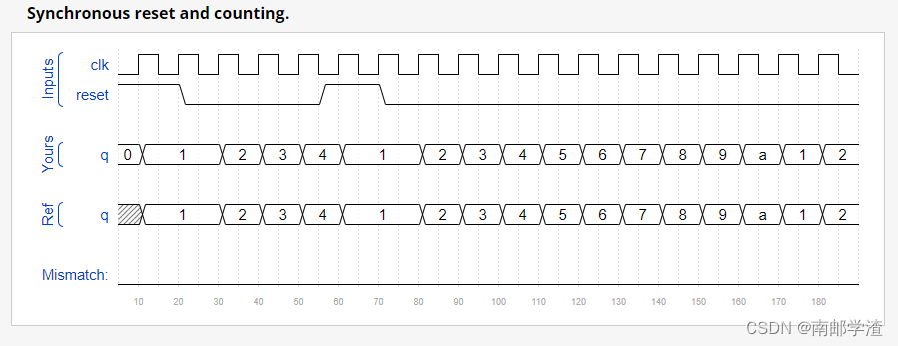

三、Decade counter again

设计一个计数值为10的十进制计数器,计数值从1到10,且有同步复位

- RTL代码

module top_module (

input clk,

input reset,

output [3:0] q);

always @(posedge clk)

if(reset)

q <= 1'b1;

else if(q == 4'd10)

q <= 1'b1;

else

q <= q + 1'b1;

endmodule

- 仿真波形图

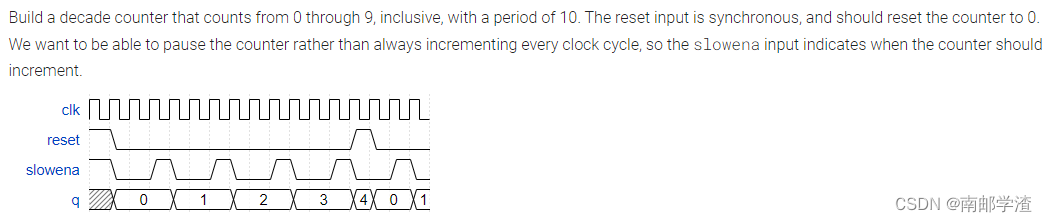

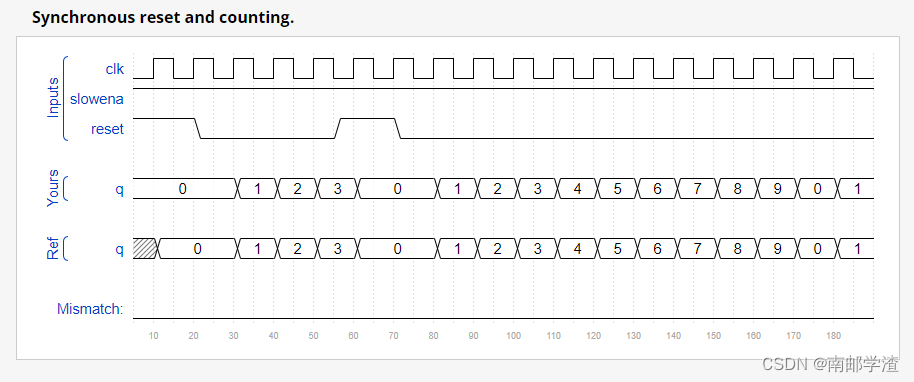

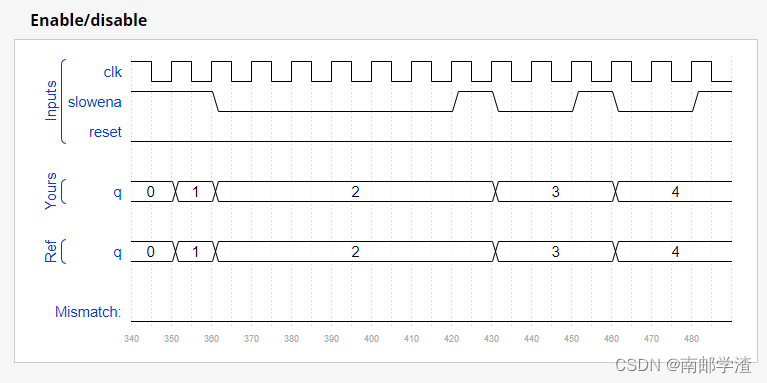

四、Slow decade counte

设计一个缓慢的计数值为10的从0到9的十进制计数器,要求在slowena信号为高电平的时候计数值进行计数,否则保持原来的计数状态。

- RTL代码

module top_module (

input clk,

input slowena,

input reset,

output [3:0] q);

always @(posedge clk)

if(reset)

q <= 1'b0;

else if(q == 4'd9 && slowena)

q <= 1'b0;

else if(slowena)

q <= q + 1'b1;

else

q <= q;

endmodule

- 仿真波形图

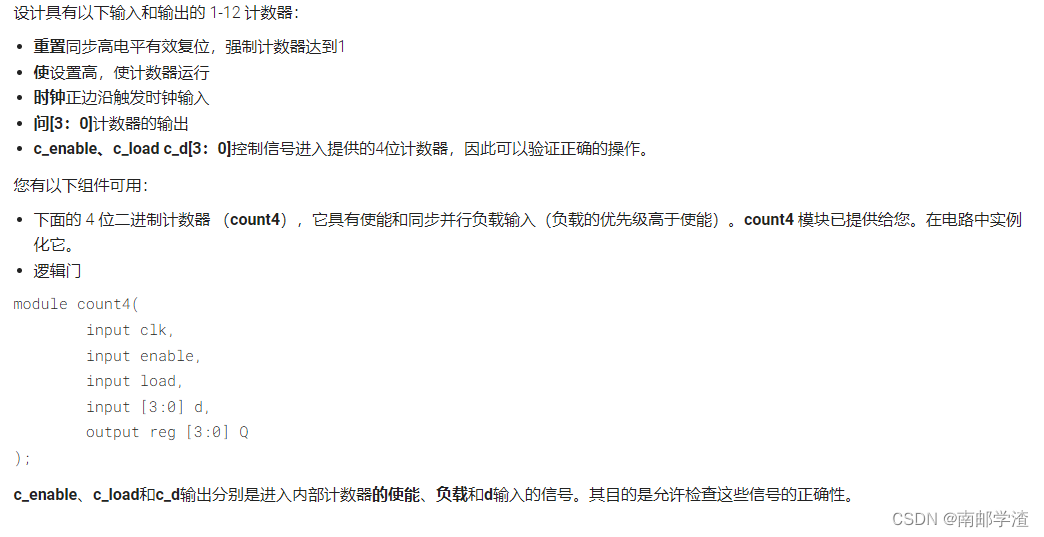

五、Counter 1-12

- RTL代码

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

); //

count4 the_counter (clk, c_enable, c_load, c_d ,Q);

assign c_enable = enable;

assign c_load = ((Q >= 4'd12) && enable) | reset;

assign c_d = c_load? 4'd1:4'd0;

endmodule

- 仿真波形图

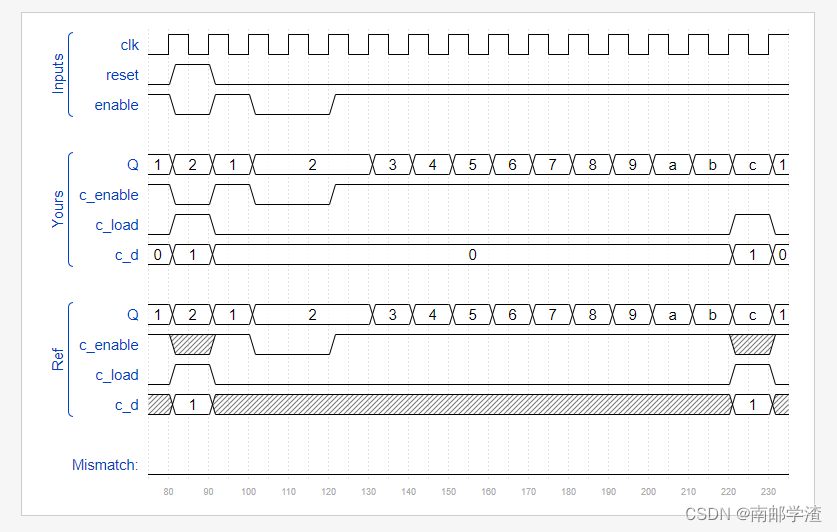

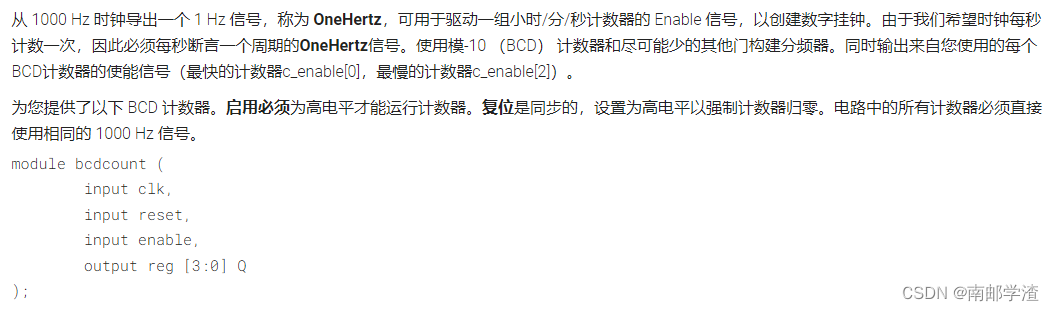

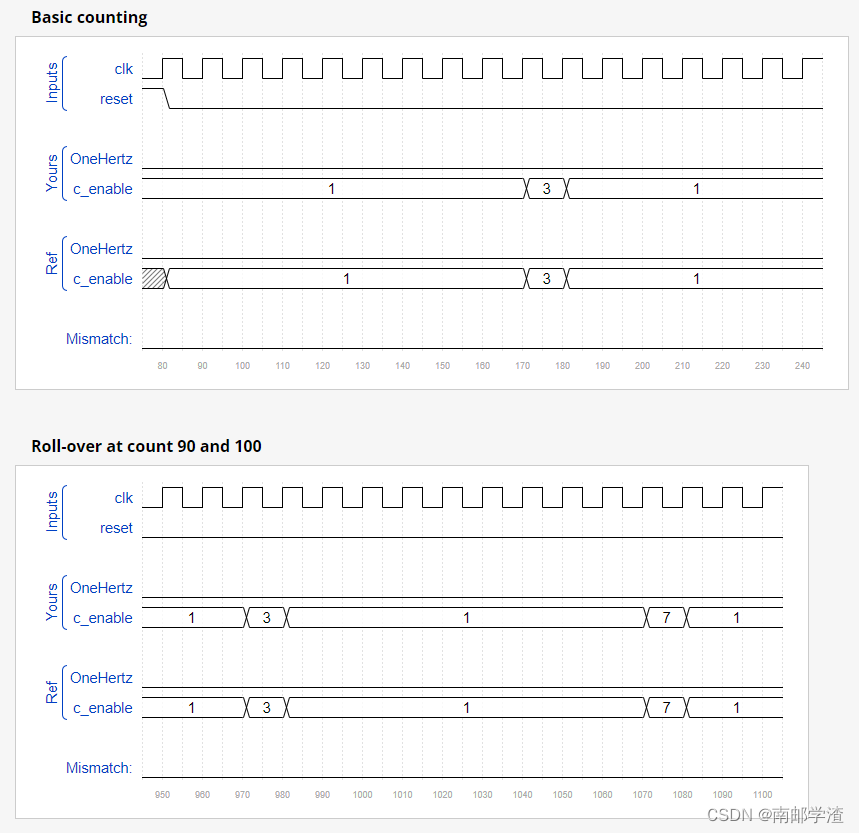

六、Counter 1000

- RTL代码

module top_module (

input clk,

input reset,

output OneHertz,

output [2:0] c_enable

); //

wire [3:0] one,ten,hundred;

assign c_enable = {one == 4'd9&&ten == 4'd9,one == 4'd9,1'b1};

assign OneHertz = one == 4'd9&&ten == 4'd9&&hundred == 4'd9;

bcdcount counter0 (clk, reset, c_enable[0],one);

bcdcount counter1 (clk, reset, c_enable[1],ten);

bcdcount counter2 (clk, reset, c_enable[2],hundred);

endmodule

- 仿真波形图

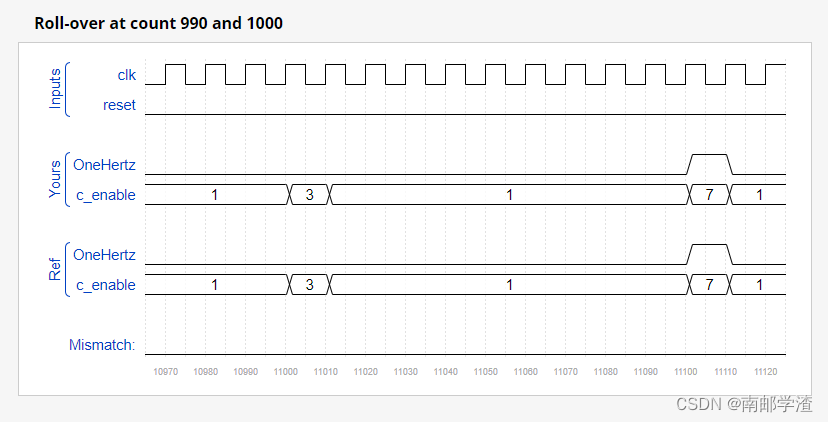

七、4-digit decimal counter

- RTL代码

module top_module (

input clk,

input reset,

// Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

reg [3:0]one;

reg [3:0]ten;

reg [3:0]hundred;

reg [3:0]thousand;

always @(posedge clk)

if(reset)

one <= 1'b0;

else if(one == 4'd9)

one <= 1'b0;

else

one <= one + 1'b1;

always @(posedge clk)

if(reset)

ten <= 1'b0;

else if(ten == 4'd9 && one == 4'd9)

ten <= 1'b0;

else if(one == 4'd9)

ten <= ten + 1'b1;

always @(posedge clk)

if(reset)

hundred <= 1'b0;

else if(hundred == 4'd9 && ten == 4'd9 && one == 4'd9)

hundred <= 1'b0;

else if(ten == 4'd9 && one == 4'd9)

hundred <= hundred + 1'b1;

always @(posedge clk)

if(reset)

thousand <= 1'b0;

else if(thousand == 4'd9 && hundred == 4'd9 && ten == 4'd9 && one == 4'd9)

thousand <= 1'b0;

else if(hundred == 4'd9 && ten == 4'd9 && one == 4'd9)

thousand <= thousand + 1'b1;

assign q = {thousand,hundred,ten,one};

assign ena[1] = (one == 4'd9)? 1'b1:1'b0;

assign ena[2] = (ten == 4'd9 && one == 4'd9)? 1'b1:1'b0;

assign ena[3] = (hundred == 4'd9 && ten == 4'd9 && one == 4'd9)? 1'b1:1'b0;

endmodule

- 仿真波形图

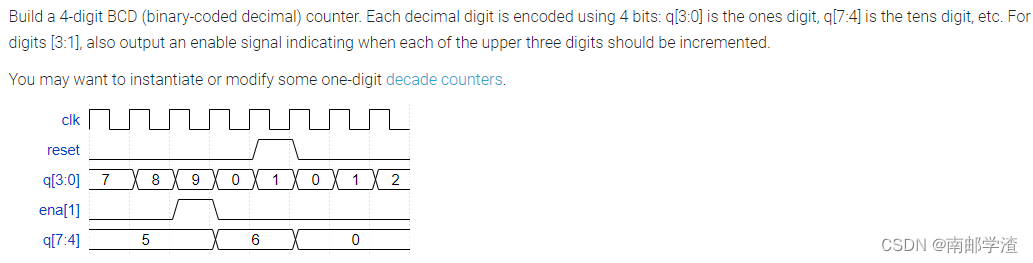

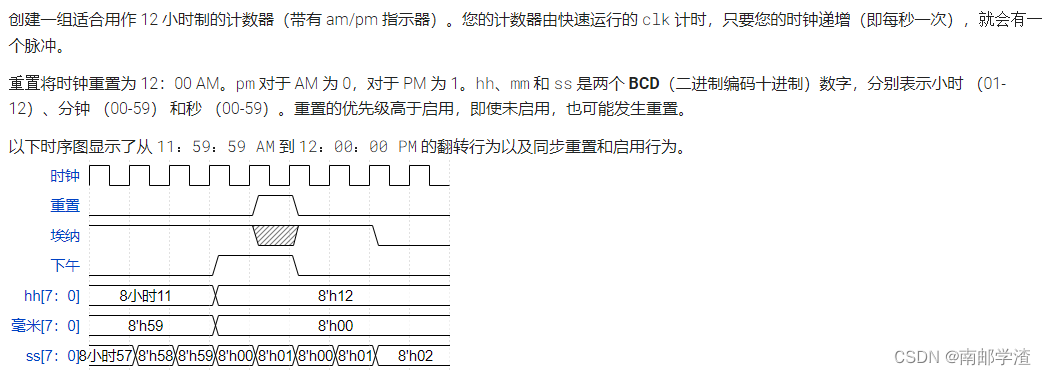

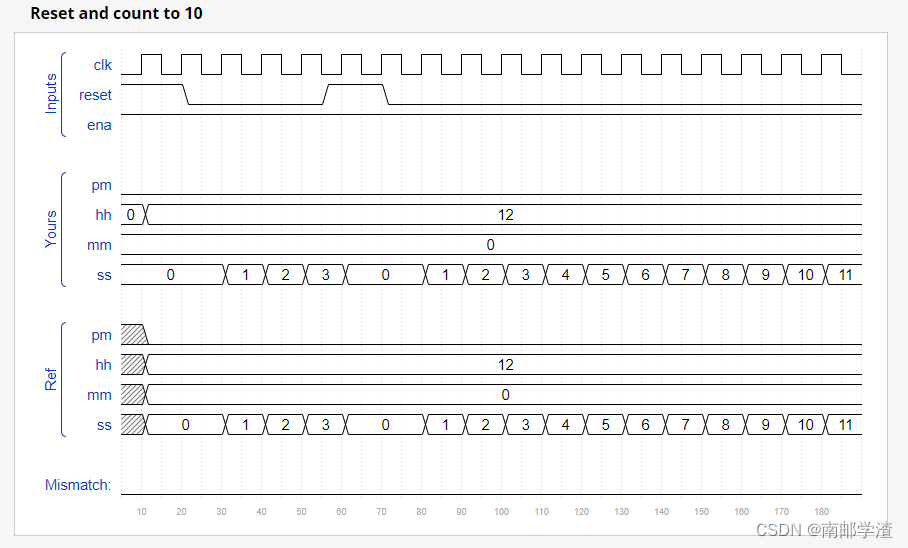

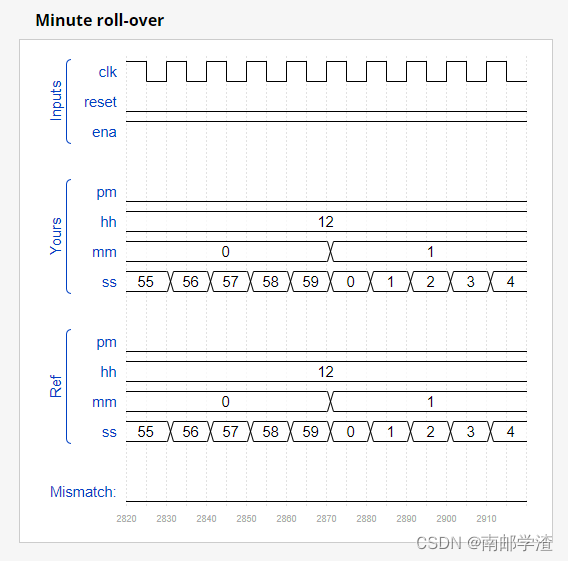

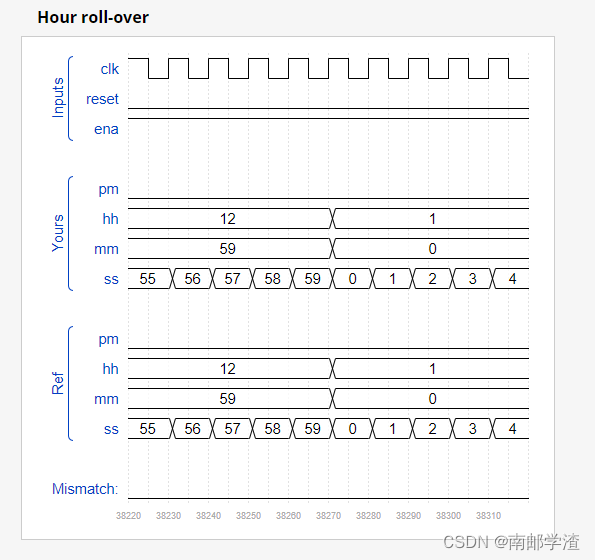

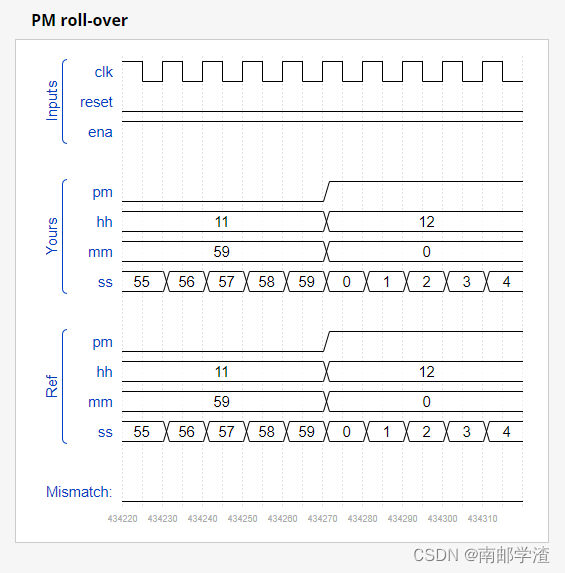

八、12-hour clock

设计一个12小时计的时钟

- RTL代码

module top_module(

input clk,

input reset,

input ena,

output reg pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

reg [3:0]s1,s2;

reg [3:0]m1,m2;

reg [3:0]h1,h2;

always @(posedge clk)

if(reset)

s1 <= 1'b0;

else if(s1 == 4'd9 && ena)

s1 <= 1'b0;

else if(ena)

s1 <= s1 + 1'b1;

always @(posedge clk)

if(reset)

s2 <= 1'b0;

else if(s2 == 4'd5 && s1 == 4'd9 && ena)

s2 <= 1'b0;

else if(s1 == 4'd9 && ena)

s2 <= s2 + 1'b1;

always @(posedge clk)

if(reset)

m1 <= 1'b0;

else if(m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

m1 <= 1'b0;

else if(s2 == 4'd5 && s1 == 4'd9 && ena)

m1 <= m1 + 1'b1;

always @(posedge clk)

if(reset)

m2 <= 1'b0;

else if(m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

m2 <= 1'b0;

else if(m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

m2 <= m2 + 1'b1;

always @(posedge clk)

if(reset)

h1 <= 4'd2;

else if(h1 == 4'd2 && h2 == 4'd1 && m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

h1 <= 1'b1;

else if(h1 == 4'd9 && h2 == 4'd0 && m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

h1 <= 1'b0;

else if(m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

h1 <= h1 + 1'b1;

always @(posedge clk)

if(reset)

h2 <= 4'd1;

else if(h1 == 4'd2 && h2 == 4'd1 && m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

h2 <= 1'b0;

else if(h1 == 4'd9 && m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

h2 <= h2 + 1'b1;

assign hh = {h2,h1};

assign mm = {m2,m1};

assign ss = {s2,s1};

always @(posedge clk)

if(reset)

pm <= 1'b0;

else if(h2 == 4'd1 && h1 == 4'd1 && m2 == 4'd5 && m1 == 4'd9 && s2 == 4'd5 && s1 == 4'd9 && ena)

pm <= ~pm;

endmodule

- 仿真波形图

最后

以上就是愤怒小虾米最近收集整理的关于Verilog语法基础HDL Bits训练11:CountersCircuits:Sequential Logic:Counters的全部内容,更多相关Verilog语法基础HDL内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[Verilog学习笔记] always@(*)语句是什么意思](https://www.shuijiaxian.com/files_image/reation/bcimg24.png)

发表评论 取消回复