结论

①在always块中建立组合逻辑模型时,如果敏感列表没有完成,在仿真中将会以锁存器的形式出现,但是在综合中将列出所有的敏感信号列表,从而建立相应的组合逻辑(可能也是有锁存器的)。

②@*只能对always块中的信号敏感,对外部always块中的函数引用的信号不敏感。

③组合逻辑中要对RAM中的每个元素都敏感时,可以使用@*,也可以用@(addr,men[addr])

④敏感列表中存在有操作时,对于操作项而言,不会对操作数敏感,而是对操作后的结果敏感,所以不在敏感列表中进行操作。

实验

在绝大多数变成语言中,’*'都是表示包括所有可能,那么在Verilog中是不是也一样呢?为此,我用modelsim做了一个实验。

被测试的电路

module

test(in,en,rst_n,out);

input

[1:0]

in;

input

en;

input

[1:0]

rst_n;

output

[3:0]

out;

reg

[3:0]

out;

always

@(*)begin

if(!rst_n)

out=0;

else

out=out+in;

end

endmodule

//测试电路,testbench

`timescale 10ps/1ps

module

test_tb;

reg

[1:0]

in;

reg

en;

reg

[1:0]

rst_n;

wire

[3:0]

out;

initial begin

#1

in=1;

#1

en=0;

#1

rst_n=1;

#1

rst_n=0;

#1

rst_n=1;

#1

rst_n=2;

#1

rst_n=3;

#1

in=1;

#1

in=2;

#1

in=3;

end

always

#1

en=~en;

test test_top(in,en,rst_n,out);

endmodule

说明:这里,被测试的电路中,输出out等于其本身加上输入in,但要在’※'的激发下才能进行;在testbench 电 路中,首先复位并初始化各个信号的值,然后再改变各个信号的值,观察out值的变化,以此来确定 '※'所代表的信号。

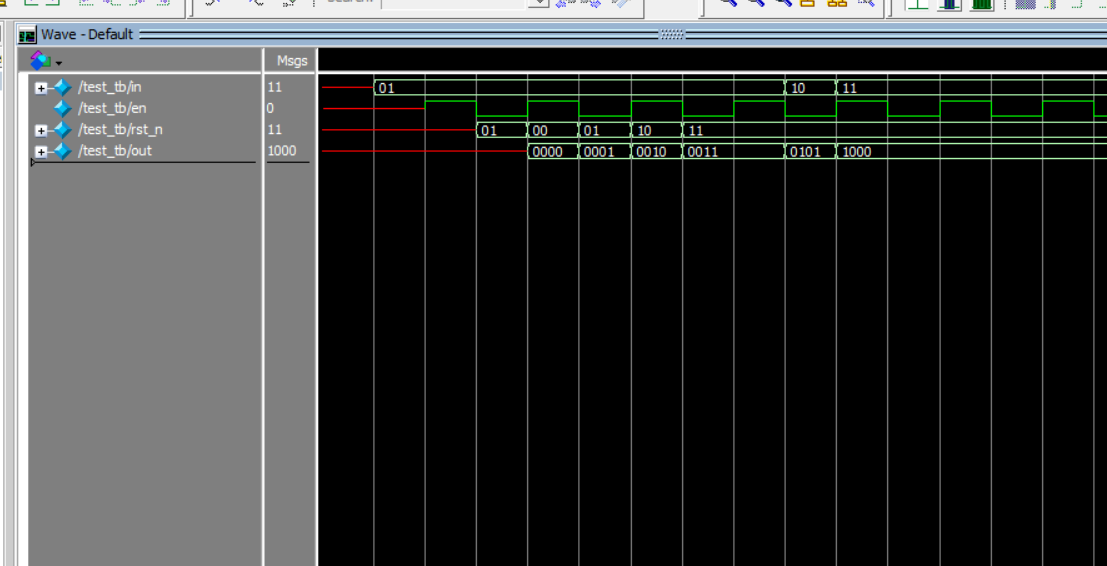

用modelsim仿真后的波形:

由仿真后的波形中可以看出:(1)当rst_n复位后,也就是从1变成0时,out变成0,而out赋值语句是包含在always @(※)中的,这就说明rst_n的变化激发了always模块的执行,则rst_n信号是包含在’※’ 中的。后面,rst_n每变一次值,out都加上in的值,也证明了’ ※ ‘包括了rst_n信号。(2)之后,in每变一次值,always模块都执行一次,out都加上了此时的in值,则说明’※‘也包括了in信号。(3)再往后,en不停的从0变成1再变成0,但out的值始终没变,则说明’※'不包括en信号。

结论:在Verilog中,※只包括该模块中的所有信号,没在该模块中出现的信号不包含于※。

最后

以上就是怡然微笑最近收集整理的关于always @(*) 中‘*’所代表的意思结论实验的全部内容,更多相关always内容请搜索靠谱客的其他文章。

![[Verilog学习笔记] always@(*)语句是什么意思](https://www.shuijiaxian.com/files_image/reation/bcimg24.png)

发表评论 取消回复