相关推荐

S型源表与2400,2450及B2900相比有哪些不同? ①、2400为吉时利第一代数字源表,单通道....

发表于 10-23 13:34 •6次 阅读

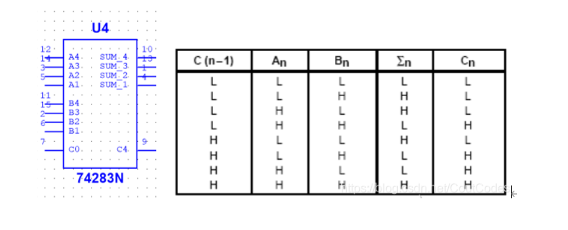

用两片加法器芯片74283配合适当的门电路完成两个BCD8421码的加法运算。(输入两个以BCD84....

振荡器从一个初始状态经过一段时间又回到这个状态;这个时间间隔定义为振荡器的一个循环,又叫周期。

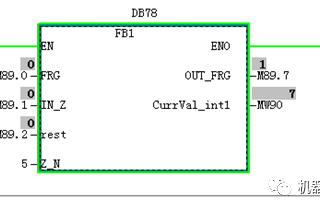

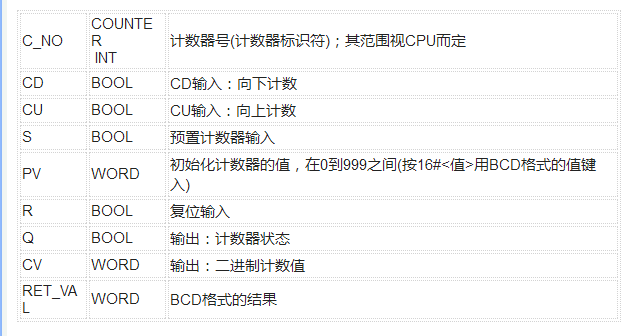

可使用分配参数并加计数指令递增计数器值。当 CU 参数的信号状态从0变为1(信号上升沿)时,当前计数....

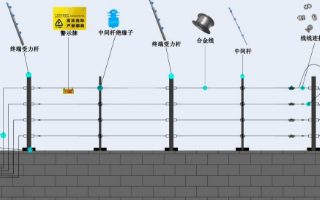

脉冲电子围栏工作原理: 脉冲电子围栏系统有别于传统的高压电网,脉冲电子围栏系统可识别有意入侵和无意入....

发表于 10-12 15:49 •33次 阅读

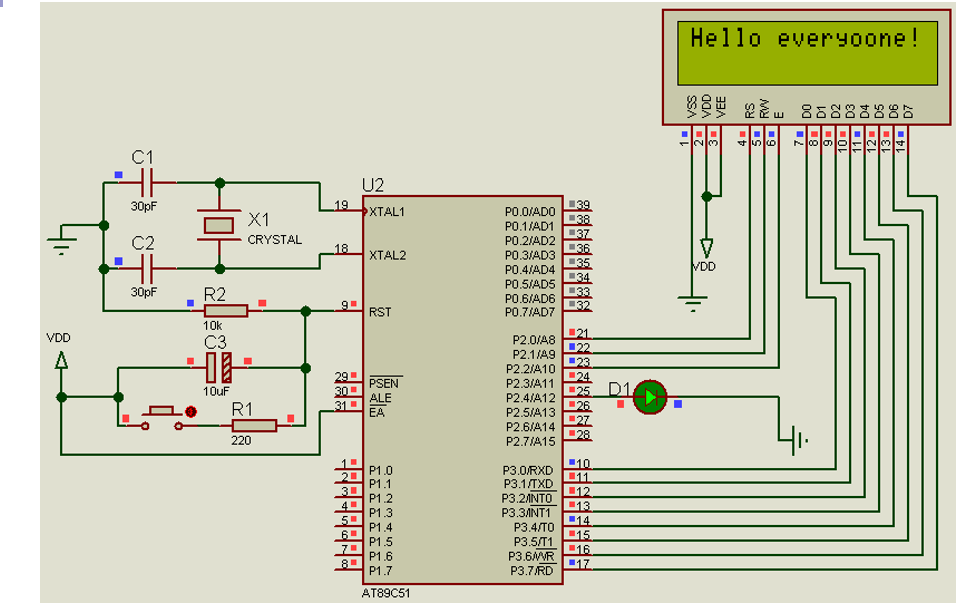

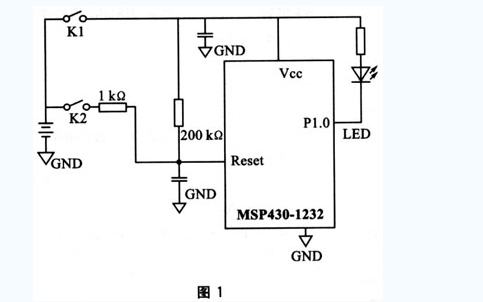

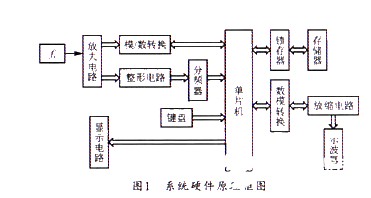

虚拟仿真开发:用软件手段对单片机应用系统进行仿真开发,与用户样机硬件无任何联系,只需在PC机安装Pr....

发表于 10-10 16:34 •432次 阅读

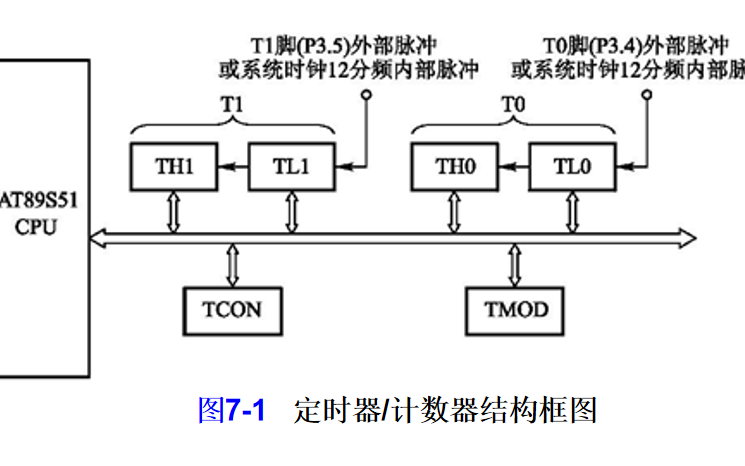

AT89S51定时器/计数器结构见图 7-1,定时器/计数器T0由特殊功能寄存器TH0、TL0构成,....

发表于 10-10 16:34 •42次 阅读

据芯视界官方网站介绍,公司成立于2018年,拥有先进的光电转换器件设计和单光子检测成像技术,主营固态....

10-09 15:37

• 446次 阅读

对于那些人类无法持续监视的嵌入式系统,看门狗芯片可能是个很好的解决方案。英锐恩单片机开发工程师表示,....

发表于 10-09 08:00 •36次 阅读

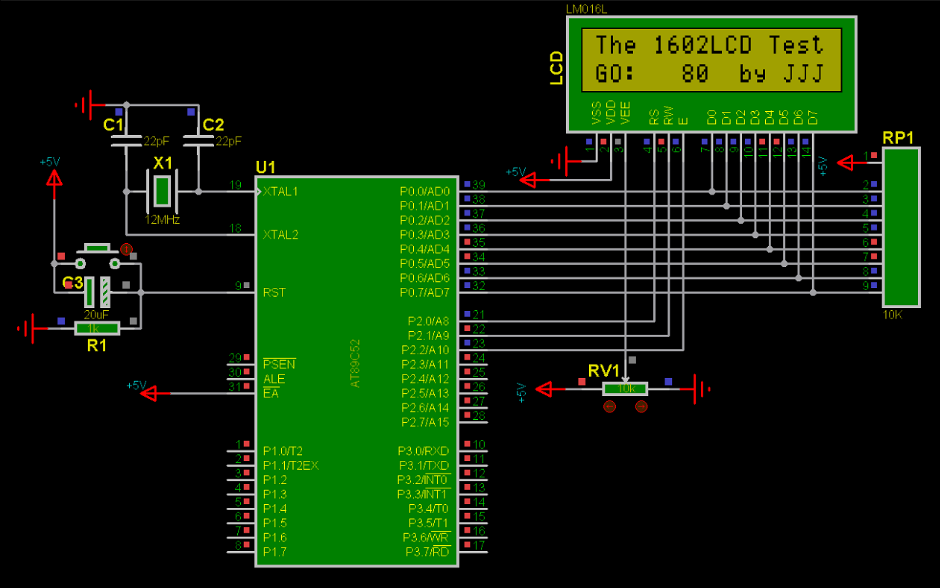

本文档的主要内容详细介绍的是使用单片机实现LCD1602脉冲计数器的程序和仿真电路图免费下载。

发表于 10-09 08:00 •40次 阅读

近年来,随着现代化科学技术的飞速发展,犯罪分子犯罪智能化、复杂化、隐蔽性加强,因此,促使安全防范技术....

发表于 10-09 07:25 •52次 阅读

AT89S51 是一个低功耗,高性能CMOS 8位单片机,片内含8k Bytes ISP(In-sy....

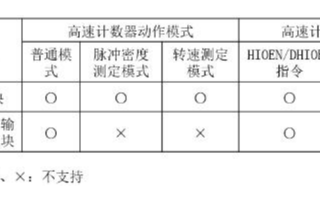

可编程控制器可接收计数脉冲,频率可高达几k到几十k赫兹。可用多种方式接收这脉冲,还可多路接收。有的可....

发表于 10-06 17:43 •262次 阅读

看门狗的作用: 看门狗定时器是一个计数器,基本功能是在发生软件问题和程序跑飞后使系统重新启动。看门狗....

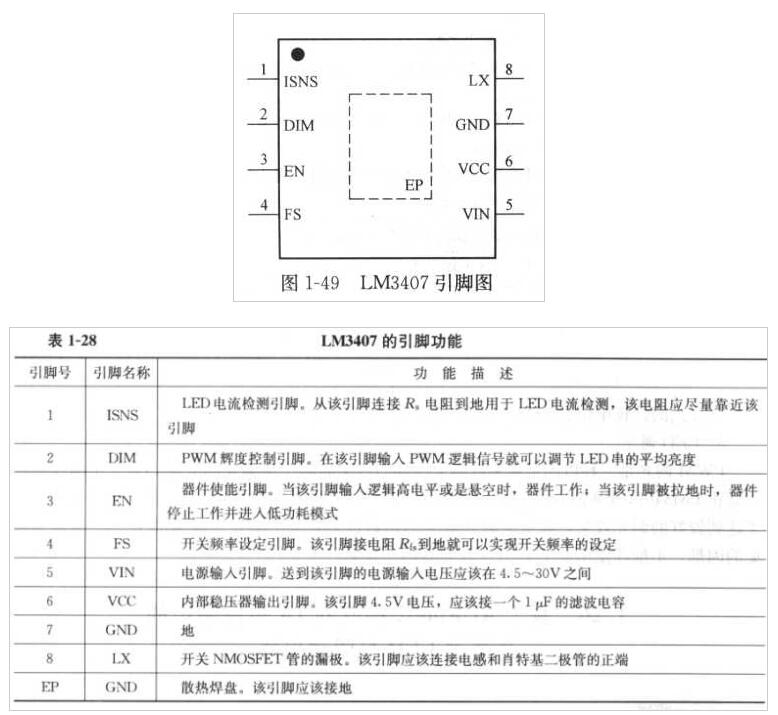

LM3407是一款集成了N沟道功率MOS场效应管的脉冲宽度调制的浮动式降压转换器,其设计是为提供精准....

10-03 16:56

• 250次 阅读

红外光谱仪可以检测和分析来自分子的反向散射光,分子的固有振动将化学信息反映在光谱中。日本东京大学的T....

09-26 09:44

• 387次 阅读

符合 标准的E1 帧结构如图1 所示,每基本帧由32 个路时隙(ts0“ts31)组成,分....

发表于 09-25 17:20 •141次 阅读

一、 高速计数器的介绍 01 高速计数器功能的概要 高速计数器是使用CPU模块的通用输入端子及高速脉....

SIMATIC S7-1500 自动化系统、基于 SIMATIC S7-1500 的 CPU 151....

发表于 09-25 08:00 •115次 阅读

正如WABeta Info的专家告诉我们的那样,WhatsApp正在开发一项新功能,它将引入自动删除....

09-23 16:01

• 248次 阅读

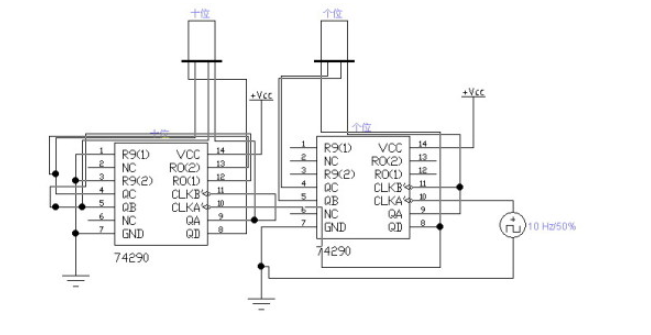

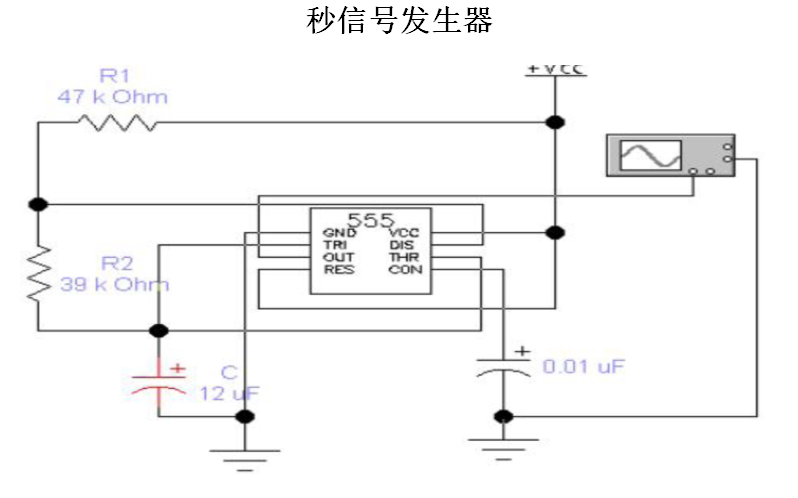

设计说明: 1. 秒钟与分钟显示电路: 分秒显示为60进1,利用两片74290组成的60进制计数器如....

超净工作台由三相电机作鼓风动力,功率145~260W左右,在其特定的空间内通过其风机将空气吸入预过滤....

发表于 09-19 09:17 •149次 阅读

定时器0设置于模式1时,计数寄存器为16位模式,由高8位TH0和低8位TL0两个8位寄存器组成,当设....

09-18 17:07

• 757次 阅读

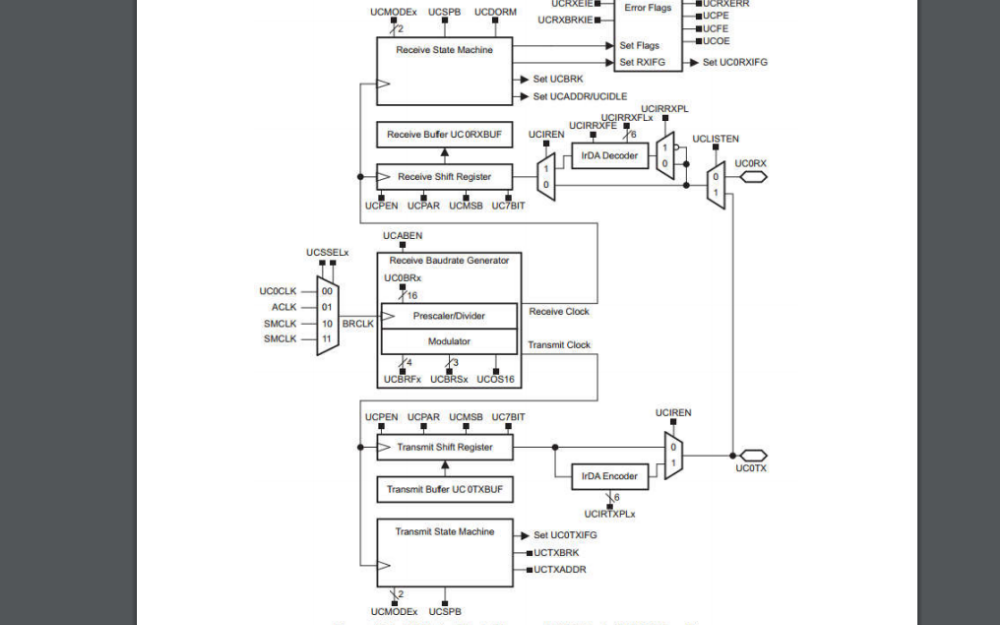

USI 模块提供了支持同步串行通信的基本功能。在其最简单的形式,它是一个 8 位或 16 位移位寄存....

发表于 09-15 08:00 •59次 阅读

粉尘传感器又称传感器,主要用来检测一定空间内粉尘浓度值,现在人们重点关注的颗粒物....

发表于 09-14 16:19 •40次 阅读

近年来,随着现代化科学技术的飞速发展,犯罪分子犯罪智能化、复杂化、隐蔽性加强,因此,促使安全防范技术....

发表于 09-11 17:27 •78次 阅读

如今人们对于住宅需求早已今非昔比,不但需要足够大的空间,而且对于住宅所处位置是否交通便利,环境如何,....

发表于 09-11 17:11 •184次 阅读

本文档的主要内容详细介绍的是脉冲按键电话显示器实验的工程文件免费下载。

发表于 09-11 16:55 •57次 阅读

当参数 S 的信号状态从“0”变为“1”时,计数器值将置位为参数 PV 的值。如果置位计数器且输入 ....

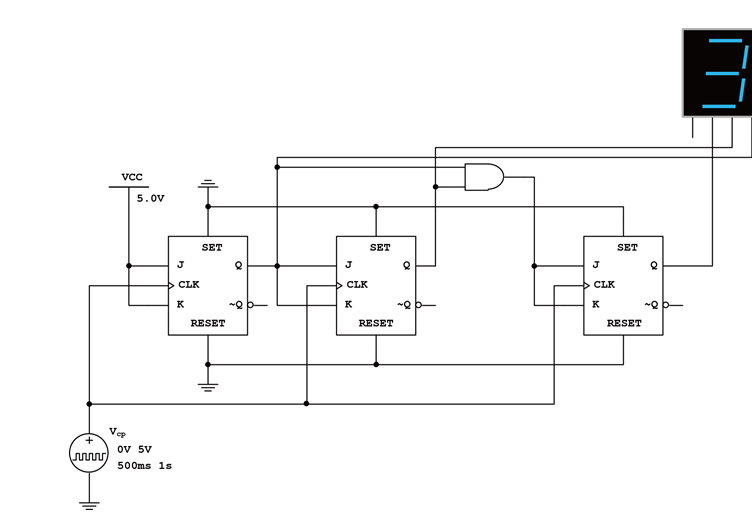

本文档的主要内容详细介绍的是使用Multisim仿真实例实现二进制计数器的实验电路图免费下载。

发表于 09-04 16:55 •84次 阅读

本文档的主要内容详细介绍的是十进制计数器的Multisim仿真实例电路图免费下载。

发表于 09-04 16:55 •117次 阅读

本文档的主要内容详细介绍的是3D计数器的Multisim仿真实例数电实验图免费下载。

发表于 09-03 18:22 •74次 阅读

反应能力测试器可用来检测和训练人的快速反应能力,它有多种结构形式,下面介绍的这个反应能力测试仪,采用十进制计数器4017...

发表于 09-03 17:45 •101次 阅读

可使用“分配参数并加计数”指令递增计数器值。当 CU 参数的信号状态从“0”变为“1”(信号上升沿)....

频率响应测量需要具有平坦频谱的信号源。通过将示波器的快速边沿测试信号用作阶跃信号源,再利用示波器的衍....

发表于 09-03 09:37 •257次 阅读

变频器的电路检修中,尤其是将驱动电路与主电路脱开检修的过程中,经常碰到OC故障报警现象,而此时变频器....

09-02 09:46

• 691次 阅读

用四通道示波器观察时钟clk及各级触发器输出的Q0、Q1、Q2信号。根据观察,在图2中画出Q0、Q1....

发表于 08-31 16:55 •279次 阅读

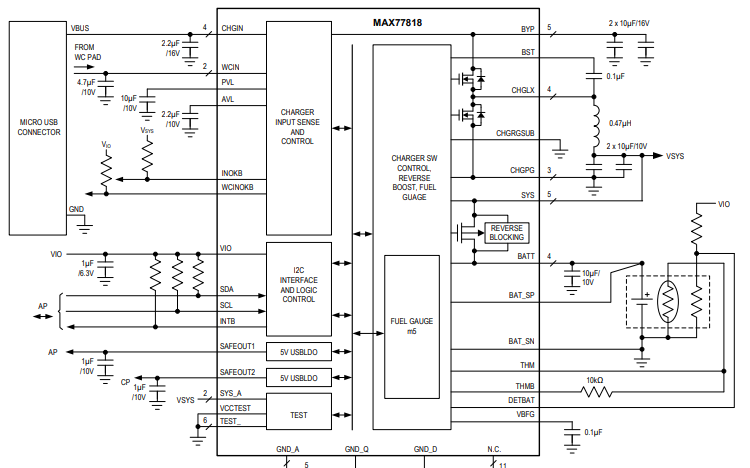

MAX77818集成了一个高性能3A开关充电器和专有型号的仪表™ m5燃油表在一个节省空间的WLP包....

发表于 08-31 08:00 •224次 阅读

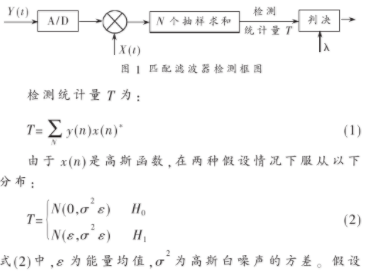

如果已知授权用户的先验信息 ,如调制类型、脉冲整形等,可以用匹配滤波器检测。它能使输出信噪比最大化,....

发表于 08-28 09:59 •146次 阅读

每个输出可高达80 PTs,高达四个总体OE控制,四个专用总体时钟输入接口,每个宏单元都具备时钟、输....

我有一个CPLD和一个FPGA。 CPLD向FPGA发送时钟。 我还需要一个触发信号去FPGA,但我的引脚用尽了。 在发...

发表于 08-26 15:09 •0次 阅读

脉冲激光测距仪作为军用装备器材,发展于60 年代初。经过30 多年的开发、研制和装备,目前国外已....

发表于 08-26 10:40 •275次 阅读

据CNN介绍,沙耶尔是第一代iPod的软件工程师,他17日在专注研究苹果公司的“TidBits”网站....

08-26 09:22

• 720次 阅读

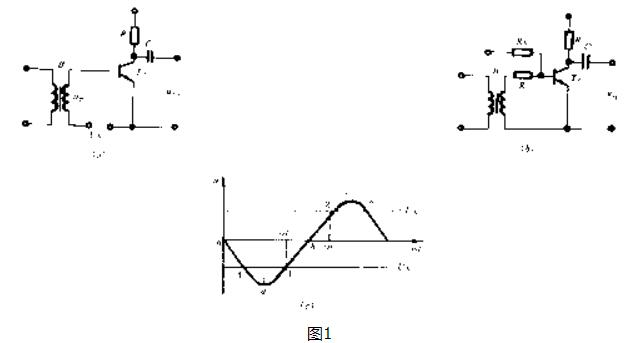

在由晶闸管构成的整流电路中,晶闸管门极触发电路的作用通常是根据直流控制电压的大小决定触发角a的大小,....

08-25 17:54

• 857次 阅读

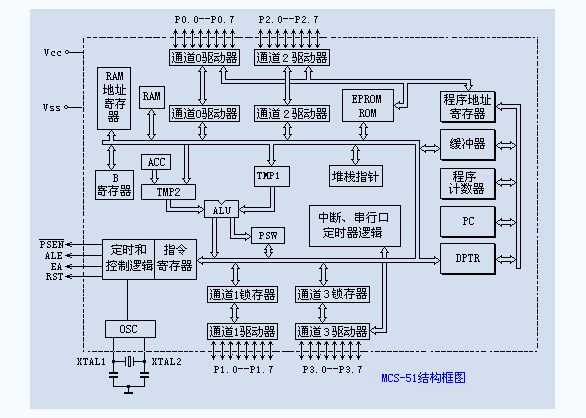

8051内部有128个8位用户数据存储单元和128个专用寄存器单元,它们是统一编址的,专用寄存器只能....

e 络盟拥有来自泰克等全球领先供应商的广泛系列测试和测量产品,且其中有数百种产品均支持当天发货。e ....

发表于 08-21 15:25 •99次 阅读

该交通灯定时控制系统的组成框图如图1所示。由状态控制器、状态译码器、减法计数器、秒脉冲发生等组成。 ....

发表于 08-21 14:51 •95次 阅读

为了提高测量的精度,拓展单片机的测频范围,本设计采取了对信号进行分频的方法。设计中采用两片同步十进制....

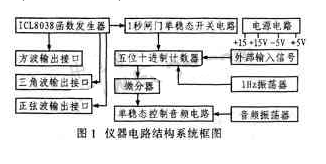

工厂计量部门、科研院所、大学物理实验室使用函数信号发生器和计数器计量、维修、实验和教学,但大多是把函....

发表于 08-21 09:37 •121次 阅读

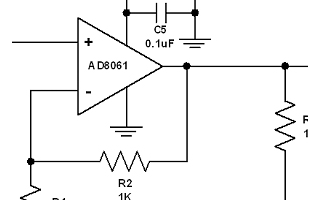

与典型的时钟缓冲应用相比,消费类电子应用的工作频率较低,需求较少,采用低成本的高速运算放大器(~10....

发表于 08-20 14:14 •212次 阅读

是否有任何可用于UG472中提到的“计数器级联”的示例设计。 -谢谢...

发表于 08-10 09:31 •0次 阅读

光栅作为精密测量的一种工具,由于他本身具有的优点,已在精密仪器、坐标测量、精确定位、高精度精密加工等领域得到了广泛的应用...

发表于 08-05 06:24 •0次 阅读

打算用ecap的脉冲检测功能测量电压频率,将电压由正弦波转换成方波之后,由于电压存在谐波,脉冲波形存在一点瑕疵,如下图所示,...

发表于 07-21 13:18 •0次 阅读

最近接触声纳发射机,里面常出现信号形式为CW脉冲的说法,那么CW脉冲是什么? 自己查了一下是说CW代表顺时针旋转,所以请...

发表于 07-20 08:10 •101次 阅读

难道是epwmx的两个pwm输出口分别对应的是cmpA和cmpB。A输出口跟B输出口的比较值可以设成不一样。那A口跟B口的占空比就不...

发表于 07-16 10:24 •101次 阅读

给的钛酸锂电池充电 正负脉冲电流多大合适?间歇时间呢? 各位烧友求指导 ...

发表于 07-16 09:43 •303次 阅读

视频讲解双脉冲基本原理及意义,点击下方链接在线观看 ...

发表于 06-24 14:18 •79次 阅读

FPGA的很有发展前景,那你知道FPGA是怎样产生的吗?20世纪60年代,晶体管技术迅速的发展,数字集成电路以双极型工艺制成...

发表于 06-23 13:54 •354次 阅读

与其它产品相比 计数器/算术/奇偶校验功能 Technology Family VCC (Min) (V) VCC (Max) (V) Rating Operating temperature range (C) Package Group SN74HC4040A HC 2 6 Catalog -40 to 85 SO | 16 TSSOP | 16

发表于 01-08 17:46 •203次 阅读

CD54 /74HC190是异步预设的BCD十进制计数器,而CD54 /74HC191和CD54 /74HCT191是异步预设的二进制计数器。 通过低异步并行负载(LOAD)输入完成预置数字输入(A ?? D)上的数字预置。当LOAD 为高电平,计数使能(CTEN)为低电平时,计数发生,向下/向上(D /U)输入为低电平表示减计数或低电平表示向上计数。计数器与时钟从低到高的转换同步递减或递增。 当计数器发生上溢或下溢时,MAX /MIN输出(在计数期间为低电平)变高并且在一个时钟周期内保持高电平。此输出可用于高速级联中的先行进位(参见图1)。 MAX /MIN输出还启动纹波时钟(RCO)输出,该输出通常为高电平,变为低电平,并在时钟脉冲的低电平部分保持低电平。这些计数器可以使用RCO 进行级联(参见图2)。 如果将十进制计数器预设为非法状态或在接通电源时采用非法状态,则会返回正常序列中的一个或两个计数,如状态图所示(见图3)。 特性 2-V至6-VV CC 操作(?? HC190,191) 4.5 V至5.5 VV CC 操作(?? HCT191) 55至125°C的宽工作温度范围 同步计数和...

发表于 11-02 19:21 •96次 阅读

?? AC161设备是4位二进制计数器。这些同步可预置计数器具有内部进位预测功能,适用于高速计数应用。这些器件完全可编程;也就是说,它们可以预设为0到9或15之间的任何数字。预设是同步的;因此,在负载输入处设置低电平会禁用计数器,并使输出在下一个时钟脉冲之后与设置数据一致,无论使能输入的电平如何。 清除功能是异步。清零(CLR)输入的低电平将所有四个触发器输出设置为低电平,无论CLK,负载(LOAD)或使能输入的电平如何。 进位外观 - 前端电路为n位同步应用提供级联计数器,无需额外的门控。有助于实现此功能的是ENP,ENT和纹波进位输出(RCO)。 ENP和ENT都必须高计数,并且ENT被前馈以启用RCO。当计数最大时(9或15,Q A 为高电平),启用RCO会产生高电平脉冲。这种高电平溢出纹波进位脉冲可用于实现连续级联级。无论CLK的电平如何,都允许ENP或ENT的转换。 计数器具有完全独立的时钟电路。在发生计时之前,修改操作模式的控制输入(ENP,ENT或LOAD )的更改不会影响计数器的内容。计数器的功能(无论是启用,禁用,加载还是计数)仅由满足稳定设置和保持时间的条件决定。 特性 快速...

发表于 11-02 19:21 •62次 阅读

?? AC280和?? ACT280是采用高级CMOS逻辑技术的9位奇数/偶数奇偶校验发生器/检查器。偶数和奇数奇偶校验输出均可用于检查或生成长达9位的字的奇偶校验。甚至指示奇偶校验( E输出到另外的任何输入?AC280,?? ACT280奇偶校验器。 特性 缓冲输入 典型传播延迟 - 在V CC = 5V时为10ns ,T A = 25°C,C L = 50pF 超过MIL-STD-883的2kV ESD保护,方法3015 耐SCR闩锁CMOS工艺和电路设计 功耗显着降低的双极FAST ?? /AS /S速度 平衡传播延迟 < li> AC类型具有至的工作电压和30%电源的均衡噪声抗扰度 ±24mA输出驱动电流 - 扇出至15 FAST ??集成电路 - 驱动器50 传输线 表征操作来自?? 40°至85°C FAST ??是飞兆半导体的商标。 参数 与其它产品相比 计数器/运算器/奇偶校验功能产品 Technology Family VCC (Min) (V) VCC (Max) (V) Bits (#) Voltage (Nom) (V) F @ Nom Voltage (Max) (Mhz) ICC @ Nom Voltage (Max) (mA) tpd @ Nom Voltage (Max) (ns) IOL (Max) (mA) Function Type...

发表于 11-02 19:21 •33次 阅读

CD4060B由振荡器部分和14个纹波进位二进制计数器级组成。振荡器配置允许设计RC或晶体振荡器电路。提供RESET输入,将计数器复位到全O状态并禁用振荡器。 RESET线上的高电平完成复位功能。所有计数器阶段都是主从触发器。在 O )。所有输入和输出均完全缓冲。施密特触发器对输入脉冲线的作用允许无限制的输入脉冲上升和下降时间。 CD4060B系列类型采用16引脚密封双列直插式陶瓷封装(F3A后缀), 16引脚双列直插塑料封装(E后缀),16引脚小外形封装(M,M96,MT和NSR后缀),以及16引脚薄型收缩小外形封装(PW和PWR后缀)。 特性 15 V时12 MHz时钟频率 常用复位 完全静态操作 缓冲输入和输出 施密特触发器输入脉冲线 在20 V下测试静态电流100% 标准化,对称输出特性< /li> 5 V,10 V和15 V参数额定值 符合JEDEC暂定标准No. 13B的所有要求,“B ??系列说明的标准规范” CMOS器件?? 振荡器特性: 芯片上的所有有源元件 RC或晶体振荡器配置 RC振荡器频率为690 kHz最小电压15 V 应用 控制计数器 定时器 分频器 延时电路 参数 与其它产品相比 计数器/运算器/奇偶校验功能产品 ...

发表于 11-02 19:21 •131次 阅读

CD40192b可预置BCD向上/向下计数器和CD40193B可预设二进制向上/向下计数器均由4个同步时钟控制的门控“D”型触发器组成作为一个柜台。输入包括4个独立的阻塞线,一个PRESET ENABLE 控制,单独的CLOCK UP和CLOCK DOWN信号以及一个主RESET。提供四个缓冲Q信号输出以及用于多级计数方案的CARRY 和BORROW 输出。 计数器被清零,以便所有输出在RESET线上处于低电平状态。 RESET与时钟异步完成。当PRESET ENABLE 控制为低电平时,每个输出都可以与相应的卡纸输入电平的时钟异步编程。 计数器在CLOCK UP信号的正时钟沿计数一个计数如果CLOCK DOWN线为高电平。如果CLOCK UP线为高电平,计数器会对CLOCK DOWN信号的正时钟沿计数递减计数。 CARRY 和BORROW 信号为高电平,计数器向上或向下计数。在计数器达到计数模式下的最大计数后,CARRY 信号在半个时钟周期内变为低电平。在计数器达到倒计数模式下的最小计数后,BORROW 信号在半个时钟周期内变为低电平。通过将BORROW 和CARRY 输出分别连接到后续计数器...

发表于 11-02 19:21 •154次 阅读

CD40160B,CD40161B,CD40162B和CD40163B是4位同步可编程计数器。 CD40162B和CD40163B的CLEAR功能是同步的,CLEAR 输入的低电平在下一个正的CLOCK边沿将所有四个输出设置为低电平。 CD40160B和CD40161B的CLEAR功能是异步的,CLEAR 输入的低电平将所有四个输出设置为低电平,而不管CLOCK,LOAD 或ENABLE输入的状态如何。 LOAD 输入的低电平禁用计数器,并使输出与下一个CLOCK脉冲后的设置数据一致,无论ENABLE输入的条件如何。 进位预测电路提供用于n位同步应用的级联计数器,无需额外的门控。完成此功能的工具有两个计数使能输入和一个进位输出(C OUT )。当PE和TE输入均为高电平时,计数启用。 TE输入被前馈以使能C OUT 。该使能输出产生正输出脉冲,其持续时间约等于Q1输出的正部分。该正溢出进位脉冲可用于实现连续级联级。当时钟为高电平或低电平时,可能会发生PE或TE输入的逻辑转换。 CD40160B类型采用16引脚密封双列直插式陶瓷封装(F3A后缀)。 CD40161B型采用16引脚密封双列直插式陶瓷封装(F3A后缀),16引脚双列直插塑料封装(E后...

发表于 11-02 19:21 •218次 阅读

CD4518双BCD上行计数器和CD4520双二进制上行计数器均由两个相同的内部同步4级计数器组成。计数器级是D型触发器,具有可互换的CLOCK和ENABLE线,用于递增正向或负向转换。对于单机操作,ENABLE输入保持高电平,计数器在CLOCK的每个正向转换时前进。计数器在其RESET线上被高电平清零。 通过将Q4连接到后续计数器的使能输入,同时后者的CLOCK输入保持低电平,可以在纹波模式下级联计数器。 CD4518B和CD4520B型采用16引脚密封双列直插陶瓷封装(F3A后缀),16引脚双列直插塑料封装(E后缀),16引脚小型-outline包(M,M96和NSR后缀)和16引脚薄收缩小外形封装(PW和PWR后缀)。 特性 中速操作 - 10 V时的6 MHz典型时钟频率 正或负 - 边沿触发 同步内部进位传播 100%测试20 V时的静态电流 在整个封装温度下,18 V时的最大输入电流为1μA范围;在18 V和25°C下100 nA 噪声容限(在整个封装温度范围内): 1 V,V DD = 5 V 2 V V DD = 10 V 2.5 V V DD = 15 V 5 V,10 V和15 V参数额定值 标准化,对称输出特性 符合JEDEC暂定标准No. 13B的所有...

发表于 11-02 19:21 •127次 阅读

?? HC161,?? HCT161,?? HC163和?? HCT163是可预设的同步计数器,具有先行进位逻辑,可用于高电平高速计数应用程序。 ?? HC161和?? HCT161分别是异步复位十进制和二进制计数器; ?? HC163和?? HCT163器件分别是十进制和二进制计数器,它们与时钟同步复位。计数和并行预置都与时钟的负到正转换同步完成。 同步并行使能输入SPE的低电平禁用计数操作并允许P0到P3的数据输入要加载到计数器中(前提是满足SPE的建立和保持要求)。 所有计数器在主复位输入MR上以低电平复位。在?? HC163和?? HCT163计数器(同步复位类型)中,必须满足相对于时钟的建立和保持时间要求。 每个计数器中有两个计数使能,PE和TE提供n位级联。在所有计数器中,无论SPE ,PE和TE输入的电平(以及时钟输入,CP,在?? HC161和?? HCT161类型中)都会发生复位操作。 如果是十年计数器当电源被施加电源时,它被预置为非法状态或呈现非法状态,它将以一个计数返回到正常序列,如状态图所示。 先行进位功能简化了串行级联计数器。两个计数使能输入(PE和TE)必须为高才能计数。 TE输入通过所有四个级的Q输出进行门控,以便在最大计数时,终...

发表于 11-02 19:21 •64次 阅读

具有快速进位的?? AC283和?? ACT283 4位二进制加法器,采用先进的CMOS逻辑技术。如果总和超过15,这些器件会添加两个4位二进制数并生成进位。 由于add函数的对称性,该器件可与所有高电平有效操作数一起使用(正逻辑)或所有低电平有效操作数(负逻辑)。使用正逻辑时,如果没有进位,则必须将进位输入连接为低电平。 特性 缓冲输入 超过2kV ESD保护MIL-STD-883,方法3015 SCR -Lackup-Resistant CMOS工艺和电路设计 双极FAST ?? /AS /S速度显着降低功耗 平衡传播延迟 AC类型具有至的工作电压和30%供电时的平衡噪声抗扰度 ±24mA输出驱动电流 - 扇出至15 FAST ??集成电路 - 驱动器50 传输线 表征操作来自?? 40°至85°C FAST ??是Fairchild Semiconductor的商标。 参数 与其它产品相比 计数器/运算器/奇偶校验功能产品 Technology Family VCC (Min) (V) VCC (Max) (V) Bits (#) Voltage (Nom) (V) F @ Nom Voltage (Max) (Mhz) ICC @ Nom Voltage (Max) (mA) tpd @ Nom Voltage (Max) (ns) IOL (Max) (mA) ...

发表于 11-02 19:21 •30次 阅读

CD4510B可预置BCD向上/向下计数器和CD4516可预置二进制向上/向下计数器由四个同步时钟控制的D型触发器组成(带有门控结构)提供T型触发器功能)作为计数器连接。这些计数器可以通过RESET线上的高电平清除,并且可以通过PRESET ENABLE线上的高电平预设为卡纸输入上的任何二进制数。 CD4510B将在向上模式下最多两个时钟脉冲计数非BCD计数器状态,在向下模式下最多四个时钟脉冲。 如果保持CARRY-IN输入低电平,计数器在每个正向时钟转换时上升或下降。同步级联是通过并联所有时钟输入并将不太重要的级的CARRY-OUT连接到更重要级的CARRY-IN来实现的。 CD4510B和CD4516B可以级联在纹波中通过将CARRY-OUT连接到下一级的时钟来实现模式。如果在终端计数期间UP /DOWN输入发生变化,则必须使用时钟门控CARRY-OUT,并且在时钟为高电平时必须更改UP /DOWN输入。该方法为随后的计数阶段提供干净的时钟信号。 (见图15)。 这些器件类似于MC14510和MC14516。 CD4510B和CD4516B类型采用16引脚双列直插塑料封装( E后缀),16引脚小外形封装(NSR后缀)和16引脚薄缩小外...

发表于 11-02 19:21 •88次 阅读

CD4017B和CD4022B分别是具有10和8个解码输出的5级和4级Johnson计数器。输入包括CLOCK,RESET和CLOCK INHIBIT信号。 CLOCK输入电路中的施密特触发器动作提供脉冲整形,允许无限制的时钟输入脉冲上升和下降时间。 如果CLOCK INHIBIT信号为低电平,这些计数器在正时钟信号转换时提前一位计数。当CLOCK INHIBIT siganl为高电平时,禁止通过时钟线的计数器前进。高RESET信号将计数器清零至零计数。 Johnson计数器配置的使用允许高速操作,2输入解码门控和无尖峰解码输出。提供防锁定门控,从而确保正确的计数顺序。解码输出通常为低并且仅在它们各自的解码时隙处变高。每个解码输出在一个完整时钟周期内保持高电平。 CAR40-B信号在CD4017B中每10个时钟输入周期或CD4022B中每8个时钟输入周期完成一次,用于在多器件计数链中对后续器件进行纹波时钟。 CD4017B和CD4022B采用16引脚密封双列直插式陶瓷封装(F3A后缀),16引脚双列直插塑料封装(E后缀),16引脚小外形封装(NSR后缀)和16引脚薄收缩小外形封装(PW和PWR后缀)。 CD4017B类型还提供16引脚小外形封装(M和M9...

发表于 11-02 19:21 •130次 阅读

具有快速进位的?? AC283和?? ACT283 4位二进制加法器,采用先进的CMOS逻辑技术。如果总和超过15,这些器件会添加两个4位二进制数并生成进位。 由于add函数的对称性,该器件可与所有高电平有效操作数一起使用(正逻辑)或所有低电平有效操作数(负逻辑)。使用正逻辑时,如果没有进位,则必须将进位输入连接为低电平。 特性 缓冲输入 超过2kV ESD保护MIL-STD-883,方法3015 SCR -Lackup-Resistant CMOS工艺和电路设计 双极FAST ?? /AS /S速度显着降低功耗 平衡传播延迟 AC类型具有至的工作电压和30%供电时的平衡噪声抗扰度 ±24mA输出驱动电流 - 扇出至15 FAST ??集成电路 - 驱动器50 传输线 表征操作来自?? 40°至85°C FAST ??是Fairchild Semiconductor的商标。 参数 与其它产品相比 计数器/运算器/奇偶校验功能产品 Technology Family VCC (Min) (V) VCC (Max) (V) Bits (#) Voltage (Nom) (V) F @ Nom Voltage (Max) (Mhz) ICC @ Nom Voltage (Max) (mA) tpd @ Nom Voltage (Max) (ns) IOL (Max) (mA) ...

发表于 11-02 19:21 •43次 阅读

CD4018B类型包括5个Johnson-Counter阶段,每个阶段的缓冲Q输出和计数器预设控制选通。提供时钟,复位,数据,预设启用和5个单独的JAM输入。通过将Q 5,Q 4,Q 3,Q 2,Q 1信号分别馈送回DATA输入,可以实现10,8,6,4或2个计数器配置的除法。通过使用CD4011B来控制到DATA输入的反馈连接,可以实现9,7,5或3个除计数器配置。通过使用多个CD4018B单元可以实现大于10的除法功能。计数器在正时钟信号转换时提前计数一次。时钟线上的施密特触发器动作允许无限制的时钟上升和下降时间。高RESET信号将计数器清零至全零状态。高PRESET-ENABLE信号允许JAM输入信息预设计数器。提供防锁定门控以确保正确的计数顺序。 CD4018B型采用16引脚密封双列直插式陶瓷封装(F3A后缀),16引脚双列直插式塑料封装(E后缀),16引脚小外形封装(M,M96,MT和NSR后缀),以及16引脚薄型收缩小外形封装(PW和PWR后缀)。 特性 中速运行???? 10 MHz(典型值)V DD ?? V SS = 10 V 完全静态工作 100%测试20 V时的静态电流 标准化,对称输出特性 5 V,10 V和15 V参数额定值 在整个封装温...

发表于 11-02 19:21 •74次 阅读

?? HC192,?? HC193和?? HCT193分别是异步预置的BCD十进制和二进制向上/向下同步计数器。 < p>将计数器预设为预设数据输入(P0-P3)上的数字是通过LOW异步并行负载输入(PL)来完成的。计数器在Clock-Up输入的低到高转换(和Clock-Down输入的高电平)上递增,并在Clock-Down输入的低到高转换时递减(和高电平时钟输入)。 MR输入的高电平会覆盖任何其他输入,以将计数器清零为零状态。终端向上计数(进位)在达到零计数之前的半个时钟周期内变为低电平,并在零计数时返回高电平。倒计数模式下的终端倒计数(借用)同样在最大计数之前的半个时钟周期内变低(192中的9和193中的15)并且在最大计数时返回高。通过将较低有效计数器的进位和借位输出分别连接到下一个最重要的计数器的Clock-Up和CLock-Down输入来实现级联。 如果存在十进制计数器非法状态或在接通电源时采取非法状态,它将按一个计数返回正常顺序,如状态图所示。 特性 同步计数和异步加载 N位级联的两个输出 前瞻进行高速计数 扇出(超温范围) 标准输出。 。 。 。 。 。 。 。 。 。 。 。 。 。 。 10 LSTTL负载 总线驱动器输出。 。 。 。 。 。 。 。 。...

发表于 11-02 19:21 •160次 阅读

CD40192b可预置BCD向上/向下计数器和CD40193B可预设二进制向上/向下计数器均由4个同步时钟控制的门控“D”型触发器组成作为一个柜台。输入包括4个独立的阻塞线,一个PRESET ENABLE 控制,单独的CLOCK UP和CLOCK DOWN信号以及一个主RESET。提供四个缓冲Q信号输出以及用于多级计数方案的CARRY 和BORROW 输出。 计数器被清零,以便所有输出在RESET线上处于低电平状态。 RESET与时钟异步完成。当PRESET ENABLE 控制为低电平时,每个输出都可以与相应的卡纸输入电平的时钟异步编程。 计数器在CLOCK UP信号的正时钟沿计数一个计数如果CLOCK DOWN线为高电平。如果CLOCK UP线为高电平,计数器会对CLOCK DOWN信号的正时钟沿计数递减计数。 CARRY 和BORROW 信号为高电平,计数器向上或向下计数。在计数器达到计数模式下的最大计数后,CARRY 信号在半个时钟周期内变为低电平。在计数器达到倒计数模式下的最小计数后,BORROW 信号在半个时钟周期内变为低电平。通过将BORROW 和CARRY 输出分别连接到后续计数器...

发表于 11-02 19:21 •256次 阅读

?? ACT163器件是4位二进制计数器。这些同步可预设计数器具有内部进位前瞻功能,适用于高速计数设计。通过使所有触发器同时计时以使得输出在由计数使能(ENP,ENT)输入和内部门控指示时彼此一致地改变来提供同步操作。这种工作模式消除了通常与同步(纹波时钟)计数器相关的输出计数尖峰。缓冲时钟(CLK)输入触发时钟波形上升(正向)边沿的四个触发器。 计数器完全可编程;也就是说,它们可以预设为0到9或15之间的任何数字。预设是同步的;因此,在负载输入处设置低电平会禁用计数器,并使输出在下一个时钟脉冲之后与设置数据一致,无论使能输入的电平如何。 清除功能是同步。无论使能输入的电平如何,清零(CLR)输入的低电平都会在CLK的下一次低电平到高电平转换后将所有四个触发器输出设置为低电平。这种同步清除允许通过解码Q输出以获得所需的最大计数来容易地修改计数长度。用于解码的门的低电平有效输出连接到CLR 以同步清除计数器0000(LLLL)。 进位超前电路为n位同步应用提供级联计数器没有额外的门控。 ENP,ENT和纹波进位输出(RCO)有助于实现此功能。 ENP和ENT都必须高计数,并且ENT被前馈以启用RCO。...

发表于 11-02 19:20 •83次 阅读

CD4029B由一个四级二进制或BCD十进制加/减计数器组成,在两种计数模式下均提供先行进位。输入包括单个CLOCK,CARRY-IN (CLOCK ENABLE ),BINARY /DECADE,UP /DOWN,PRESET ENABLE和四个单独的JAN信号,Q1,Q2,Q3,Q4和一个CARRY OUT 信号作为输出。 高PRESET ENABLE信号允许JAM INPUTS信息将计数器预设为与时钟异步的任何状态。当每个JAM线为低电平时,当PRESET-ENABLE信号为高电平时,将计数器复位为零计数。当CARRY-IN 和PRESET ENALBE信号为低电平时,计数器在时钟正跳变时前进一次。当CARRY-IN 或PRESET ENABLE信号为高电平时,进程被禁止。 CARRY-OUT 信号通常为高电平,当计数器在UP模式下达到最大计数或在DOWN模式下达到最小计数时,如果CARRY-IN 信号为低电平,则变为低电平。处于低状态的CARRY-IN 信号因此可以被认为是CLOCK ENABLE 。不使用时,CARRY-IN 端子必须连接到V SS 。 当BINARY /DECADE输入为高电平时,完...

发表于 11-02 19:20 •104次 阅读

CD4020B,CD4024B和CD4040B是纹波进位二进制计数器。所有计数器阶段都是主从触发器。计数器的状态对每个输入脉冲的负转变进行一次计数; RESET线上的高电平将计数器重置为全零状态。输入脉冲线上的施密特触发器动作允许无限制的上升和下降时间。所有输入和输出均经过缓冲。 CD4020B和CD4040B型采用16引脚密封双列直插式陶瓷封装(F3A后缀),16引脚双列直插塑料封装(E后缀),16引脚小外形封装(NSR后缀)和16引脚薄收缩小外形封装(PW和PWR后缀)。 CD4040B型还提供16引脚小外形封装(M和M96后缀)。 CD4024B类型采用14引脚密封双列直插陶瓷封装(F3A后缀), 14引脚双列直插塑料封装(E后缀),14引脚小外形封装(M,MT,M96和NSR后缀),以及14引脚薄型收缩小外形封装(PW和PWR后缀) 。 特性 中速操作 完全静态操作 缓冲输入和输出 100%测试20 V时的静态电流 标准化,对称输出特性 完全静态操作 常用复位 5V,10V和15V参数额定值 在整个封装温度范围内,18 V时的最大输入电流为1μA;在18 V和25°C下100 nA 噪声容限(在整个封装温度范围内): V DD = 5 V时为1 V 2 V at ...

发表于 11-02 19:20 •242次 阅读

HC4060-Q1器件包含一个振荡器部分和14个纹波进位二进制计数器级。此振荡器配置可实现RC-或者晶体振荡器电路设计。时钟(CLKI)输入上的高到低转换增加了计数器的值。清除(CLR)输入上的高电平会关闭振荡器( CLKO 变为高电平而CLKO变为低电平)并且将计数器复位清零(所有的Q输出为低电平)。 特性 符合汽车应用要求 2V至6V的宽运行电压范围 输出可驱动多达10个低功耗肖特基晶体管逻辑电路(LSTTL)负载 低功耗,I CC 最大80μA t pd 典型值= 14 ns ±4mA输出驱动(在5V时间) 低输出电流,最大值1μA 实现相移振荡电路(RC) - 或者晶体振荡器电路的设计 参数 与其它产品相比 计数器/算术/奇偶校验功能 Technology Family VCC (Min) (V) VCC (Max) (V) Bits (#) Voltage (Nom) (V) F @ Nom Voltage (Max) (Mhz) ICC @ Nom Voltage (Max) (mA) tpd @ Nom Voltage (Max) (ns) IOL (Max) (mA) IOH (Max) (mA) Function Type Rating Operating Temperature Range (C) Pin/Package var ...

发表于 10-16 10:08 •100次 阅读

最后

以上就是狂野美女最近收集整理的关于用74ls90组成二十四进制计数器_尘埃粒子计数器的工作原理和应用分析的全部内容,更多相关用74ls90组成二十四进制计数器_尘埃粒子计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复