一、 实验要求

1. 理解触发器和计数器的概念。

2. 完成触发器(D型)、计数器(递增、递减)以及层次化特征的低频计数器的设计、仿真与实现。

二、 实验过程步骤

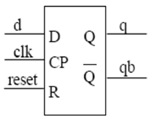

1、设计模块1:异步复位的D触发器d_ff

a.模块功能要求

在数字电路中,异步复位的上升沿D触发器的逻辑电路符号如下图所示,其功能表如下表所示。其工作原理为:只要复位控制端口的信号有效(为0),D 触发器就会立即进行复位操作,与时钟信号无关。当复位端置1时,在时钟信号的上升沿到来时,输入端口D的数据将传递给输出端口Q和输出端口~Q。

| R | D | CP | Q | ~Q |

| 0 | × | 上升沿 | 0 | 1 |

| 1 | × | 0 | 保持 | 保持 |

| × | 1 | 保持 | 保持 | |

| 0 | 上升沿 | 0 | 1 | |

| 1 | 上升沿 | 1 | 0 |

b.实验步骤

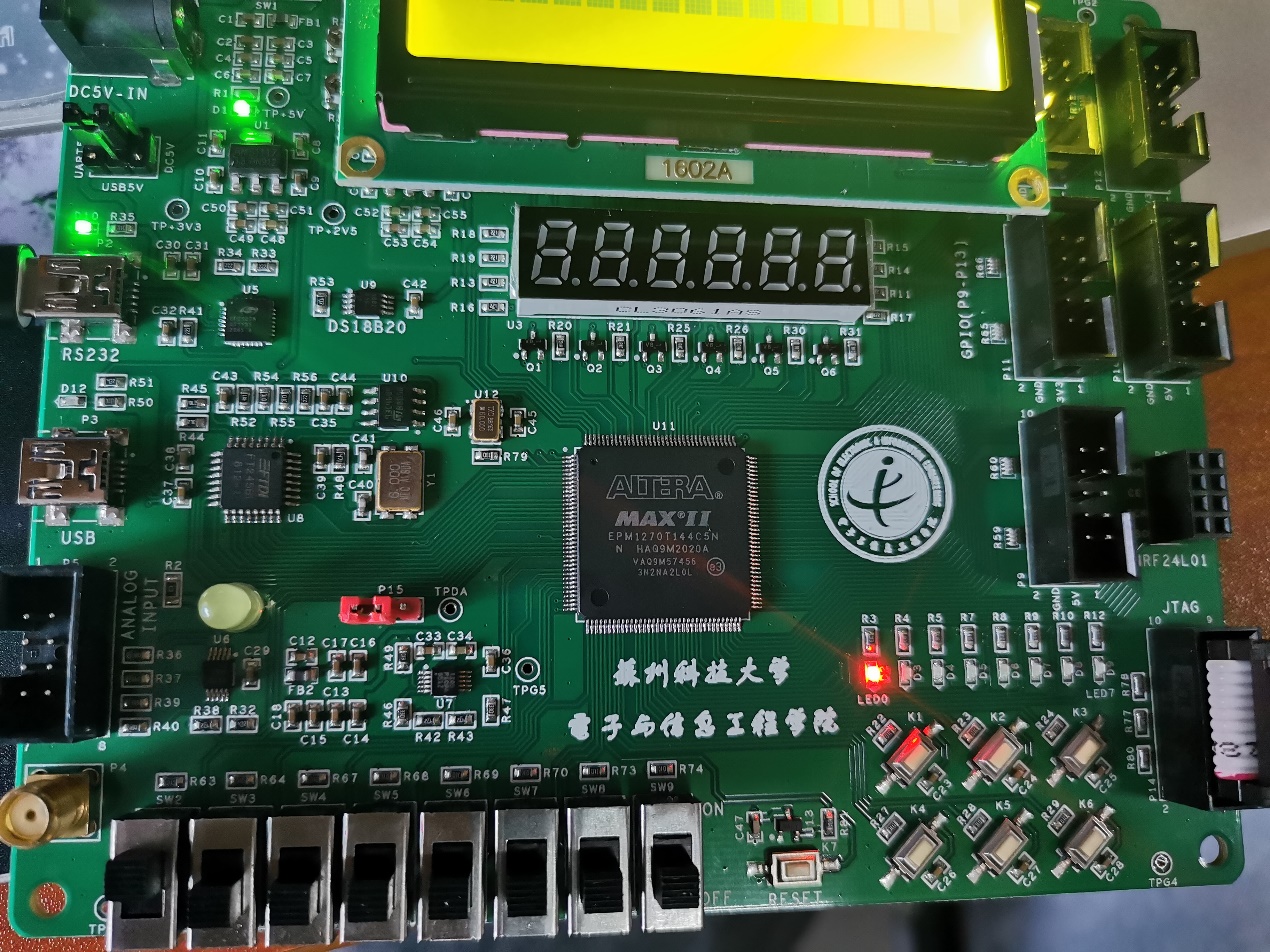

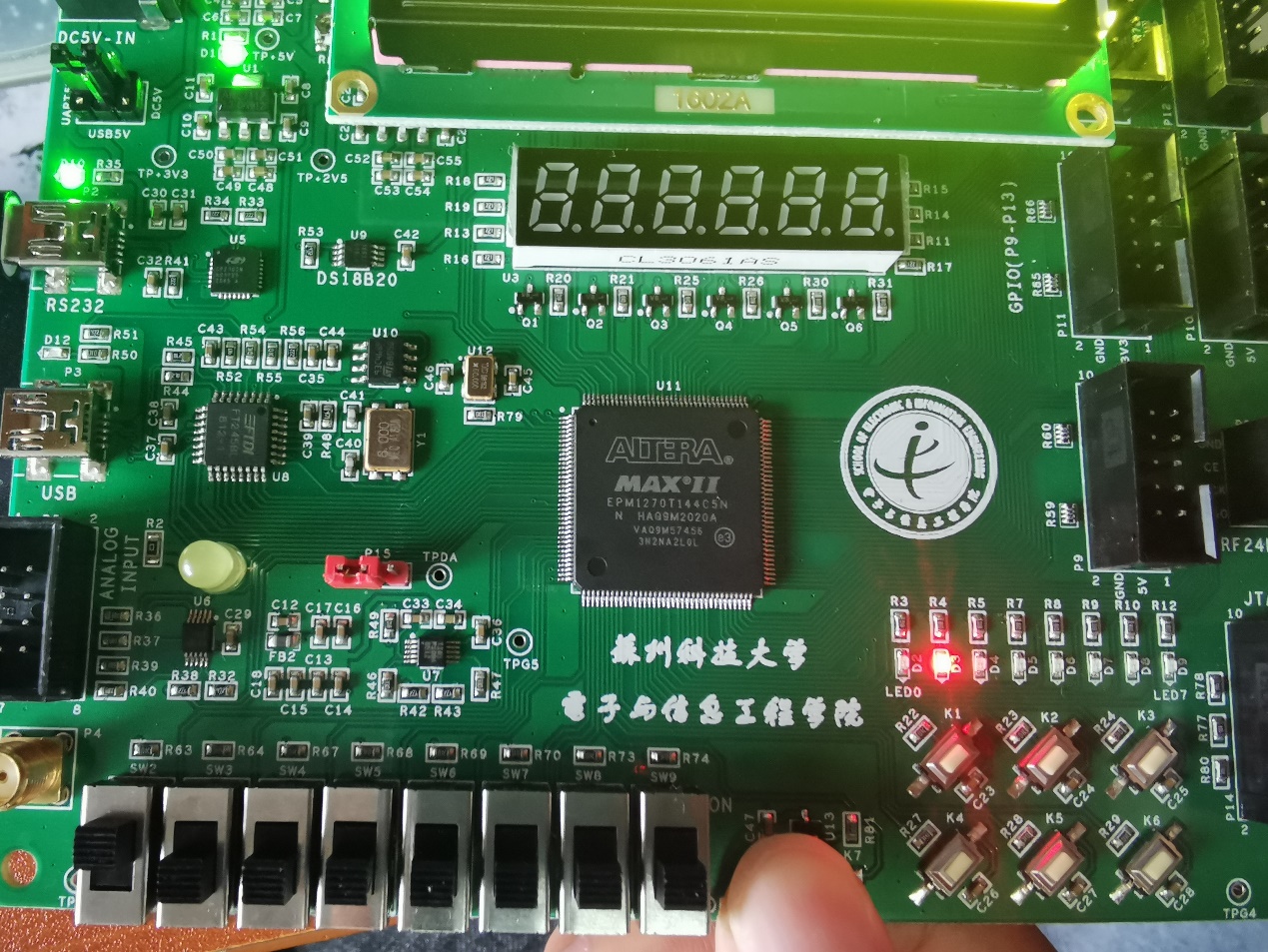

(1)利用wizard新建项目,所选器件为MAX II 系列型号为EPM1270T144C5N的器件。

(2)新建Verilog文件,名称与模块名一致,保存为d_ff.v。程序内容如下:

module d_ff(clk, reset, d, q, qb);

input clk, reset, d;

output q, qb;

reg q;

assign qb=~q;

always@(posedge clk or negedge reset)

if(~reset)

q<=1'b0;

else

q<=d;

endmodule(3)将d_ff.v设为顶层实体后编译,纠错直至编译成功。

(4)新建仿真文件Vector Waveform File,保存为d_ff.vmf。在左侧节点区右击,Insert→Insert Node or Bus→Node Finder,Filter一栏选中“所有管脚”后,点击List,再点击全选,将左侧所有节点全部添加至右侧Selected Nodes窗口中。

(5)首先根据仿真需求,在Edit→End Time中设置所需仿真时间。本实验中设为3us。Clk信号设为周期为160ns的时钟信号,结尾处置零。设置若干复位信号测试复位功能。为体现时钟信号上升沿对D触发器的控制,三个D=1出现的时间分别设置在clk信号的上升沿处、提前上升沿10ns处以及提前上升沿40ns处。

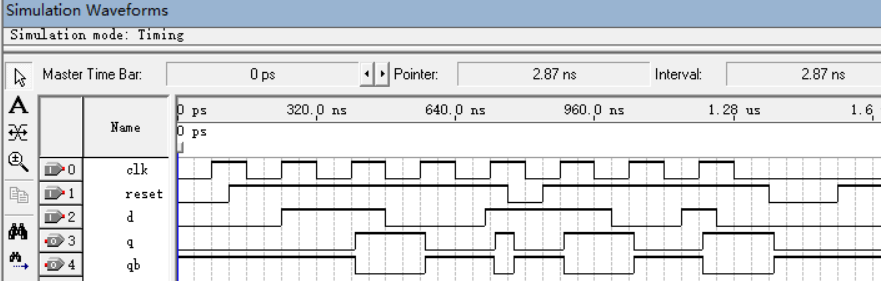

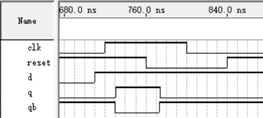

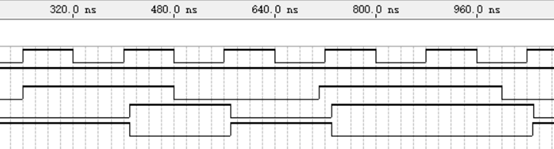

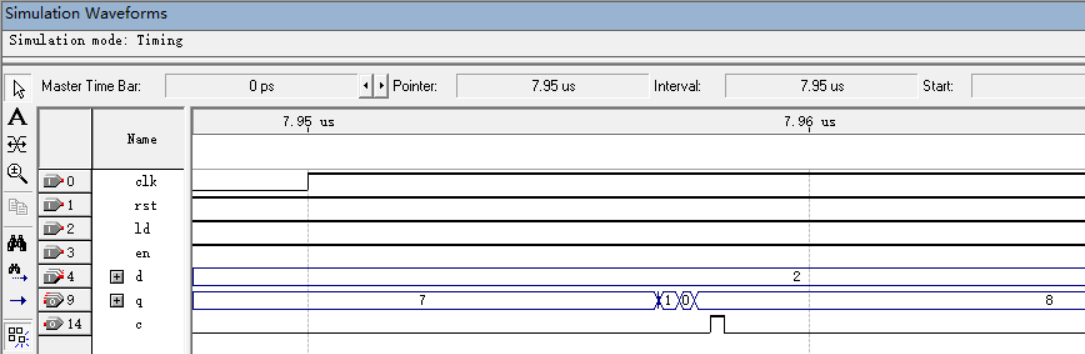

(6)点击Processing→Simulator Tool,打开d_ff.vmf文件,先点击Start,仿真成功后再点击Report,仿真波形输出如下图所示。

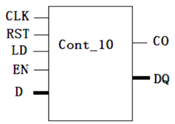

2、设计模块2:通用十进制计数器cnt10

a.模块功能要求

由于实验板上晶振频率太高,对时钟信号直接计数人眼无法直接观察,为此需要对时钟信号进行分频,使频率变为1Hz之后再计数可直接观察计数过程。为了使得计数和分频均基于同一个计数器来实现,需要设计一个通用的十进制计数器,其计数方式为0,1,2,…8,9,0,…,同时须具有复位、置数及维持等功能。通用十进制计数器的符号及功能表如下图所示。

| CLK | RST | LD | EN | 功能 |

| × | 0 | × | × | 异步复位 |

| 上升沿 | 1 | 0 | × | 同步置数 |

| 上升沿 | 1 | 1 | 0 | 维持 |

| 上升沿 | 1 | 1 | 1 | 计数 |

b.实验步骤

(1)新建Verilog文件,名称与模块名一致,保存为cnt10.v。程序内容如下:

module cnt10(clk,rst,ld,en,d,q,c);

input clk,rst,ld,en;

input [3:0]d;

output [3:0]q;

output c;

reg [3:0]q;

assign c= q[3] & q[0] & en;

always@(posedge clk or negedge rst)//时钟上升沿有效,复位下降沿有效

if(~rst)

q<=4'b0000; //rst=0时异步复位

else if(~ld)

q<=d;

//ld=0时同步置数

else if(en)

//en=1时计数

begin

if(q[3] & q[0]) //q=4’b1001(十进制为9)时,q置零,重新从0开始计数

q<=4'b0000;

else

q<=q + 1'b1;

end

endmodule

(2)将cnt10.v设为顶层实体后编译,纠错直至编译成功。

(3)新建仿真文件Vector Waveform File,保存为cnt10.vmf,将所有节点全部添加至窗口中。

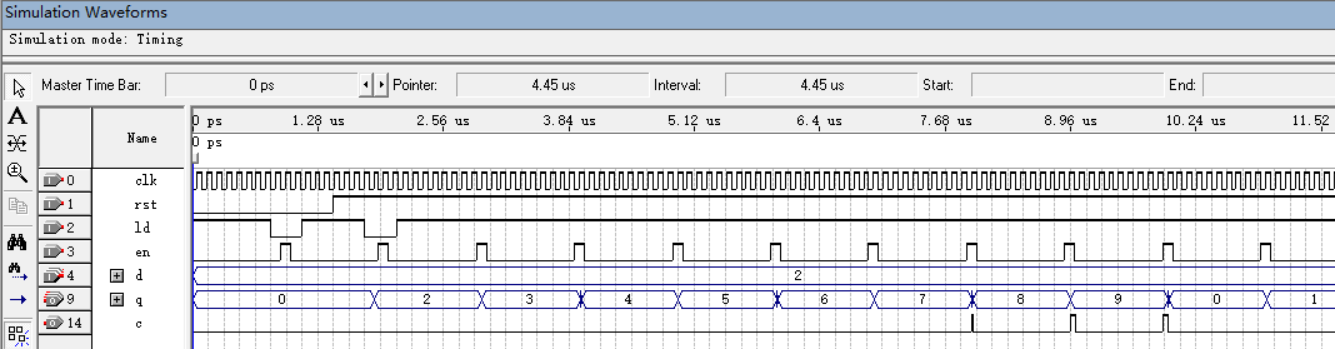

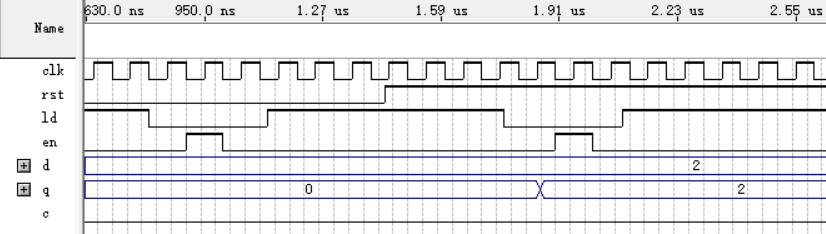

(4)首先根据仿真需求,在Edit→End Time中设置所需仿真时间。本实验中设为100us。Clk设为周期为100ns的时钟信号。Rst和ld端均为低电平有效,在开头部分置0,测试计数器的复位及置数功能。En为控制计数的输入端,设为周期为1us,占空比为10%的clock信号。D的初始值设为2。

(5)点击Processing→Simulator Tool,打开cnt10.vmf文件,Mode选择Timing。先点击Start,仿真成功后再点击Report,仿真波形输出如下图所示。

3、设计模块3:分频器div_mode

(1)新建Verilog文件,名称与模块名一致,保存为div_mode.v。程序内容如下:

module div_mode(clk,rst,en,co_20us,co_200us,co_1s);

input clk,rst,en;

output co_20us,co_200us,co_1ms;

wire en1,en2,en3,en4,en5,en6,en7,en8;

wire [3:0]q0,q1,q2,q3,q4,q5,q6,q7;

assign co_20us=en2;

assign co_200us=en3;

assign co_1s=en7 | en6 & q7[2] & ~(q7[1] | q7[0]);//q7=b'100,fifth time

//co_1ms=en4 | en3 & q4[2] & ~(q4[1] | q4[0]);

cnt10 U0(clk,rst,1'b1,en,4'b0000,q0,en0);//5M=200ns

cnt10 U1(clk,rst,1'b1,en0,4'b0000,q1,en1);//2us

cnt10 U2(clk,rst,1'b1,en1,4'b0000,q2,en2);//20us

cnt10 U3(clk,rst,1'b1,en2,4'b0000,q3,en3);//200us

cnt10 U4(clk,rst,1'b1,en3,4'b0000,q4,en4);//2ms

cnt10 U5(clk,rst,1'b1,en4,4'b0000,q5,en5);//20ms

cnt10 U6(clk,rst,1'b1,en5,4'b0000,q6,en6);//200ms

cnt10 U7(clk,rst,1'b1,en6,4'b0000,q7,en7);//2s

endmodule(2)将div_mode.v设为顶层实体后编译,纠错直至编译成功。

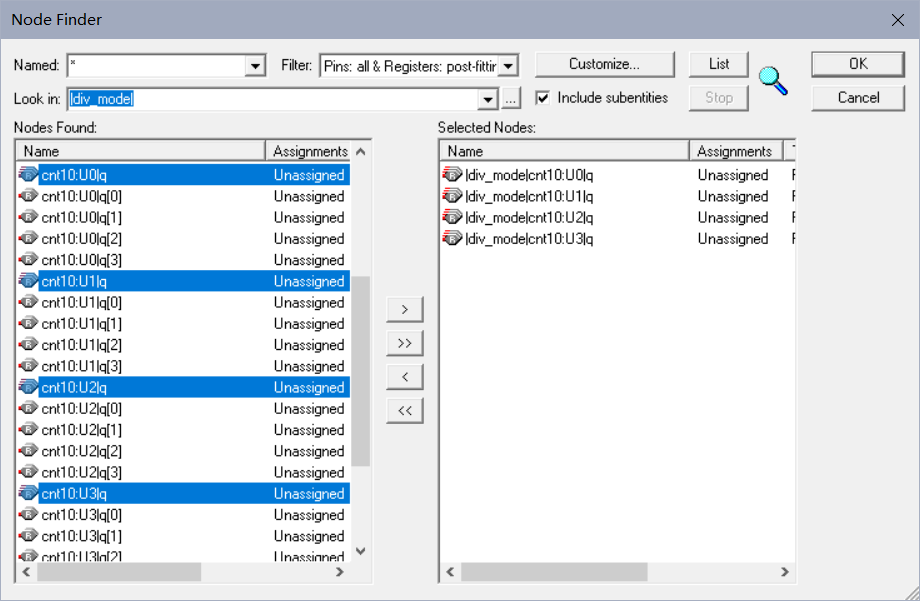

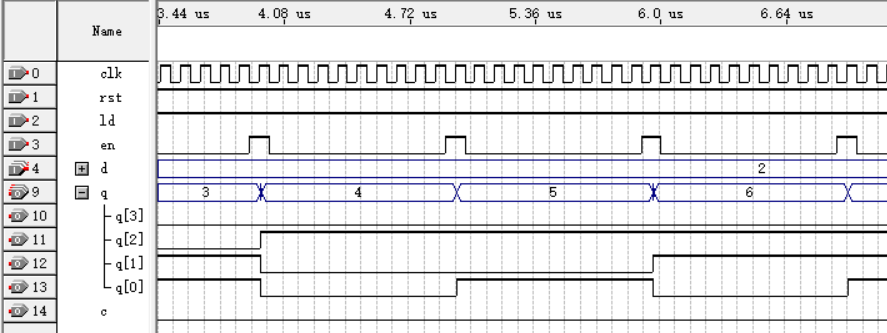

(3)新建仿真文件Vector Waveform File,保存为div_mode.vmf。在Filter一栏选中“所有管脚”后,将所有节点全部添加至窗口中。再把Filter一栏改成“Pins:all®istors”后,选中U0-U3管脚将其加入,如下图所示。

(4)首先根据仿真需求,在Edit→End Time中设置所需仿真时间。本实验中设为5ms。然后将clk设为周期为100ns的clock信号,en设置为全1,上电复位设置好。

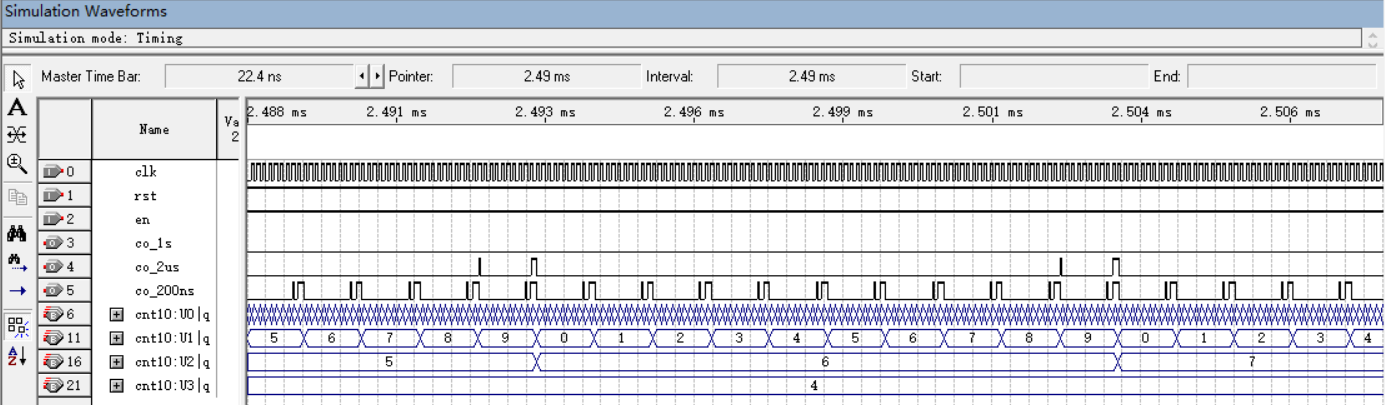

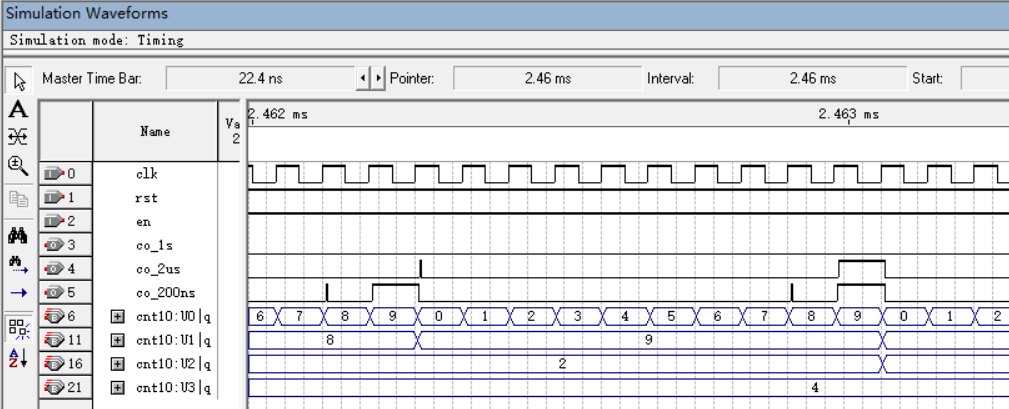

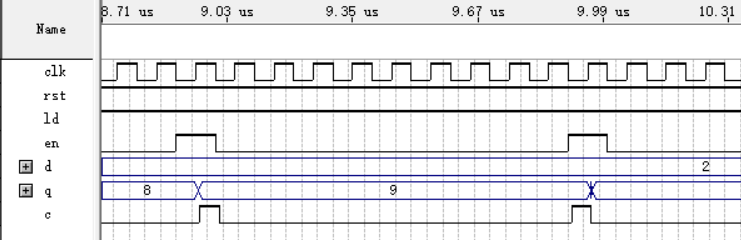

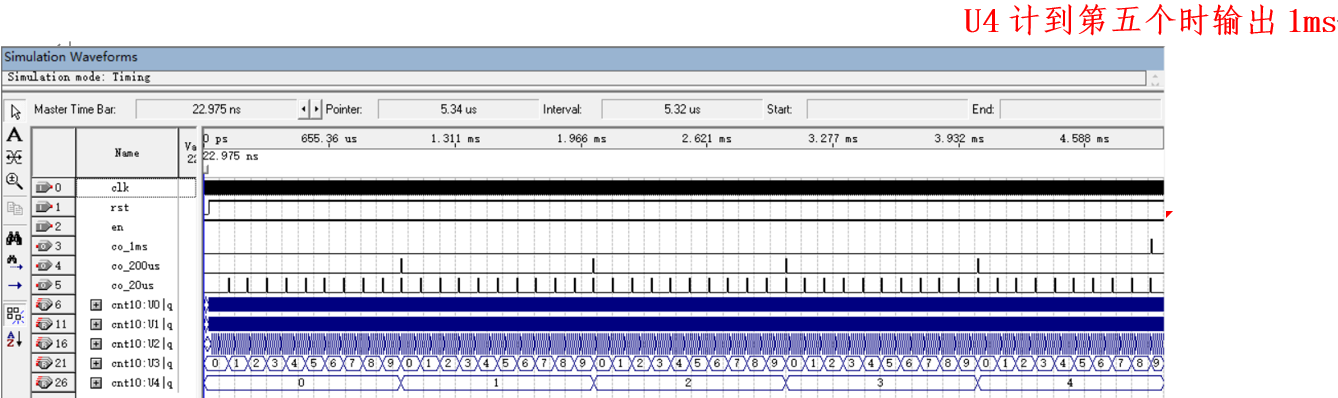

(5)点击Processing→Simulator Tool,打开div_mode.vmf文件,Mode选择Timing。先点击Start,仿真成功后再点击Report,仿真波形输出如下图所示。

三、 实验结果分析总结

1、模块功能仿真结果分析总结

(1)模块1:异步复位的D触发器d_ff

异步复位D触发器的reset信号为0时,输出信号Q立即复位,不受时钟信号的影响。复位响应延迟约为13ns,如下图所示。

若D=1与clk的上升沿同时到来,该周期内无输出。若D提前clk上升沿10ns变成1,则该上升沿处有输出Q=1。由于芯片的传输延迟效应,Q产生1的时刻比clk上升沿迟了10ns。效果如下图所示。

clk信号消失后,不论D的输入信号为何,输出信号Q始终保持不变。

(2)模块2:通用十进制计数器cnt10

输入端优先级:rst>ld>en。当rst=0时,ld、en无效,计数器处于复位状态;当rst=1,ld=0时,en无效,计数器处于置数状态,下一个clk上升沿处将d中的数直接置入q中,效果如下图所示:

在rst=1,ld=1的情况下,当en=1时,计数器处于计数状态;当en=0时,计数器维持。

当en、q[3]、q[0]都为1时,即计数计到9时的开头结尾输出c=1。

当en、q[3]、q[0]都为1时,即计数计到9时的开头结尾输出c=1。

干扰信号

干扰信号

(3)模块3:分频器div_mode

cnt10 U0(clk,rst,1'b1,en,4'b0000,q0,en0);//200ns <= 芯片晶振频率f=5M

cnt10 U1(clk,rst,1'b1,en0,4'b0000,q1,en1);//2us

cnt10 U2(clk,rst,1'b1,en1,4'b0000,q2,en2);//20us

cnt10 U3(clk,rst,1'b1,en2,4'b0000,q3,en3);//200us

cnt10 U4(clk,rst,1'b1,en3,4'b0000,q4,en4);//2ms

cnt10 U5(clk,rst,1'b1,en4,4'b0000,q5,en5);//20ms

cnt10 U6(clk,rst,1'b1,en5,4'b0000,q6,en6);//200ms

cnt10 U7(clk,rst,1'b1,en6,4'b0000,q7,en7);//2s如需产生1s输出,则co_1s=en7 | en6 & q7[2] & ~(q7[2] | q7[0]),即q7=100,计到第五个200ms时输出。

如需产生1ms输出,则co_1ms=en4 | en3 & q4[2] & ~(q4[1] | q4[0]),即q4=100,计到第五个200us时输出。

2、模块功能测试记录与分析总结

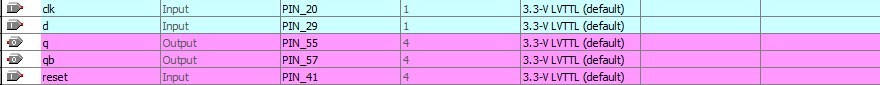

(1)异步复位的D触发器管脚分配如下表:

下图所示为,置数端d设为1时,q输出为1,q’输出为0。

下图所示为,按下复位键后,q变为0,q’变为1。

下图所示为,按下复位键后,q变为0,q’变为1。

(2)通用十进制计数器与分频器实验结果

由于芯片晶振频率约为5MHz,即一个时钟周期约为200ns,人手控制的一个en信号过长,期间已经计数无数次,人眼无法观测,故板子上无效果。

往期数字系统设计专栏文章:

- 简单逻辑电路设计:与非门/逻辑门

- 组合逻辑电路设计:4-2线优先编码器/2-4线译码器/比较器/全加器

最后

以上就是老迟到楼房最近收集整理的关于【数字系统】时序逻辑电路设计:异步复位D触发器/十进制计数器/分频器 Quartus II 环境/Verilog HDL语言/编程+仿真+开发板/FPGA/CPLD/EDA的全部内容,更多相关【数字系统】时序逻辑电路设计:异步复位D触发器/十进制计数器/分频器内容请搜索靠谱客的其他文章。

发表评论 取消回复