引言

低速通信目前搞过 UART串口通信、IIC通信。其实 SPI 也算是中低速(有时也可以用作高速通信)串行通信的范畴,但是一直还没真正实现过,所以此系列就 SPI的协议以及FPGA设计作几篇博客记录。欢迎订阅关注~

SPI 标准协议 x1模式

SPI 是一种事实标准,由Motorola开发,支持全双工通信,并没有一个官方标准。已知的有的器件SPI已达到50Mbps,如果时序满足,FPGA的SPI通信速率可以达到100Mbps以上。具体到产品中SPI的速率主要看主从器件SPI控制器的性能限制。

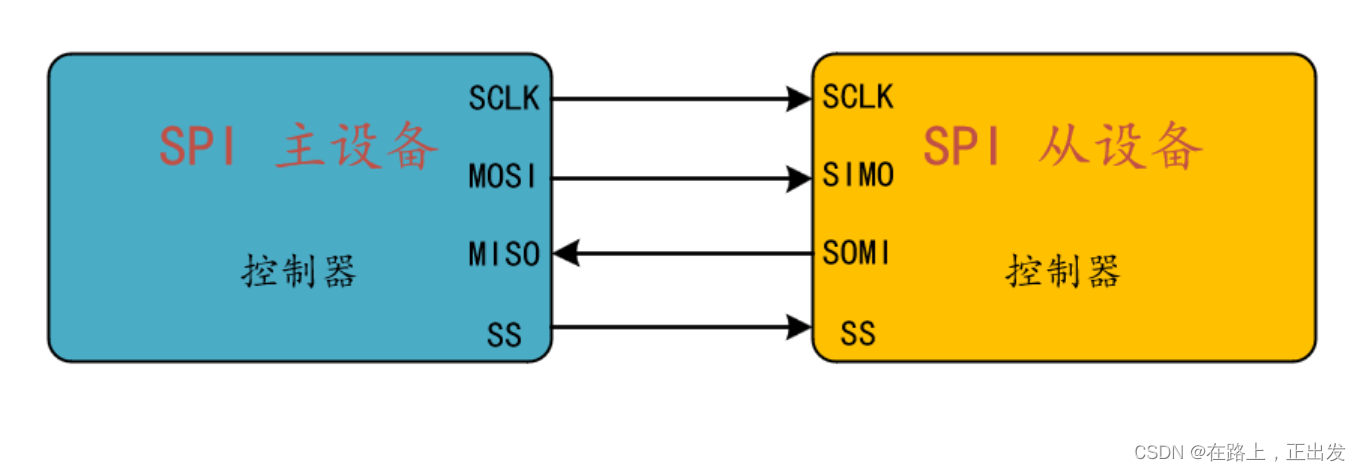

设备通信框图

SPI通信主设备:

SCLK:SPI 通信时钟,源:SPI 主设备。

MOSI:SPI 主设备控制器数据发送,源:SPI 主设备。Master Out Slave In

MISO:SPI 主设备控制器数据接收,源:SPI 从设备。Master In Slave Out

SS:从设备片选,源:SPI 主设备。Slave Select

SPI通信从设备:

SCLK:SPI 通信时钟,源:SPI 主设备。

SIMO:SPI 从设备控制器数据接收,源:SPI 主设备。Slave In Master Out

SOMI:SPI 从设备控制器数据发送,源:SPI 从设备。Slave Out Master In

SS:从设备片选,源:SPI 主设备。Slave Select

SPI 时序协议

SPI 串行同步时钟可以设置为不同的极性(Clock Polarity,CPOL)与相位(Clock Phase,CPHA)

CPOL(时钟极性)

决定在总线空闲时,同步时钟(SCK)信号线上的电位是高电平还是低电平。当时钟极性为0时(CPOL=0), SCK信号线在空闲时为低电平;

当时钟极性为1时(CPOL=1) ,SCK信号线在空闲时为高电平;CPHA(时钟的相位)

对于SPI主控制器决定了数据的更新时刻设计,对于SPI从控制器决定了数据的采样时刻。当时钟相位为0时(CPHA=0),在SCK信号线的第一个跳变沿进行采样;

当时钟相位为1时(CPHA=1),在SCK信号线的第二个跳变沿进行采样;以下我们给出CPOL和CPHA的共计4种情况。

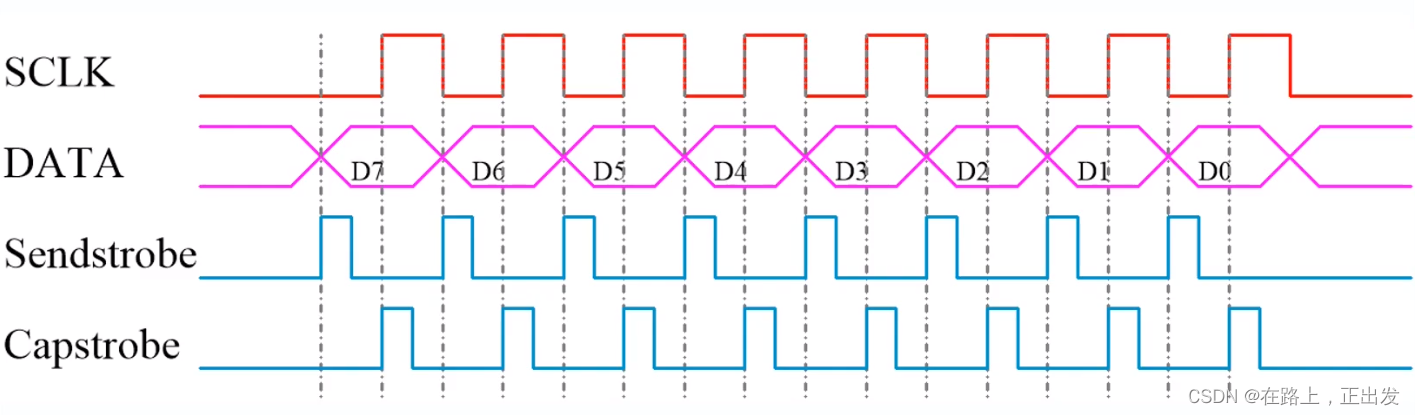

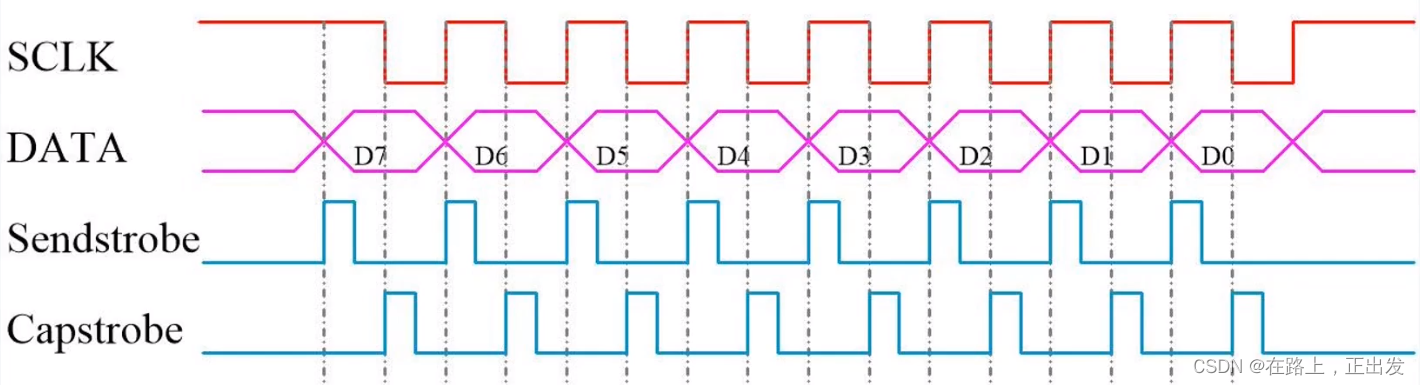

1、CPOL = 0;CPHA = 0;

CPOL=0, CPHA=0默认SCLK为低电平,对于发送方,在对于第1个bit数据提前放到总线,建议提前0.5个SCK周期,对于接收方,数据在第1个SCLK跳变沿采样,并且容易满足时序约束。

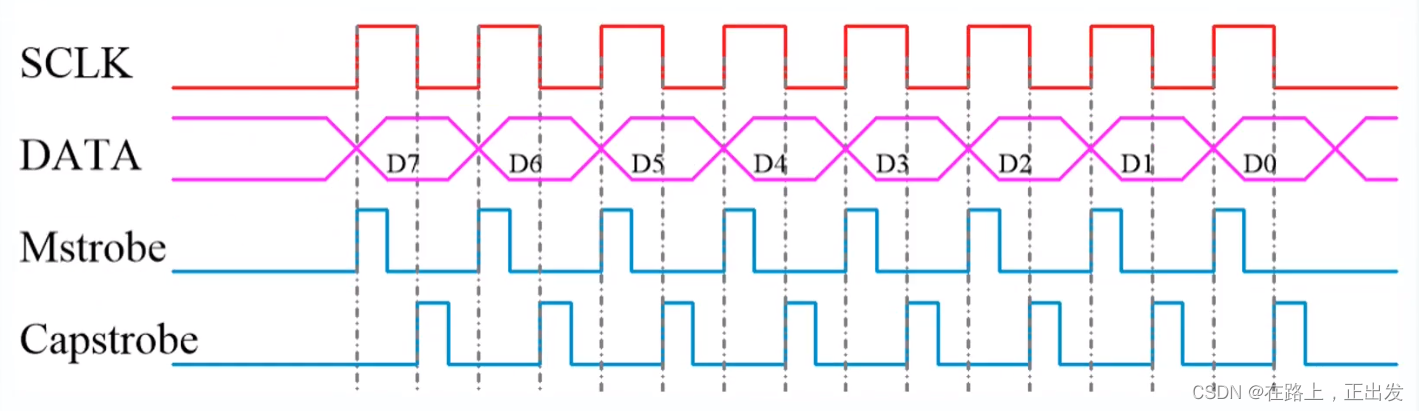

2、CPOL = 0;CPHA = 1;

CPOL=0, CPHA=1默认SCLK为低电平,对于发送方,在第1个SCLK的跳变沿更新(对于第一个bit 数据可以提前放到总线)对于接收方,数据在第2个SCLK跳变沿采样,并且容易满足时序约束。

3、CPOL = 1;CPHA = 0;

CPOL=1,CPHA=0默认SCLK为高电平,对于发送方,在对于第1个bit 数据提前放到总线(建义提前0.5个SCK周期)对于接收方,数据在第1个SCLK跳变沿采样,并且容易满足时序约束。

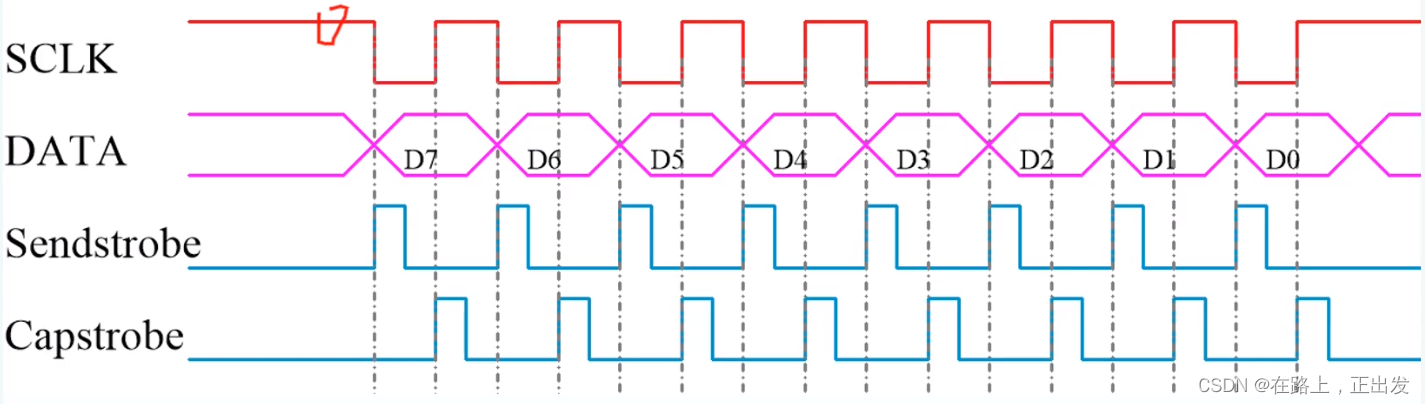

3、CPOL = 1;CPHA = 1;

CPOL=1 CPHA=1默认SCLK为高电平,对于发送方,在第1个SCLK的跳变沿更新(对于第一

个bit数据可以提前放到总线)对于接收方,数据在第2个SCLK跳变沿采样,并且容易满足时序约束。

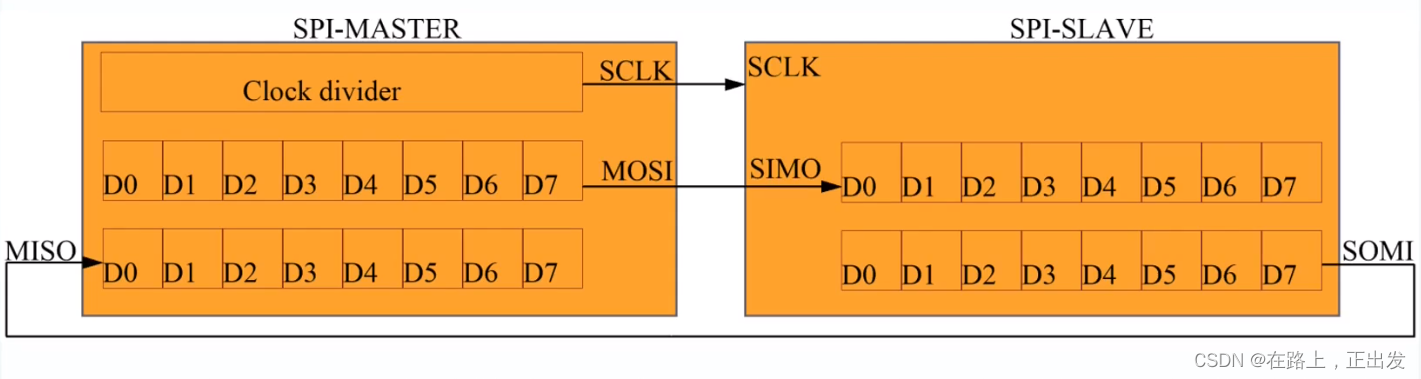

SPI 驱动模型

一个基本的SPIl Master驱动程序至少包含用于产生SCLK的时钟分频单元,发送数据并串移位模块、接收数据串并移位模块;

一个基本的SPI Slave驱动程序至少包含接收数据的串并移位模块,和发送数据的并串转换模块。

目前只先介绍较为基础的标准 SPI 通信协议(x1模式),后续会继续添加更为复杂的模式的基本介绍~

最后

以上就是怡然热狗最近收集整理的关于基于FPGA的 SPI通信 设计(1)引言SPI 标准协议 x1模式的全部内容,更多相关基于FPGA的内容请搜索靠谱客的其他文章。

发表评论 取消回复