取一个信号的上升沿或下降沿信号,可以通过将信号delay后,然后将原信号和delay信号,通过不同的与非操作,获取上升沿信号或下降沿信号:

阶段一:

reg delay; // delay信号

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= orig; // orig是原信号

wire pos_signal = orig && ( ~delay ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~orig ) && delay; // 原信号下降沿位置处产生的pulse信号

阶段二:

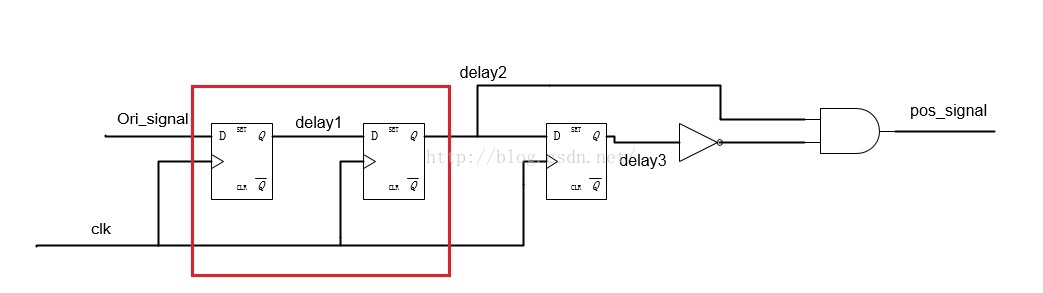

上述操作会存在亚稳态问题,并且得到的上升沿信号pos_signal和下降沿信号neg_signal无法被原采样时钟clk采样。正确做法是,先将原信号用采样时钟delay 2次(打两拍),得到和采样时钟同时钟域的信号delay2,然后再按上述方法获取上升沿和下降沿信号,这时得到的上升沿或下降沿就可以被原采样时钟采样。

例句如下:

reg ori_signal;// 需取上升沿或下降沿的原信号

reg delay1;

reg delay2;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay1 <= 0;

else

delay1 <= ori_signal;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay2 <= 0;

else

delay2 <= delay1; // delay2 已与clk同域

reg delay3;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay3 <= 0;

else

delay3 <= delay2;

wire pos_signal = delay2 && ( ~delay3 ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~delay2 ) && delay3; // 原信号下降沿位置处产生的pulse信号

上升沿电路如下:

注意:前两个触发器的运用就是起同步作用,将某个信号同步到采样时钟域,以后要重点注意使用。

阶段三:

用阶段二的语句会比较繁琐,可以用下述语句简化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信号

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信号下降沿位置处产生的pulse信号

————————————————

最后

以上就是昏睡煎蛋最近收集整理的关于verilog中判断上升沿和下降沿的程序的全部内容,更多相关verilog中判断上升沿和下降沿内容请搜索靠谱客的其他文章。

发表评论 取消回复