同步复位进行设计

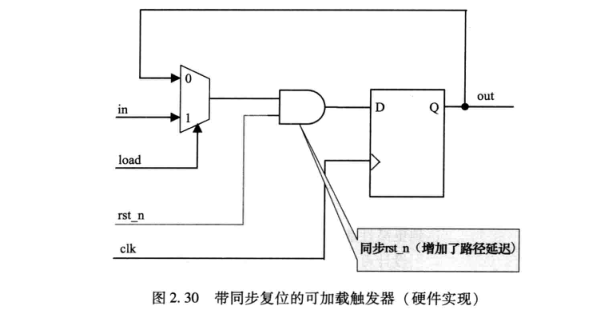

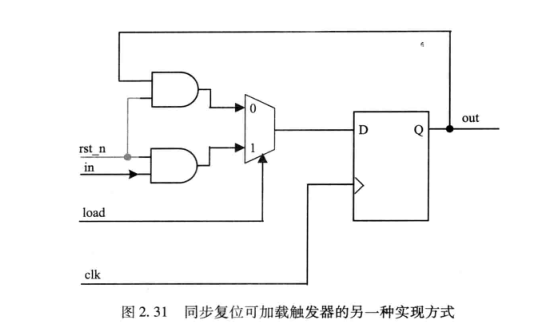

带同步复位的可加载触发器硬件实现。

使用同步复位会出现一个问题:综合工具无法分辨复位信号和其他数据信号。 综合工具可能综合出下图所示的电路结构。

**在门级仿真的时候可能出现的问题:**当rst_n信号为低时,mux的输入都为低。然而倘若加载信号load为未知态时,那么mux的输出将为未知态。实际电路没有此问题。

同步复位的优点

- 同步复位一般能确保电路100%同步的。

- 同步复位会综合为更小的触发器,特别在该复位信号被触发器的输入逻辑门控时。

- 同步复位确保复位只发生在有效时钟沿。时钟可以作为过滤掉复位毛刺的手段。

同步复位的缺点

- 同步复位可能需要一个脉冲展宽器,以保证复位信号能出现在时钟有效沿处。在进行多时钟设计时,也可以用一个小计数器来保证具有指定周期的复位脉冲宽度。

- 同步复位需要时钟信号以复位信号。在出于节省功耗的目的而使用门控时钟时,就可能出现问题。在复位信号发生时,时钟可能关闭。这种情况下只能使用异步复位,并在时钟恢复前移除复位信号。

异步复位进行设计

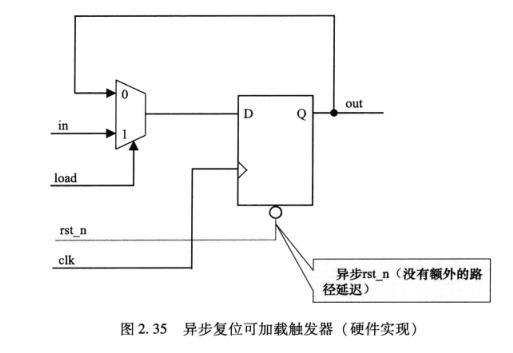

异步复位可加载触发器的硬件实现。

异步复位的优点

- 保证数据路径上是干净的。

- 复位不依赖于时钟信号。

异步复位的缺点

- 在DFT时,如果异步复位信号不能直接被I/O引脚驱动,就必须将异步复位线路与复位驱动器断开以保证DFT扫描和测试的正确。

- 产生复位信号不存在问题,但是撤离时就出现了问题。如果异步复位在触发器时钟有效沿附近释放,触发器的输出就会进入亚稳态。

- 异步复位一般由板级或系统复位所产生的噪声或毛刺引发的伪复位。需要设计毛刺过滤器来消除复位电路上的毛刺影响。

异步复位同步释放

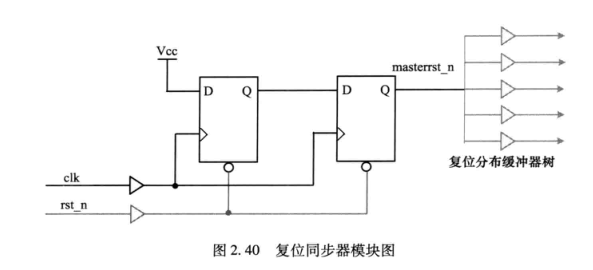

移除系统中的异步复位会使芯片进入不稳定的未知状态。因此可以采用异步复位同步你释放电路解决此问题。

需要两级触发器进行同步。

这里面关键的分析::第二个触发器用于移除由于异步撤销的复位信号与时钟上升沿过于接近所导致的亚稳态。复位同步器的第一个触发器有潜在亚稳态风险的原因是其输入固定为高电平,输出异步复位为0并且复位可能在触发器规定的恢复时间内移除(复位可能与同一个触发器的时钟输入上升沿过于接近)。

最后

以上就是快乐歌曲最近收集整理的关于《硬件架构的艺术》学习笔记(2.3)---复位信号设计同步复位进行设计异步复位进行设计异步复位同步释放的全部内容,更多相关《硬件架构内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复