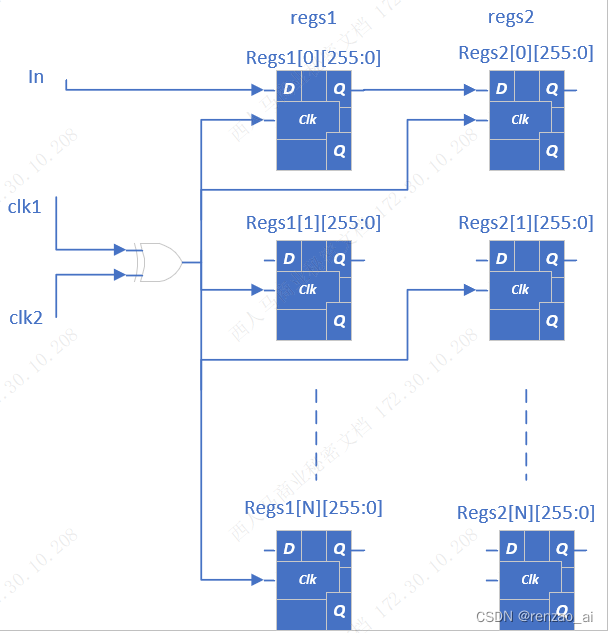

逻辑结构

regs1[i] = regs1[0]+regs1[1] + … + regs1[i-1] + regs2[0]+regs2[1] + … + regs21[i-1]

regs2[i] = regs1[0]+regs1[1] + … + regs1[i-1] + regs2[0]+regs2[1] + … + regs21[i-1] +regs1[i]

看似复杂,主要为了可以制造出违例。

代码

typedef logic [255:0] l256;

parameter times = 5;

module dut(

input clk1,

input clk2,

input rstn,

input l256 in,

output logic out

);

l256 regs1 [times];

l256 regs2 [times];

logic clk_xor;

logic rstn_sync1, rstn_sync;

l256 tmp_regs;

XOR2X1AS9 u_xor(.O(clk_xor),.I1(clk1),.I2(clk2));

always@(posedge clk_xor or negedge rstn)

if (!rstn) begin

rstn_sync1 <= 1'b0;

rstn_sync <= 1'b0;

end

else begin

rstn_sync1 <= 1'b1;

rstn_sync <= rstn_sync1;

end

always@(posedge clk_xor or negedge rstn_sync)

if(!rstn_sync) begin

for (int i = 0; i<times; i++) begin

regs1[i] <= {256{1'b0}};

regs2[i] <= {256{1'b0}};

end

end

else begin

for(int i=0;i<times; i++) begin

tmp_regs = 0;

if(i==0 ) begin

regs1[i] <= in;

regs2[i] <= regs1[i];

end

else begin

for(int j=1; j<i;j++)

tmp_regs = tmp_regs + regs1[j] + regs2[j];

regs1[i] <= tmp_regs;

regs2[i] <= tmp_regs + regs1[i];

end

end

end

always@(posedge clk_xor or negedge rstn_sync)

if(!rstn_sync)

out <= 1'b0;

else

out <= ^{regs1[times-1],regs2[times-1]}; // 256 + 256

endmodule

以上为可综合代码。注意tmp_regs = 阻塞赋值。

综合脚本

sh mkdir -p ./work

define_design_lib WORK -path ./work

set_host_options -max_cores 8

set search_path ./

lappend search_path xxx/ccs_db

set synthetic_library [list dw_foundation.sldb]

set target_library xxx_ccs.db

set link_library "* dw_foundation.sldb $target_library"

set_svf dut.svf

analyze -work WORK -format sverilog non_unate_clocks.sv

elaborate dut -work WORK -update

link

current_design dut

set_dont_touch [get_cells u_xor]

create_clock -name clk1 [get_ports clk1] -period 5

create_clock -name clk2 [get_ports clk2] -period 4

create_generated_clock -name clk1_xor [get_pins u_xor/Z] -source [get_ports clk1]

-master clk1 -divide_by 1 -combinational -add

create_generated_clock -name clk2_xor [get_pins u_xor/Z] -source [get_ports clk2]

-master clk2 -divide_by 1 -combinational -add

compile

return

分析

分析1

Clock Period Waveform Attrs Sources

clk1 5.00 {0 2.5} {clk1}

clk2 4.00 {0 2} {clk2}

Warning: A non-unate path in clock network for clock ‘clk1’

from pin ‘u_xor/O’ is detected. (TIM-052)

Warning: A non-unate path in clock network for clock ‘clk2’

from pin ‘u_xor/O’ is detected. (TIM-052)

违例1

Point Incr Path

clock clk2’ (rise edge) 2.00 2.00

clock network delay (ideal) 0.00 2.00

regs2_reg[3][27]/CK (DFFRBQX1AS9) 0.00 # 2.00 r

regs2_reg[3][27]/Q (DFFRBQX1AS9) 0.19 2.19 f

add_1_root_add_0_root_add_45_2_I3_I5/A[27] (dut_DW01_add_J4_0)

0.00 2.19 f

regs2_reg[4][209]/D (DFFRBQX1AS9) 0.00 4.88 f

data arrival time 4.88

clock clk1’ (rise edge) 2.50 2.50

clock network delay (ideal) 0.00 2.50

regs2_reg[4][209]/CK (DFFRBQX1AS9) 0.00 2.50 r

library setup time -0.06 2.44

data required time 2.44

data required time 2.44

data arrival time -4.88

slack (VIOLATED) -2.44

首先clk2到clk1,不合理。

设置如下

set_clock_groups -name clk1_clk2 -logically_exclusive -group {clk1} -group {clk2}

分析2

Point Incr Path

clock clk1’ (rise edge) 2.50 2.50

clock network delay (ideal) 0.00 2.50

regs2_reg[3][27]/CK (DFFRBQX1AS9) 0.00 # 2.50 r

regs2_reg[3][27]/Q (DFFRBQX1AS9) 0.19 2.69 f

add_1_root_add_0_root_add_45_2_I3_I5/A[27] (dut_DW01_add_J4_0)

regs2_reg[4][209]/D (DFFRBQX1AS9) 0.00 5.38 f

data arrival time 5.38

clock clk1 (rise edge) 5.00 5.00

clock network delay (ideal) 0.00 5.00

regs2_reg[4][209]/CK (DFFRBQX1AS9) 0.00 5.00 r

library setup time -0.06 4.94

data required time 4.94

data required time 4.94

data arrival time -5.38

slack (VIOLATED) -0.44

已经排除了clk1 , clk2之间的错误检查。但是因为non-unate,所以clk1’(即 clk1的反向时钟),会检查clk1,这也是不合理的。

有两个点

(1)non-unate时,timing还是会检查的,

(2)可能不合理,主要是更加严格了。

分析3

先对clk1进行纠正

set_sense -type clock -positive -clocks {clk1} [get_pins u_xor/O]

Point Incr Path

clock clk1 (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

regs2_reg[3][27]/CK (DFFRBQX1AS9) 0.00 # 0.00 r

regs2_reg[3][27]/Q (DFFRBQX1AS9) 0.19 0.19 f

regs2_reg[4][209]/D (DFFRBQX1AS9) 0.00 2.88 f

data arrival time 2.88

clock clk1 (rise edge) 5.00 5.00

clock network delay (ideal) 0.00 5.00

regs2_reg[4][209]/CK (DFFRBQX1AS9) 0.00 5.00 r

library setup time -0.06 4.94

data required time 4.94

data required time 4.94

data arrival time -2.88

slack (MET) 2.06

但是clk2还是有问题

Point Incr Path

clock clk2 (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

regs2_reg[3][27]/CK (DFFRBQX1AS9) 0.00 # 0.00 r

regs2_reg[3][27]/Q (DFFRBQX1AS9) 0.19 0.19 f

add_1_root_add_0_root_add_45_2_I3_I5/A[27] (dut_DW01_add_J4_0)

0.00 0.19 f

clock clk2’ (rise edge) 2.00 2.00

clock network delay (ideal) 0.00 2.00

regs2_reg[4][209]/CK (DFFRBQX1AS9) 0.00 2.00 r

library setup time -0.06 1.94

data required time 1.94

data required time 1.94

data arrival time -2.88

slack (VIOLATED) -0.94

分析4

对clk2进行纠正

set_sense -type clock -positive -clocks {clk2} [get_pins u_xor/O]

regs2_reg[4][209]/D (DFFRBQX1AS9) 0.00 2.88 f

data arrival time 2.88

clock clk2 (rise edge) 4.00 4.00

clock network delay (ideal) 0.00 4.00

regs2_reg[4][209]/CK (DFFRBQX1AS9) 0.00 4.00 r

library setup time -0.06 3.94

data required time 3.94

data required time 3.94

data arrival time -2.88

slack (MET) 1.06

最后

以上就是羞涩柜子最近收集整理的关于non-unate clock通过DC综合工具演示逻辑结构代码分析的全部内容,更多相关non-unate内容请搜索靠谱客的其他文章。

发表评论 取消回复