视频采集ADC(常用的有AD9824,AD9945,AD9945以及TI公司的VSP系列)是一系列完整的混合信号集成电路,包含与摄像机中电荷耦合器件(CCD)成像器输出信号处理有关的所有关键特性,数码相机,安全摄像机,或其他类似的应用。视频采集ADC包括相关双采样器(CDS),可编程增益放大器(PGA),模数转换器(ADC),输入钳位,光学黑(OB)电平钳位环路,串行接口,时序控制和参考电压发生器。建议在CCD输出和视频采集ADC ,CCDIN输入之间放置一个片外发射极跟随器。所有功能和参数(如PGA增益控制,操作模式和其他设置)均可通过串行接口进行更改。当RESET引脚与时钟异步变低时,所有参数都将复位为默认值。

视频采集ADC还提供双通道通用8位数模转换器(DAC)。该DAC可应用于各种应用,如CCD偏置控制,光圈控制等

CDS双采样

CCD图像传感器的输出信号在一个像素周期内被采样两次:一次在参考间隔采样,并且再次在数据间隔采样。减去这两个采样可提取像素视频信息,并消除两个区间常见(或相关)的噪音。因此,通过CDS降低CCD输出信号上存在的复位噪声和低频噪声非常重要。

输入钳位

缓冲CCD输出电容耦合到视频采集ADC。输入钳位的目的是恢复交流耦合所丢失的输入信号的直流分量,并为CDS建立所需的直流偏置点。 图4的框图也显示了输入钳位。 在虚拟像素间隔期间,输入电平被钳位到内部参考电压REFP(1.5 V)。 更具体地说,当CLPDM和SHP都有效时,钳位功能变为有效。

器件上电后,输入电容钳位电压不会被充电。 为了快速充电钳位电压,视频采集ADC提供了一个升压电路。

16bitADC

视频采集ADC包含一个高速16位ADC。 该ADC采用全差分流水线架构进行校正。 这种结合了ADC校正的架构对于实现较小信号电平的较好线性是非常有利的,这是由于在满量程范围内的特定点处倾向于发生大线性误差的结果; 对于低于该特定点的信号电平,线性也得到改善。ADC可在整个满量程范围内确保16位分辨率。

时序驱动

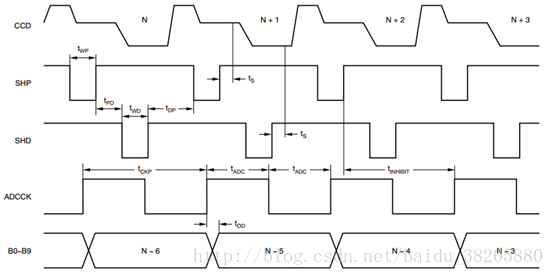

CDS和ADC由SHP和SHD操作,微分定时时钟由片上定时发生器产生。输出寄存器和解码器由ADCCK操作。数字输出数据与ADCCK同步。 CCD信号,SHP,SHD,ADCCK和输出数据之间的时序关系在“时序特性”部分中进行了描述。 CLPOB用于在OB像素间隔期间激活黑电平钳位环路,CLPDM用于在虚拟像素间隔期间激活输入钳位。在待机模式下,ADCCK,SHP,SHD,CLPOB和CLPDM在内部被屏蔽并拉高。

数据输出时序可以通过AFE-Ctrl(2)寄存器进行延迟。基本上,数据输出时序应通过ADCCK时序进行调整,但在需要超出调整范围时才有效。如输入钳位和光学黑电平(OB)环路和OB钳位电平部分所述,CLPOB用于控制自动补偿CCD偏移的OB环路,CLPDM用于将输入钳位电压充电至电容CIN,即连接到CCDIN。为了获得正确的操作,CLPOB和CLPDM应该在计时开始之前立即生效,如以下段落所述。

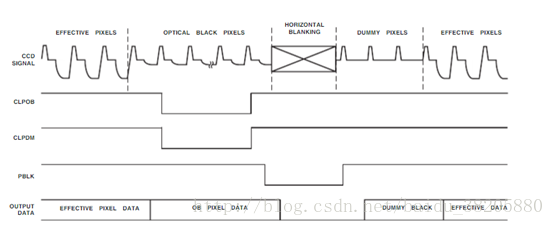

CCD有几个虚拟和OB像素。通常,虚拟像素被放置在行的开始处,并且OB像素被放置在有效像素之后。时序建议适用于CLPDM在伪像素周期内激活,CLPOB在OB像素周期内激活。任何有效期应包括同一时期的虚拟和OB像素。在某些情况下,虚拟像素被定义为“2”或其他一些小值。 视频采集ADC可以用一个很小的虚拟像素值进行操作,但'2'太小。例如,如果CIN输入钳位放电很大,视频采集ADC将无法恢复。在这种情况下,CLPDM可以与CLPOB共享OB像素。尽管较长的CLPOB周期是优选的,但根据情况(诸如OB像素的噪声),理论上大约20个像素足以使稳定操作恢复到正常状态。 CLPDM也需要10到20个像素。如果OB像素只有大约30个像素,则应共享为CLPOB的20像素和CLPDM的10像素。为了获得稳定的OB级别,CLPOB和CLPDM需要在CCD像素的不同部分处于活动状态。

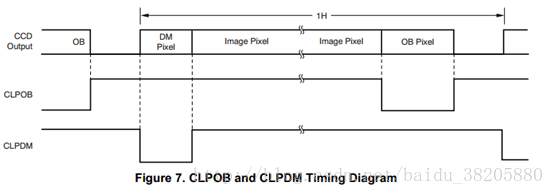

图7显示了CLPOB和CLPDM的时序图。 SHP,SHD,CLPOB,CLPDM和RLOAD的功能在低周期或串行接口默认设置的上升沿有效;每个有效极性可以通过寄存器设置进行选择。

1.CLPOB和CLPDM将覆盖PBLK。 如果重叠CLPDM和/或CLPOB,PBLK不会影响钳位操作。

2. PBLK信号是可选的。

3.数字输出数据在PBLK期间全部为零。输出数据延时为9个DATACLK周期。

最后

以上就是外向导师最近收集整理的关于CCD相机模数转换芯片时序简介的全部内容,更多相关CCD相机模数转换芯片时序简介内容请搜索靠谱客的其他文章。

发表评论 取消回复