一、哪些步骤需要进行仿真

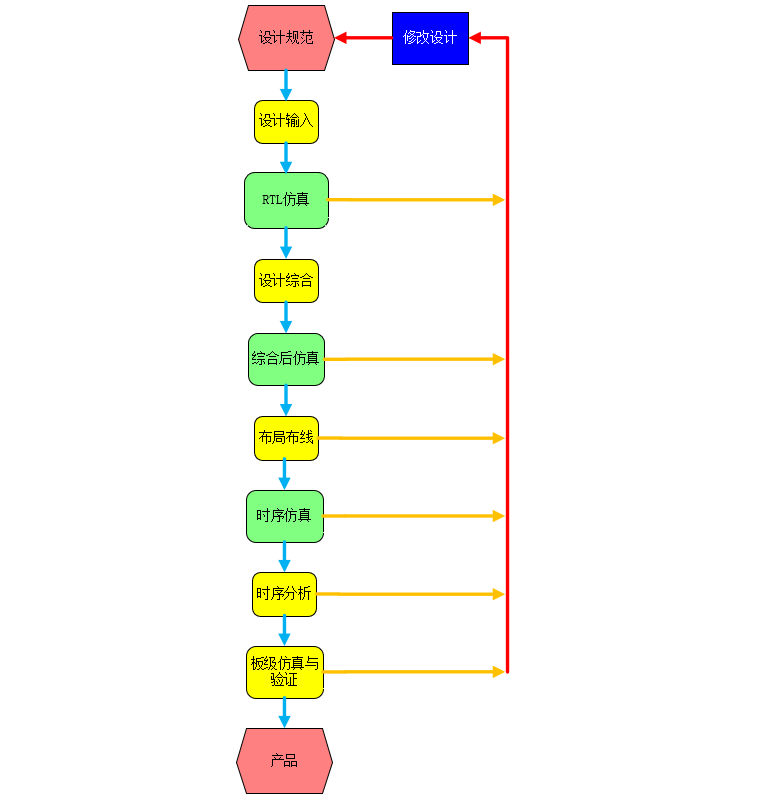

下图是FPGA开发的整个流程,先看一下仿真都出现在哪里。

流程图中绿色的步骤是要进行测试仿真的,即有三个步骤是要进行仿真操作的(有时会省略“综合后仿真”这一步)

1.RTL仿真

也称为综合前仿真、前仿真和功能仿真。

这一步只验证在顶层模块和功能子模块的设计输入完成后,其电路的逻辑功能是否符合设计要求,不考虑门延时和线延时。

2.综合后仿真

综合后仿真加入了门延时。

3.时序仿真

也称为后仿真,在门延时的基础上又加入了线延时。

二、如何编写仿真测试文件

下面以功能仿真为例子,说明测试仿真文件如何编写。

1.首先准备好需要被测模块的Verilog代码

module led_twinkle(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output [1:0] led //LED 灯

);

...... //省略功能部分

endmodule

2.编写TestBench测试仿真文件

在Vivado软件中,在左侧的 Flow Navigator 窗口点击 Add Source, 选择 Add or create simulation sources,点击 Next,点击 Create File, 给测试文件命名,通常格式为 “tb_被测试模块名”,点击OK,点击Finish。

在 Source 栏中的 Simulation Sources 中双击生成的 “tb_被测试模块名” 文件,进行编写。

~timescale 1ns / 1ps //测试时间基本单位为1ns,精度为1ps

module tb_led_twinkle(); //通常起名格式为 tb_被测试模块名

//输入

reg sys_clk;

reg sys_rst_n;

//输出

wire [1:0] led;

//信号初始化,必须有这一步,容易被忽略

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200 //延时200ns

sys_rst_n = 1'b1;

end

//生成时钟,模拟晶振实际的周期时序

always #10 sys_clk = ~sys_clk; //每10ns,sys_clk进行翻转,达到模拟晶振周期为20ns

//例化待测模块(模块例化可点击文章最后附上的网址)

led_twinkle u_led_twinkle(

.sys_clk (sys_clk), //注意语句后面为逗号

.sys_rst_n (sys_rst_n),

.led (led) //最后一步无逗号

);

endmodule

在ISE中软件操作方式会有所不同,但测试文件代码编写不变。

模块例化说明链接

最后

以上就是辛勤灰狼最近收集整理的关于Verilog测试(仿真)文件TestBench如何编写的全部内容,更多相关Verilog测试(仿真)文件TestBench如何编写内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复