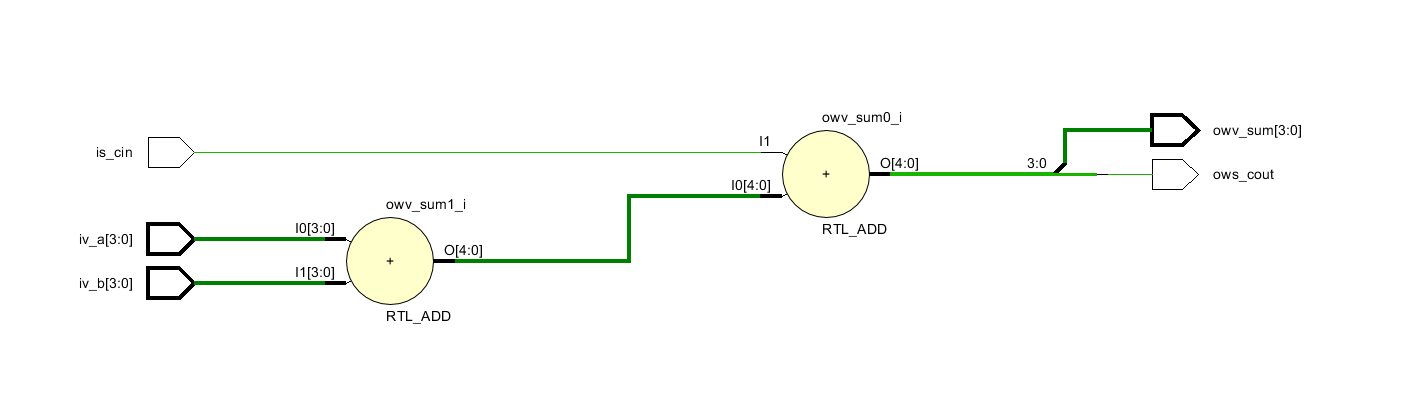

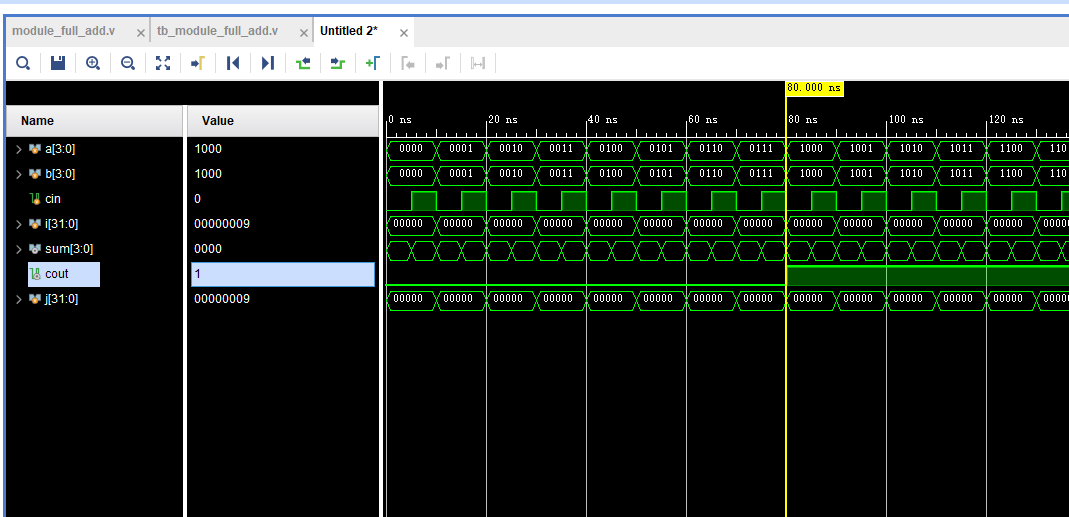

1.4位全加器

代码:

module module_full_add(

input [3:0] iv_a,iv_b,

input is_cin,

output [3:0] owv_sum,

output ows_cout

);

assign {ows_cout,owv_sum} = iv_a+iv_b+is_cin;

endmoduleRTL:

Simulation:

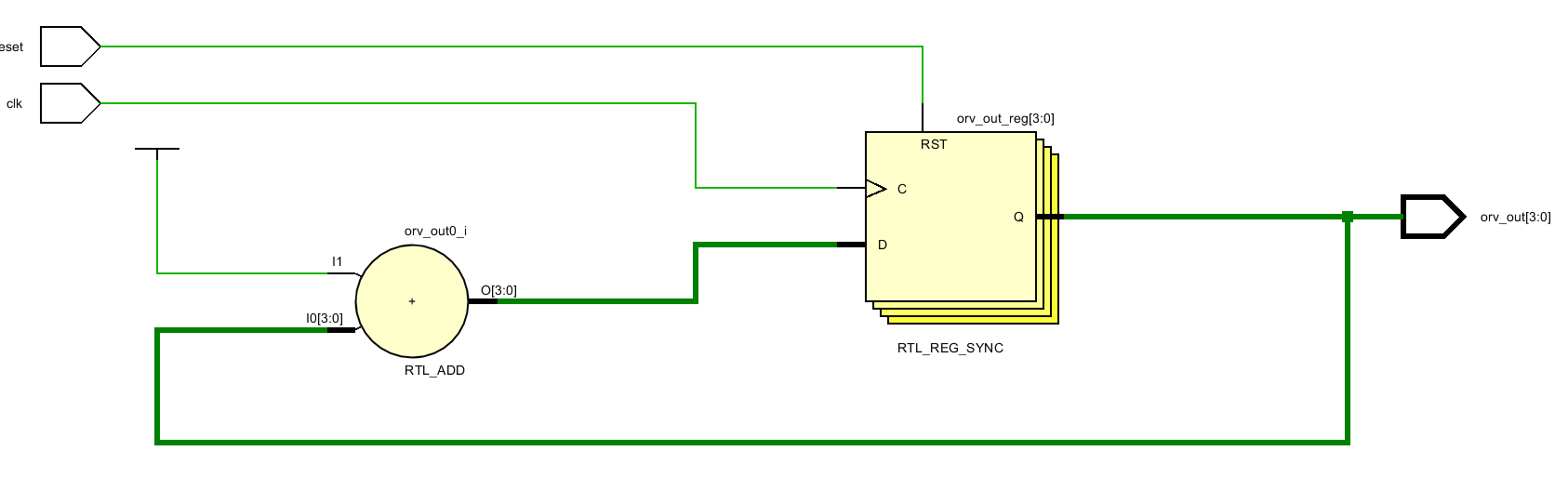

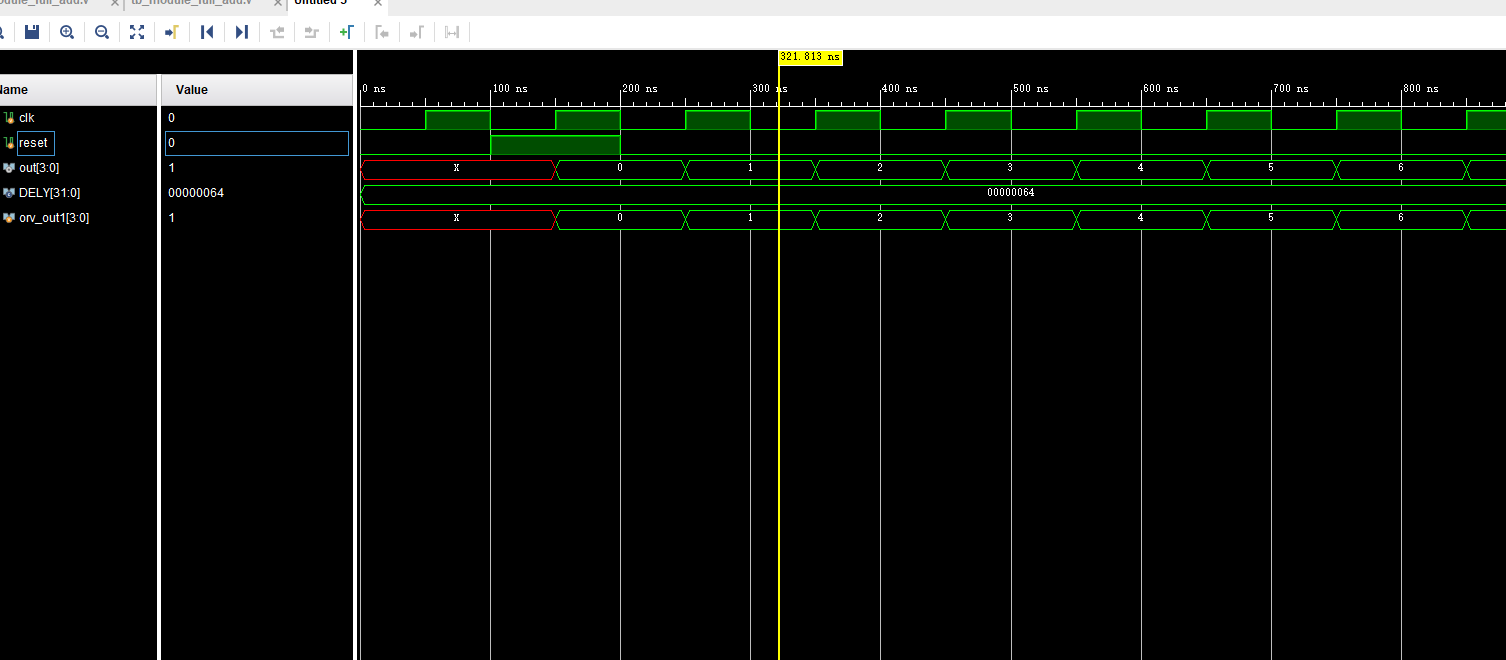

2.4位计数器

module module_full_add(

input reset,

input clk,

output [3:0] orv_out

);

reg [3:0] orv_out1;

always@(posedge clk)

begin

if(reset)

orv_out1 <= 4'b0;

else

orv_out1 <= orv_out1+1'b1;

end

assign orv_out=orv_out1;

endmoduleRTL:

仿真:

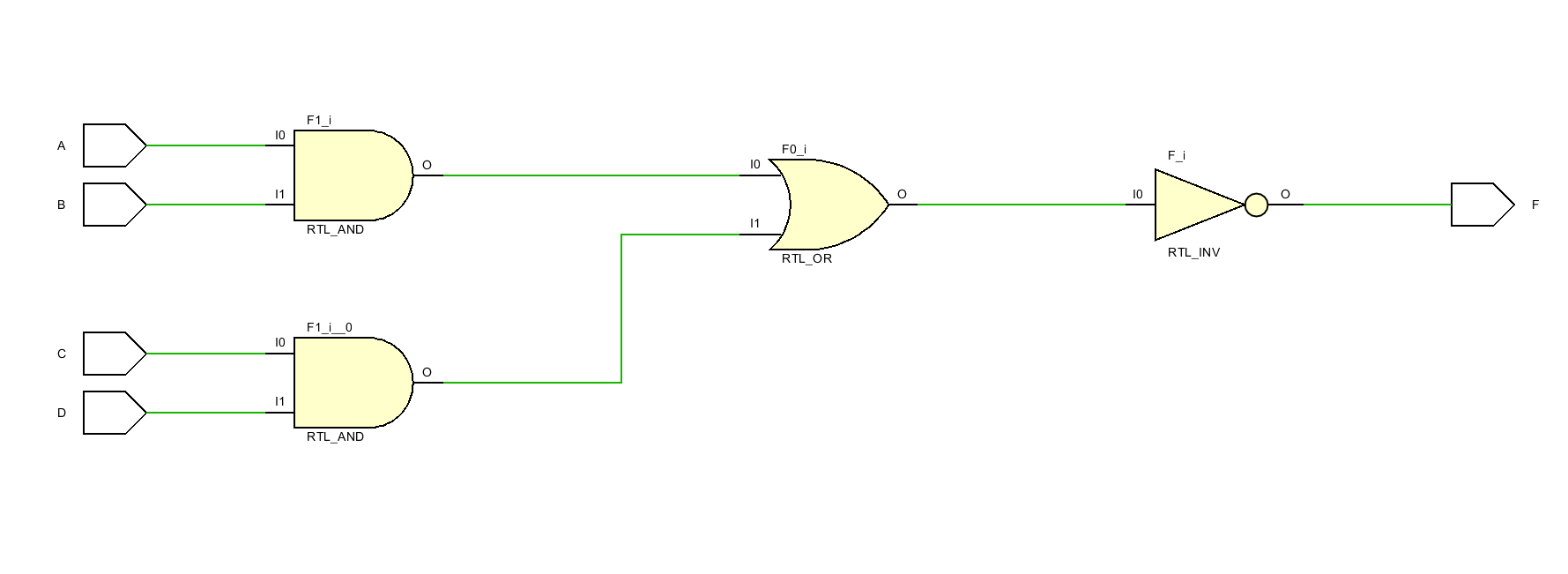

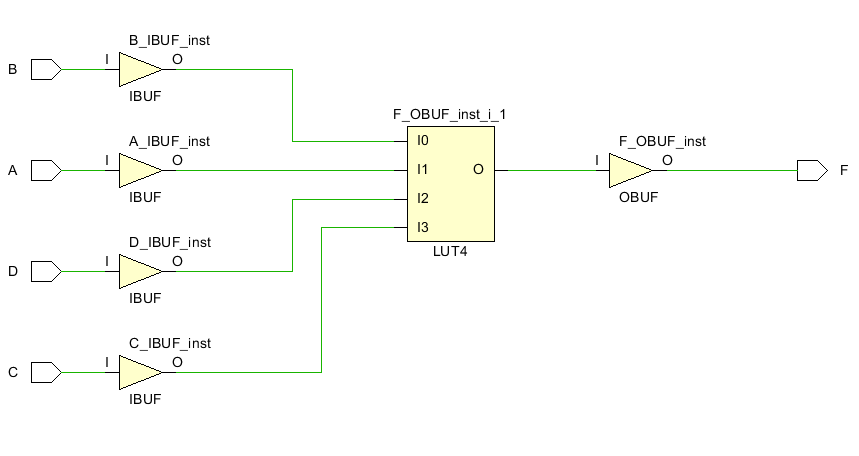

3.与或非

代码:

module module_full_add(A,B,C,D,F); //模块名为 AOI(端口列表 A,B,C,D,F)

input A,B,C,D; //模块的输入端口为 A,B,C,D

output F; //模块的输出端口为 F

wire A,B,C,D,F; //定义信号的数据类型

assign F= ~((A&B)|(C&D)); //逻辑功能描述

endmoduleRTL:

4.case四选一

代码:

module mux4_1(out,in0,in1,in2,in3,sel);

output out;

input in0,in1,in2,in3;

input[1:0] sel;

reg out;

always @(in0 or in1 or in2 or in3 or sel) //敏感信号列表

case(sel)

2'b00: out=in0;

2'b01: out=in1;

2'b10: out=in2;

2'b11: out=in3;

default: out=2'bx;

endcase

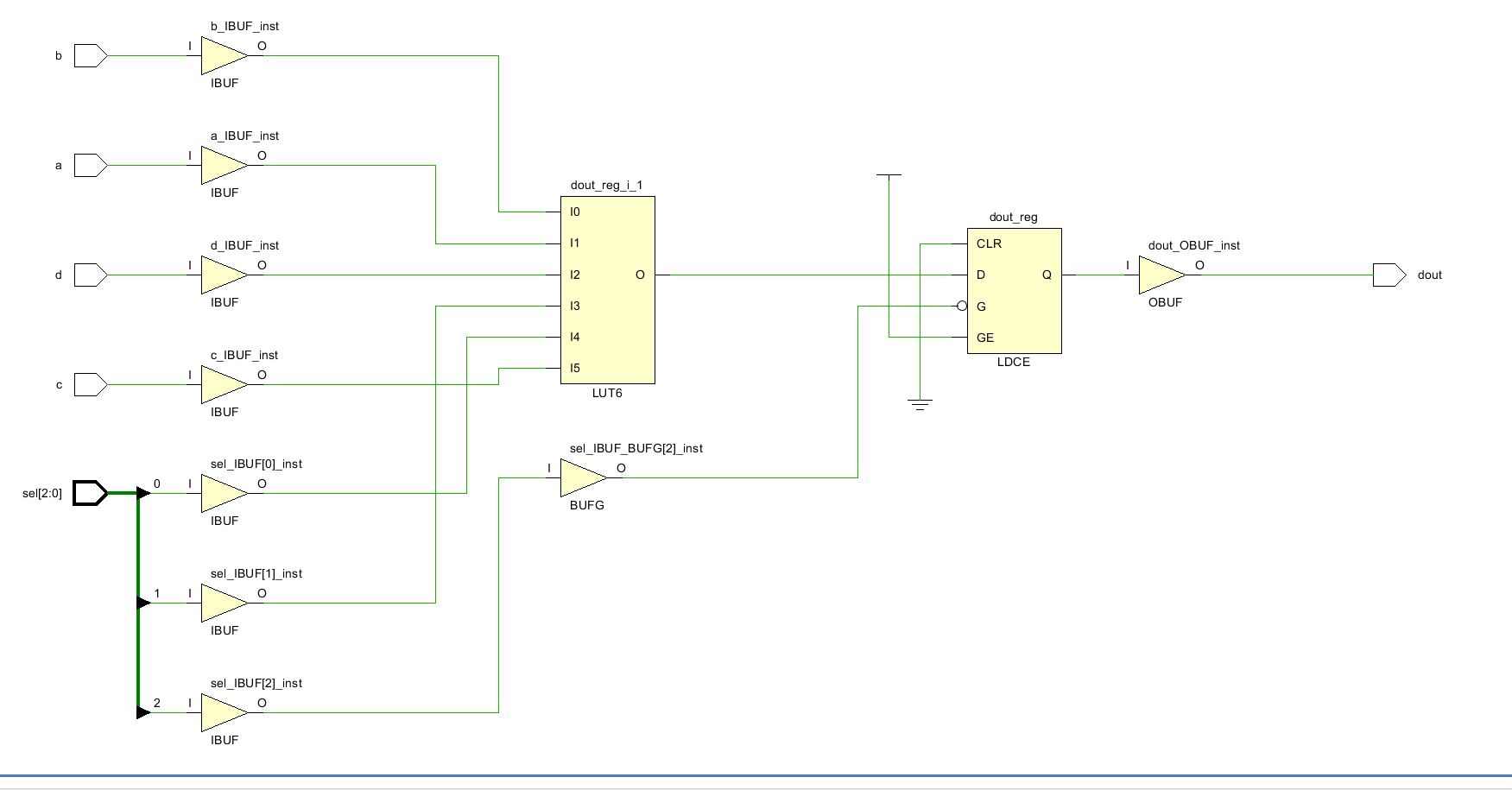

endmoduleRTL:

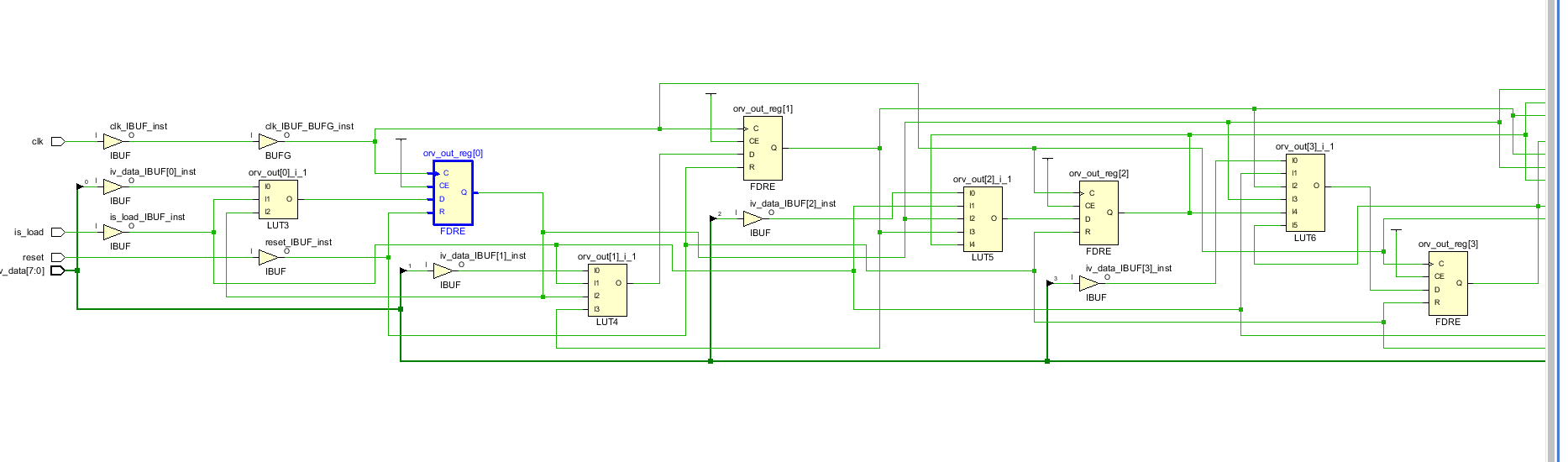

5.同步置数,同步清零。

coding:

module module_full_add(

input clk,

input reset,

input is_load,

input [7:0] iv_data,

output reg [7:0] orv_out

);

always@(posedge clk)

if(reset)

orv_out <= 8'b0;

else if(is_load)

orv_out <= iv_data;

else

orv_out <= orv_out +1'b1;

endmodule

RTL:

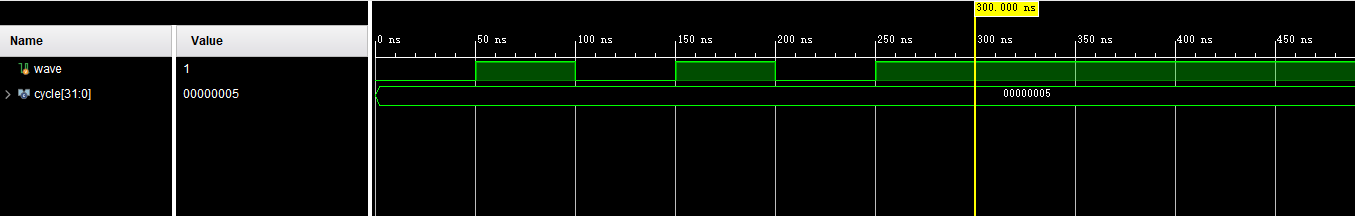

6.用fork-join并行块产生波形

coding

`timescale 10ns/1ns

module wave2;

reg wave;

parameter cycle=5;

initial

fork

wave=0;

#(cycle) wave=1;

#(2*cycle) wave=0;

#(3*cycle) wave=1;

#(4*cycle) wave=0;

#(5*cycle) wave=1;

#(6*cycle) $finish;

join

initial $monitor($time,,,"wave=%b",wave);

endmodulesimulation:

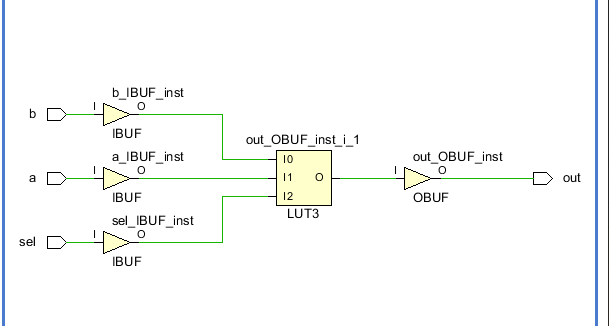

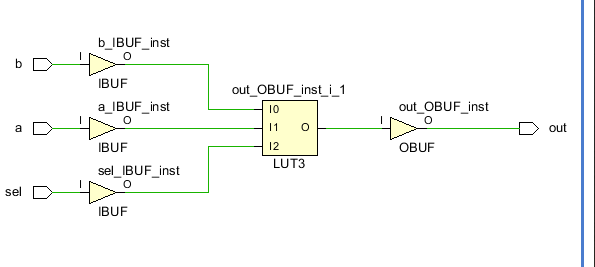

7.持续赋值方式定义的 2 选 1 多路选择器

coding:

module MUX21_1(out,a,b,sel);

input a,b,sel;

output out;

assign out=(sel==0)?a:b;

//持续赋值,如果 sel 为 0,则 out=a ;否则 out=b

endmodule

RTL:

7.阻塞赋值方式定义的 2 选 1 多路选择器

coding:

module MUX21_2(out,a,b,sel);

input a,b,sel;

output out;

reg out;

always@(a or b or sel)

begin

if(sel==0) out=a; //阻塞赋值

else out=b;

end

endmoduleRTL:

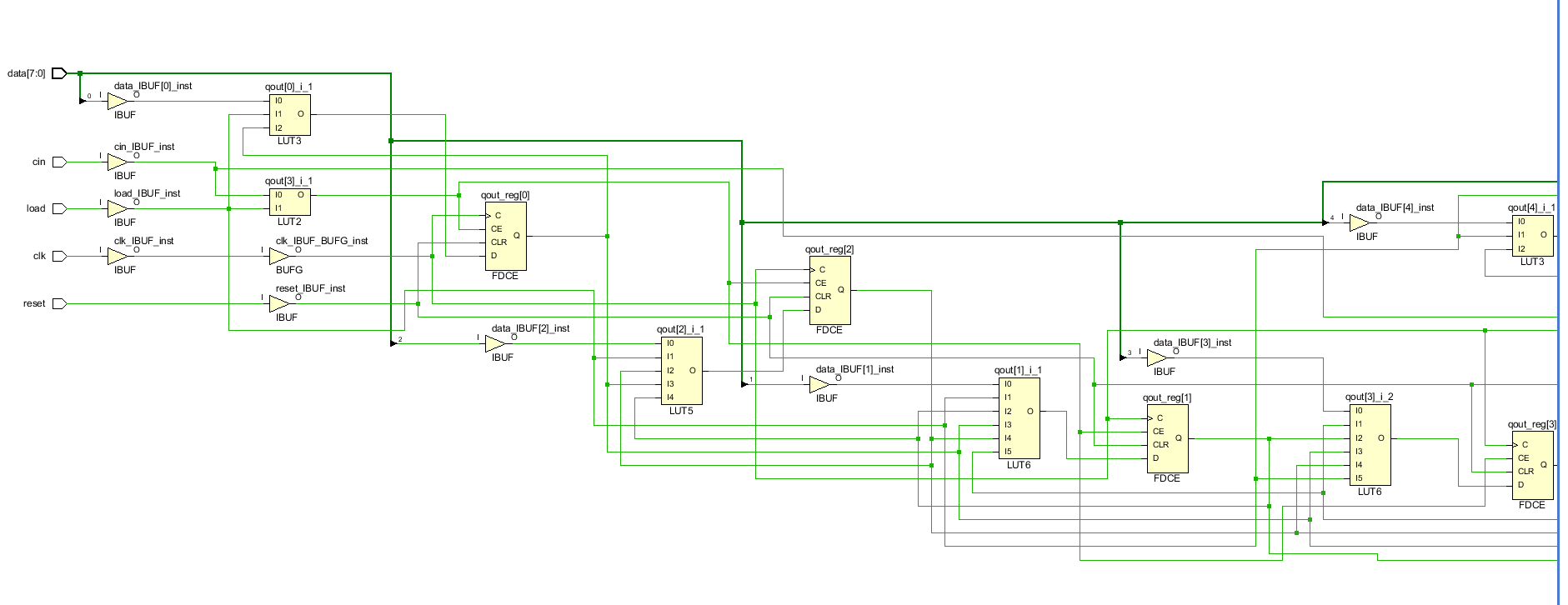

8.模为 60 的 BCD 码加法计数器

coding:

module count60(qout,cout,data,load,cin,reset,clk);

output reg[7:0] qout;

output cout;

input[7:0] data;

input load,cin,clk,reset;

always@(posedge clk or posedge reset)

if(!reset)

begin

// cout <=1'b0;

qout <= 8'b0;

end

else if(load)

qout <= data;

else if(cin)

begin

if(qout[3:0] == 9)

begin

qout[3:0] <= 0;

if(qout[7:4] == 5)

qout[7:4] <= 0;

else

qout[7:4] = qout[7:4] +1'b1;

end

else

qout[3:0] <= qout[3:0] +1'b1;

end

else

qout <=qout;

assign cout = ((qout == 8'h59)&cin) ? 1'b1: 1'b0;

endmodule

RTL:

simulation:

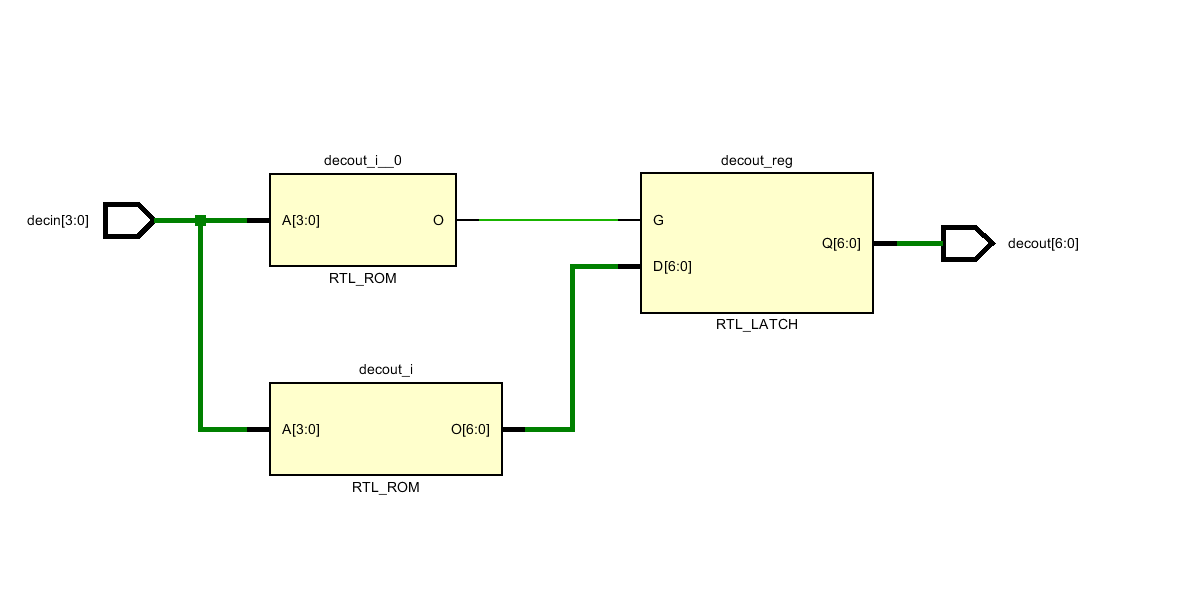

9.四输入译码器

coding:

module decode4_7(

input [3:0] decin,

output reg [6:0] decout

);

always@(decin)

begin

case(decin)

7'b0000:

decout <= 7'b111_1110;

7'b0001:

decout <= 7'b011_1110;

7'b0010:

decout <= 7'b101_1110;

7'b0011:

decout <= 7'b111_1110;

7'b0100:

decout <= 7'b111_1010;

7'b0101:

decout <= 7'b111_1100;

7'b0110:

decout <= 7'b011_1110;

7'b0011:

decout <= 7'b100_1110;

default:

decout <= decout;

endcase

end

endmoduleRTL:

10.四输入编码器

coding:

module decode4_1(

input a,b,c,d,

input [2:0] sel,

output reg dout

);

always@(sel)

begin

case(sel)

3'b000:

dout <= a;

3'b001:

dout <= b;

3'b010:

dout <= c;

3'b011:

dout <= d;

default:

dout <= dout;

endcase

end

endmoduleRTL:

11.7位表决器

coding:

module decode4_1(

input [6:0] data_in,

// input [2:0] sel,

output reg dout

);

reg [3:0] sum;

initial sum =0;

always@(data_in)

if(data_in[0] == 1)

sum = sum+1;

always@(data_in)

if(data_in[1] == 1)

sum = sum+1;

always@(data_in)

if(data_in[2] == 1)

sum = sum+1;

always@(data_in)

if(data_in[3] == 1)

sum = sum+1;

always@(data_in)

if(data_in[4] == 1)

sum = sum+1;

always@(data_in)

if(data_in[5] == 1)

sum = sum+1;

always@(data_in)

if(data_in[6] == 1)

sum = sum+1;

always@(data_in)

if(sum >3)

dout <= 1'b1;

else

dout <= 1'b0;

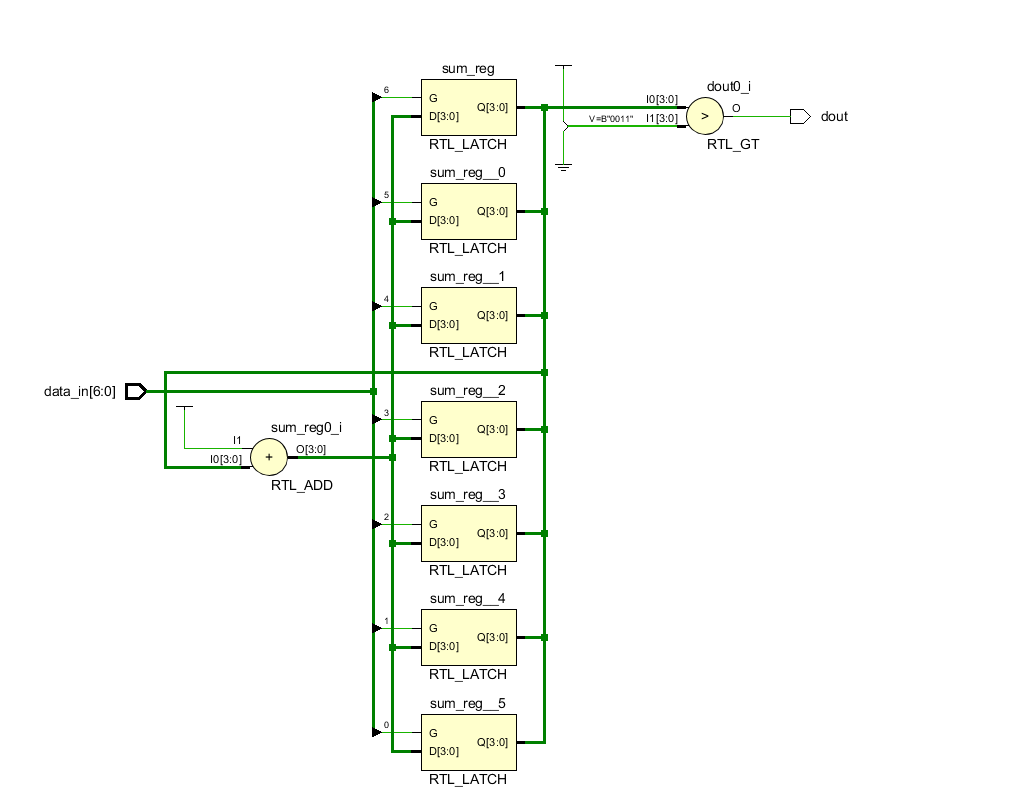

endmoduleRTL:

12.8位乘法器

13.任务举例

module alutask(code,a,b,c);

input[1:0] code;

input[3:0] a,b;

output[4:0] c;

reg[4:0] c;

task my_and; //任务定义,注意无端口列表

input[3:0] a,b; //a,b,out 名称的作用域范围为 task 任务内部

output[4:0] out;

integer i;

begin

for(i=3;i>=0;i=i-1)

out[i]=a[i]&b[i]; //按位与

end

endtask

always@(code or a or b)

begin

case(code)

2'b00: my_and(a,b,c);

/* 调用任务 my_and,需注意端口列表的顺序应与任务定义中的一致,这里的 a,b,c

分别对应任务定义中的 a,b,out */

2'b01: c=a|b; //或

2'b10: c=a-b; //相减

2'b11: c=a+b; //相加

endcase

end

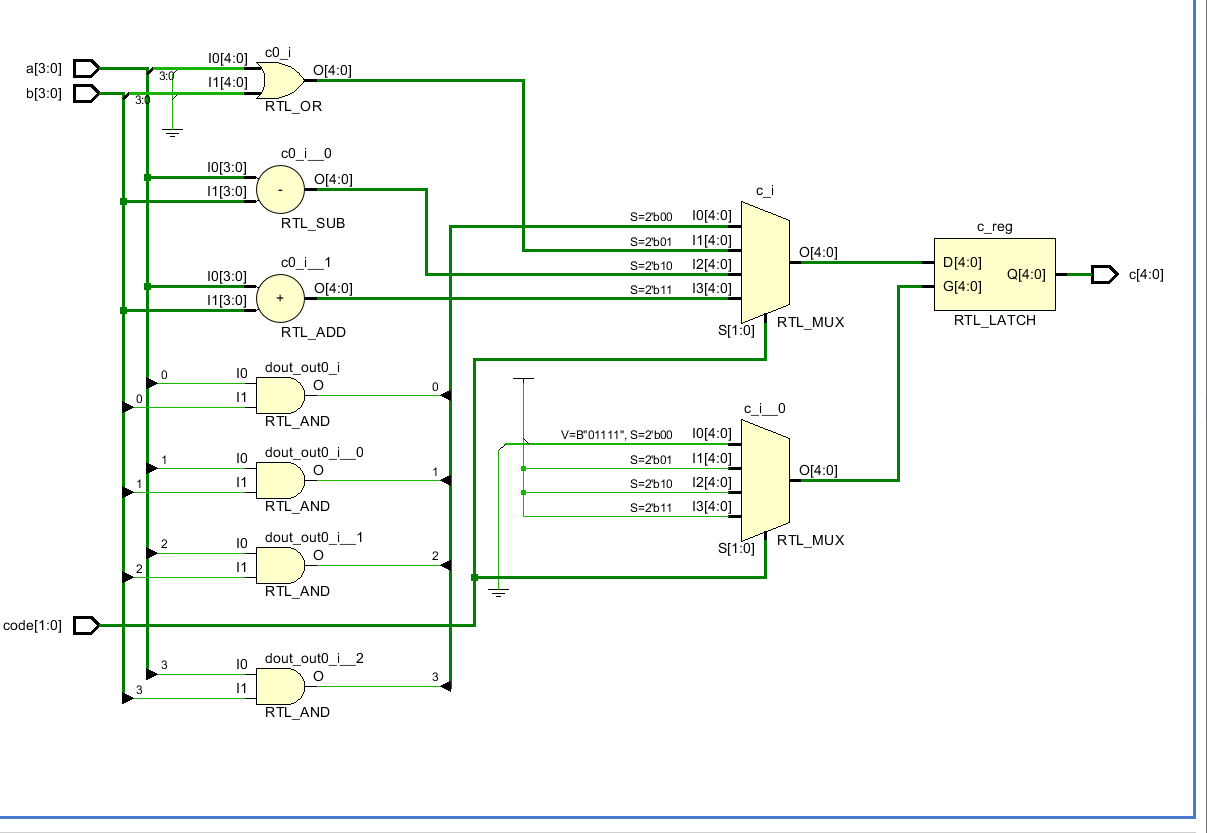

endmoduleRTL:

最后

以上就是光亮马里奥最近收集整理的关于verilog150个经典例子仿真及电路图的全部内容,更多相关verilog150个经典例子仿真及电路图内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复