目录:

一、概述

二、触发器

1、基本RS触发器

1)状态转移真值表 2)状态方程(特征方程)

2、钟控触发器

1)钟控RS触发器 2)钟控D触发器 3)钟控JK触发器 4)钟控T触发器 5)触发方式

3、集成触发器

1)触发方式 2)带有置位、复位触发器 3)边沿JK触发器

三、时序逻辑电路分析

1、概述

2、同步时序电路分析

3、异步时序电路分析

四、常用逻辑电路

1、数码寄存器

2、移位寄存器

3、计数器

1)同步二制计数器 2)同步十进制计数器 3)异步二进制计数器

4)异步十进制计数器 5)用集成计数器构成任意进制计数器 6)移位寄存器型计数器

五、时序逻辑电路的设计

----------------------------------------------------------------------------------------------------------------

一、概述

组合逻辑电路(无记忆):任意一时刻输出仅取决于该时刻输入,而与过去输入无关;

时序逻辑电路(有记忆):任意任一时刻的稳定输出不仅与当时的输入有关,而与过去输入也有关。

同步时序:各触发器有统一触发脉冲

异步时序:各触发器无统一触发脉冲

----------------------------------------------------------------------------------------------------------------

二、触发器

(1)能够存储一位二进制数字信号的基本单元叫做触发器。

(2)双稳态触发器:有两个稳定的状态0和1,当施加触发脉冲时,电路翻转,变为另一个稳态。触发脉冲撤销后,能够保持在这个稳定状态上,直到下一个触发脉冲的到来,才再次改变状态。

(3)单稳态触发器:电路只能保持在一个稳定状态上,当施加触发脉冲时,电路翻转,变为另一个状态,但这个状态无法稳定。不管触发脉冲撤销与否,电路都要自动回到原来的稳定状态。下一个触发脉冲的到来,再次重复一下这个翻转又返回的动作。

(3)单稳态触发器:电路只能保持在一个稳定状态上,当施加触发脉冲时,电路翻转,变为另一个状态,但这个状态无法稳定。不管触发脉冲撤销与否,电路都要自动回到原来的稳定状态。下一个触发脉冲的到来,再次重复一下这个翻转又返回的动作。

(5)按功能分类:RS触发器、D触发器、JK触发器、T触发器等。

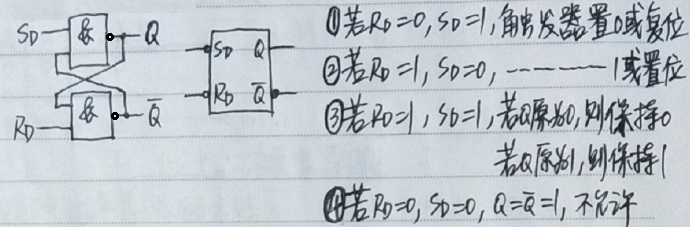

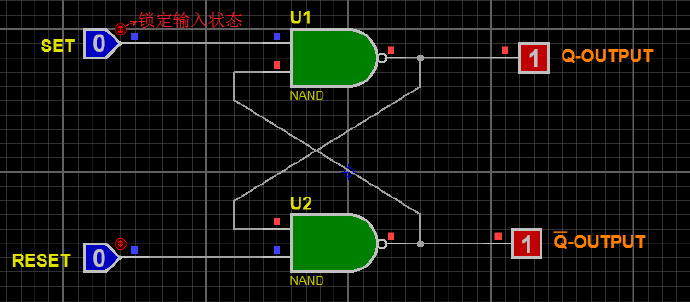

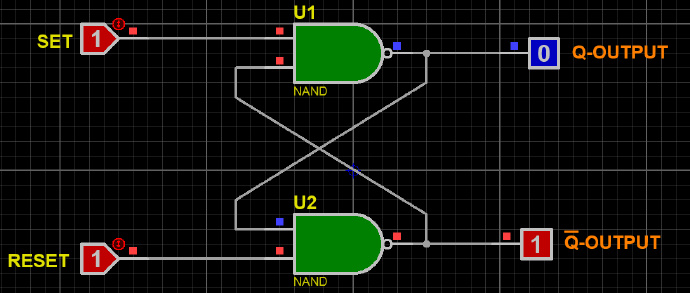

1、基本RS触发器

文件移步:https://download.csdn.net/download/liht_1634/85094870。

SET与RESET同为0,用与非门构成的 RS 触发器,约束条件:R + S = 1。其实R、S 也可以同时为零,只是此时的输出,并非互补。那么,作为两个与非门,工作正常;作为触发器,工作不正常,状态非法。

上电后二者均置为1再仿真。实际使用参见“电子元件-555时基芯片”。

------------------------------

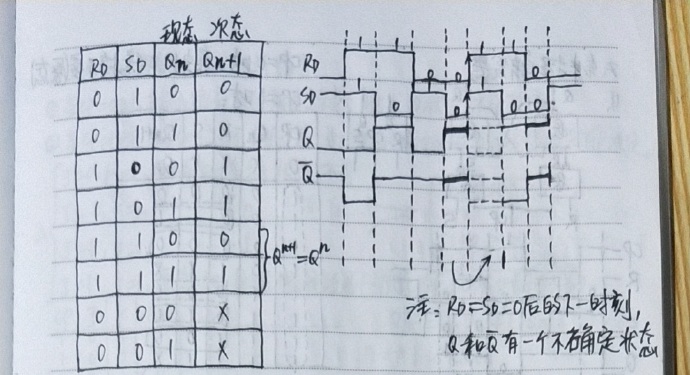

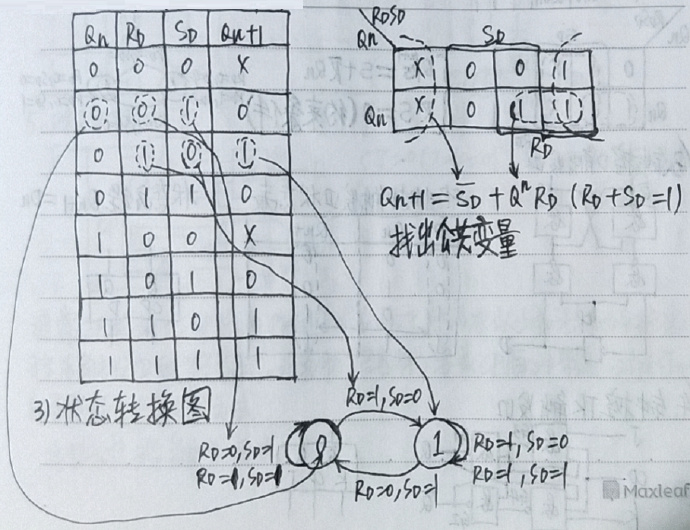

1)状态转移真值表

现态电路在某个考察瞬间t^n时的状态Q^n;

次态电路将要达到新的状态Q^(n+1)。

2)状态方程(特征方程)

---------------------------------------------------------

2、钟控触发器

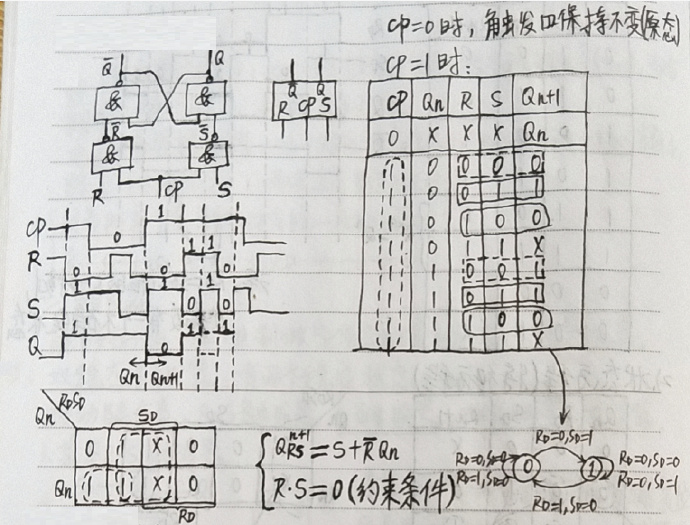

1)钟控RS触发器

------------------------------

2)钟控D触发器

------------------------------

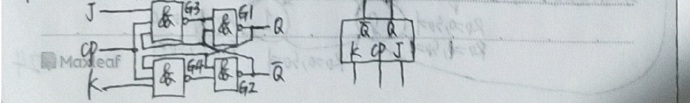

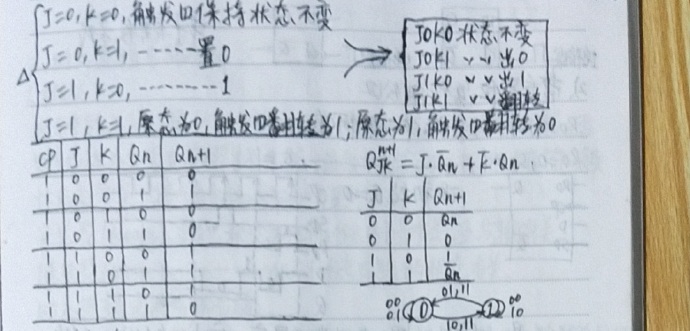

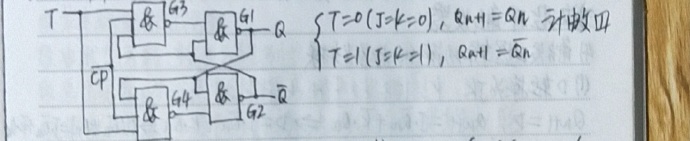

3)钟控JK触发器

JK触发器逻辑功能分析如下:

当CP=0时,输入信号J、K被封锁,触发器状态不会改变;

当CP=1时,控制门G3、G4开启,此时触发器的状态由输入信号J、K决定。

4)钟控T触发器

通常把在同一个CP脉冲作用下发生两次或两次以上翻转的现象称为触发器的“空翻”。为克服“空翻”,要求CP脉冲宽度:2Tpd

------------------------------

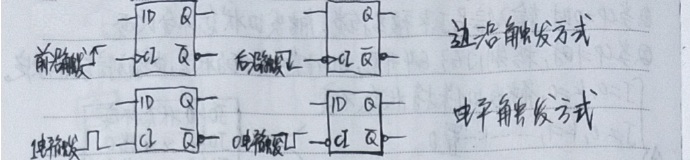

5)触发方式

电位、边沿触发方式

---------------------------------------------------------

3、集成触发器

1)触发方式

------------------------------

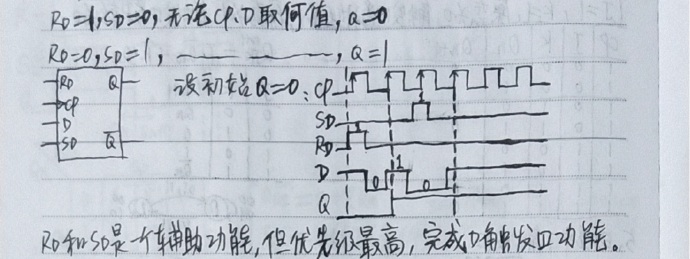

2)带有置位、复位触发器

------------------------------

3)边沿JK触发器

------------------------------

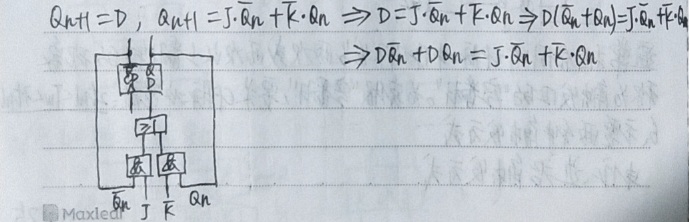

4)触发器逻辑功能 的相互转换

(1)D转换为JK

----------------------------------------------------------------------------------------------------------------

三、时序逻辑电路分析

1、概述

时钟输入端与同一个时钟源相连,称为同步时序逻辑电路,否则就称为异步时序逻辑电路。前者速度高于后者,但结构一般经后者复杂。按输出信号特点,还可分为:

米里型(Mealy):输出状态不仅与存储电路有关,还与输入有关。

摩尔型(Moore):输出状态仅与存储电路的状态有关。

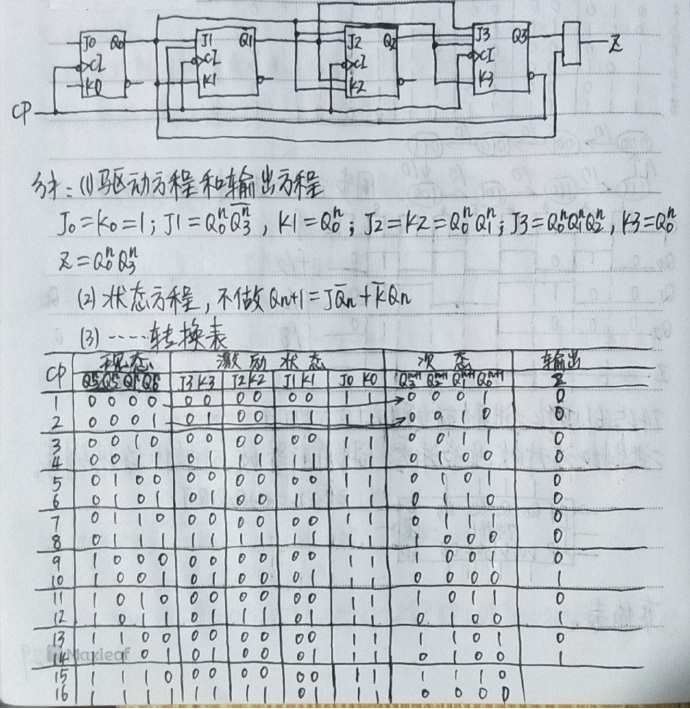

时序逻辑电路分析步骤:

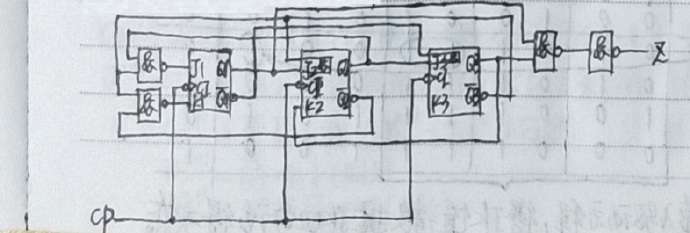

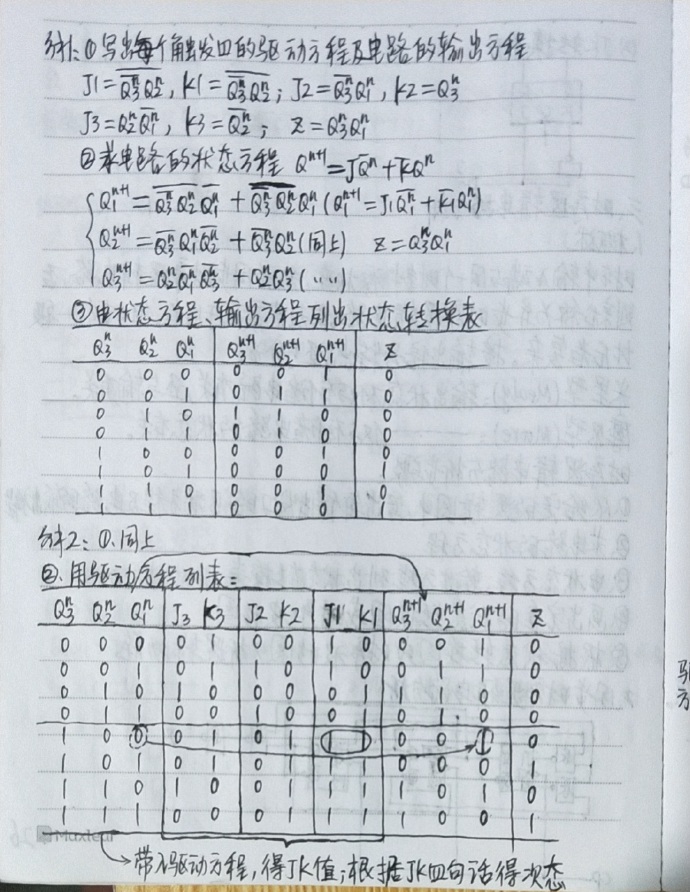

(1)从给定的逻辑图中,写出每个触发器的驱动方程及电路的输出方程

(2)求电路状态方程

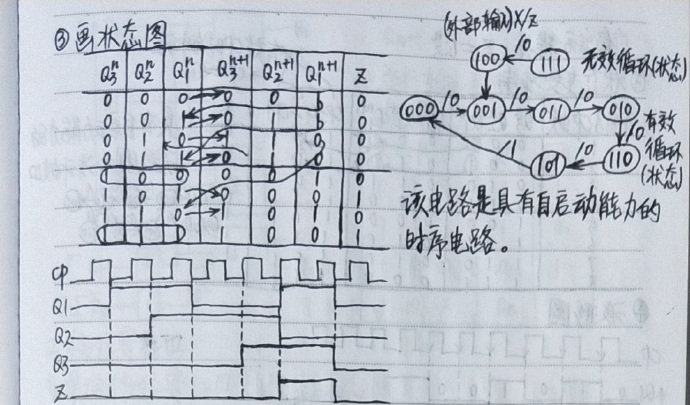

(3)由状态方程、输出方程列出状态转换表

(4)画出完整的状态转换图或时序波形图

(5)根据状态转换图或时序波形图分析逻辑功能

---------------------------------------------------------

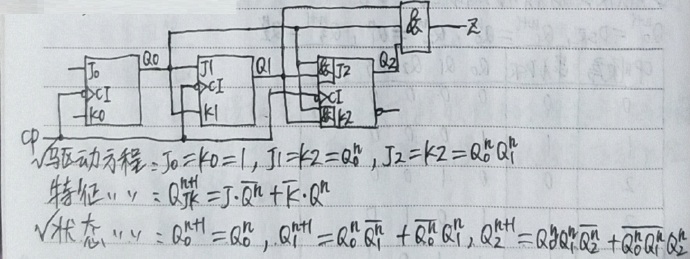

2、同步时序电路分析

---------------------------------------------------------

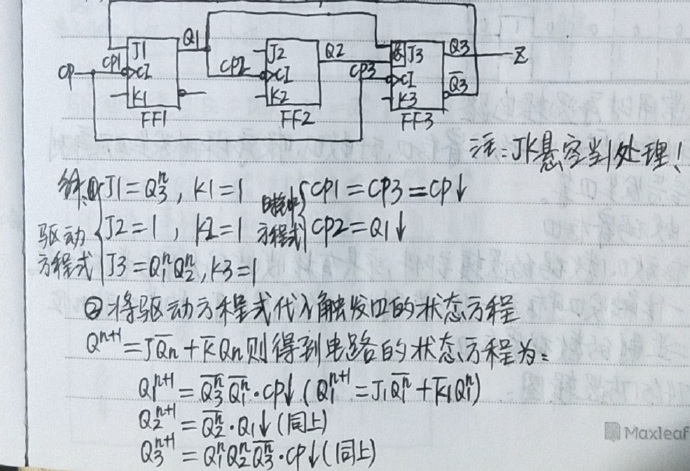

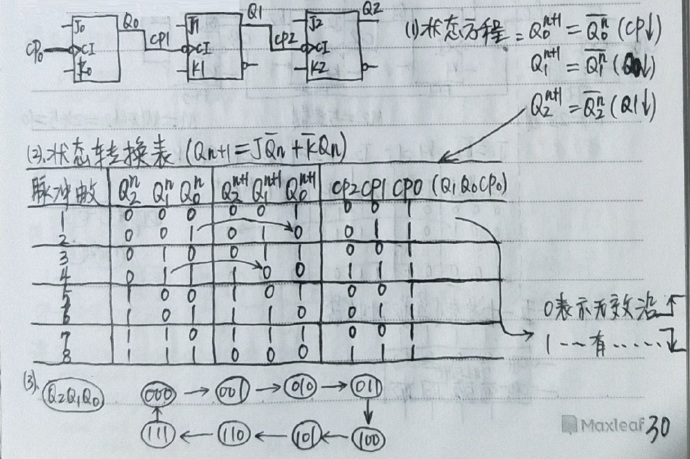

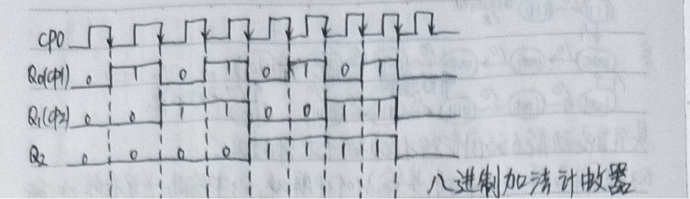

3、异步时序电路分析

----------------------------------------------------------------------------------------------------------------

四、常用逻辑电路

有数码寄存器、移位寄存器、计数器、顺序脉冲发生器及序列信号发生器等

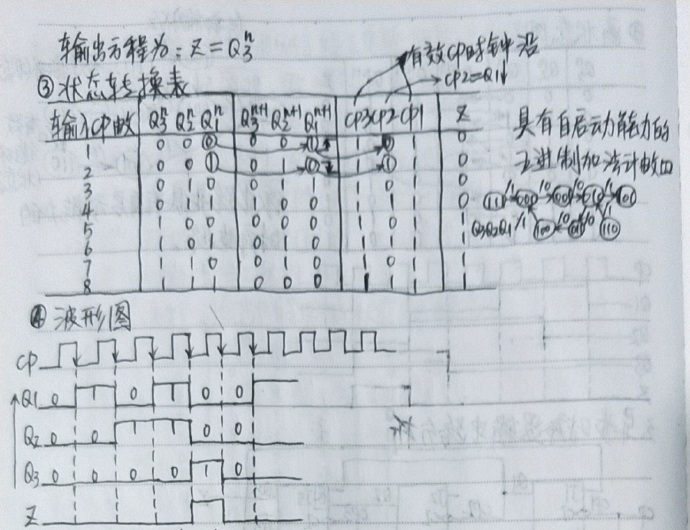

1、数码寄存器

存放0、1数码的逻辑部件,它具有接收数码和寄存数码功能。

一位触发器可存放一位二进制,n个触发器可以构成存放n位二进制的数码寄存器。

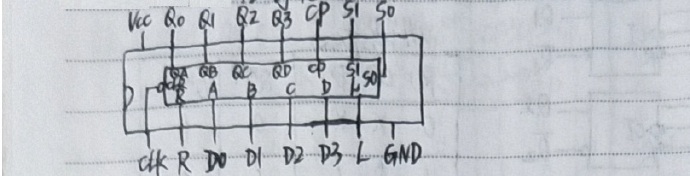

74LS175逻辑图:

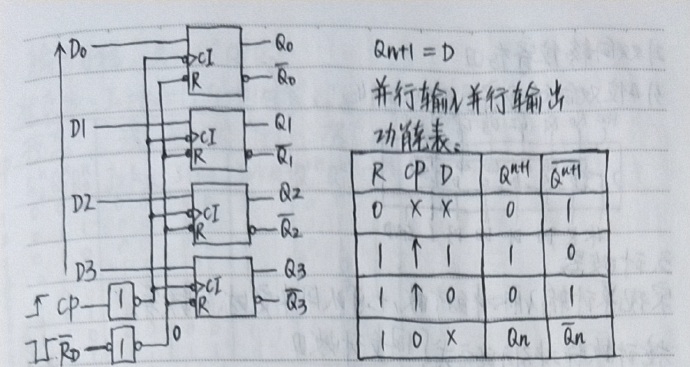

2、移位寄存器

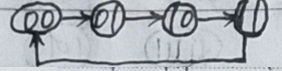

1)单向移位寄存器

------------------------------

2)双向移位寄存器

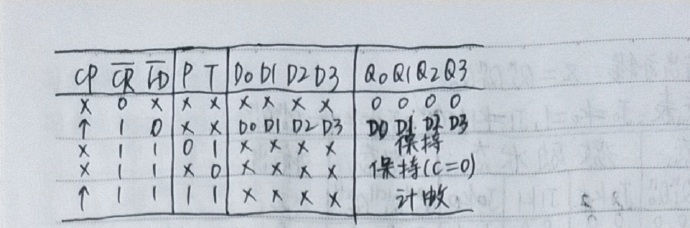

3)4位双向移位寄存器74LS194

---------------------------------------------------------

3、计数器

实现累计输入脉冲的个数,也可以用作定时、分频等。

按计数脉冲引入的方式分为同步计数器、异步计数器;

按计数进位制分类分为二进制(2^n进制)计数器;

按计数增减趋势分为加法计数器、减法计数器、可逆计数器。

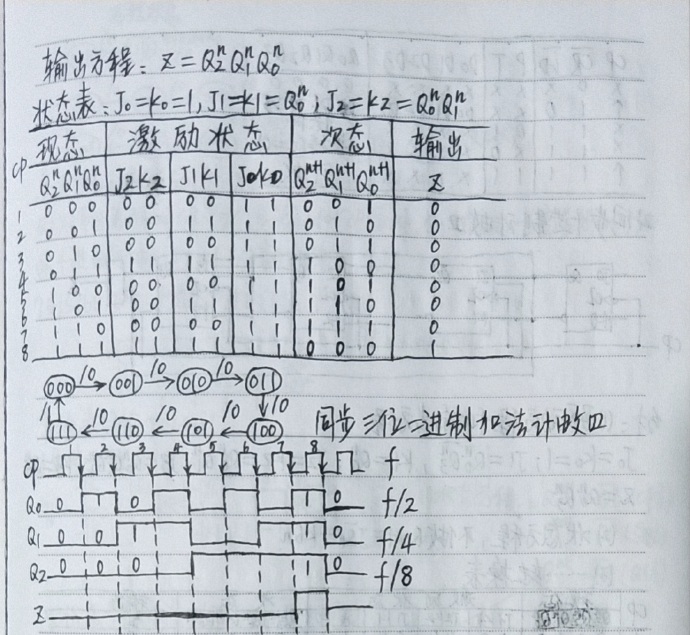

1)同步二制计数器

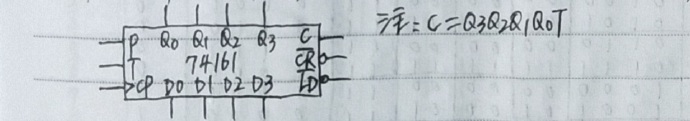

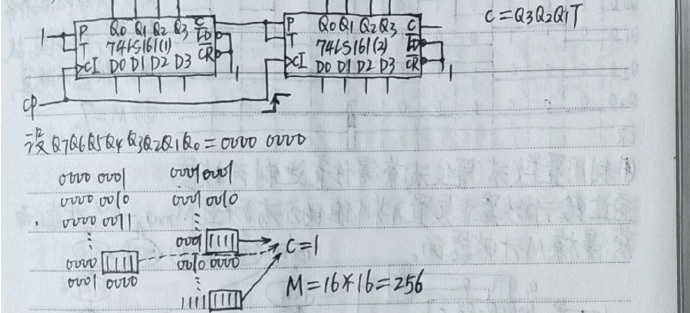

74LS161四位二进制计数器:

二进制加法计数、异步清零、同步并行置数、计数保持控制等。

真值表:

------------------------------

2)同步十进制计数器

------------------------------

3)异步二进制计数器

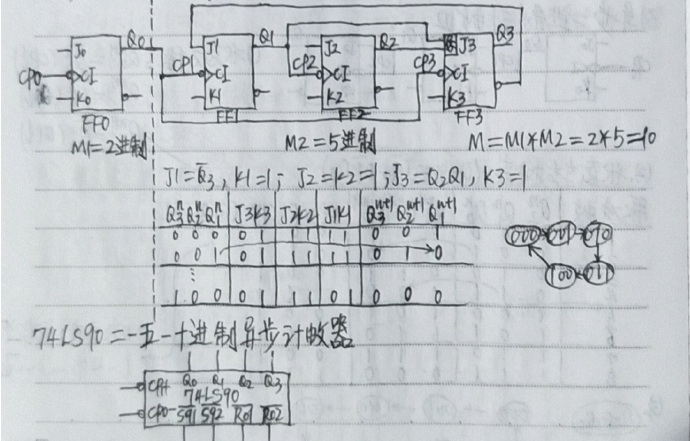

极连:用前一级计数器的输出作为后一级计数器的时钟信号,把这种连接叫计数器级连。

当把一个M1进制计数器和一个M2进制计数器级连时,可以构成M=M1*M2进制计数器。

------------------------------

4)异步十进制计数器

------------------------------

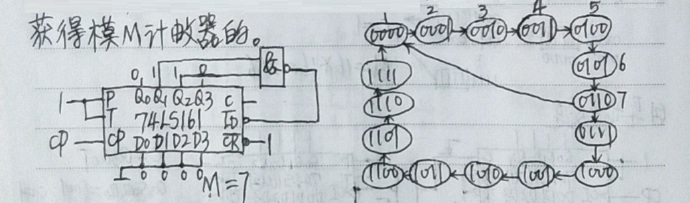

5)用集成计数器构成任意进制计数器

集成计数器一般为4位、8位二进制或十进制计数器,当超过计数范围时,可用计数器的级连来实现。

同步级连:时钟信号同时接到各片计数器的CP端,用前一级进位输出C来控制后级计数器的计数输入端。

异步级连:用前一级的进位输出C或高位输出Q作为后级的时钟信号。

(1)同步级连

(2)异步级连

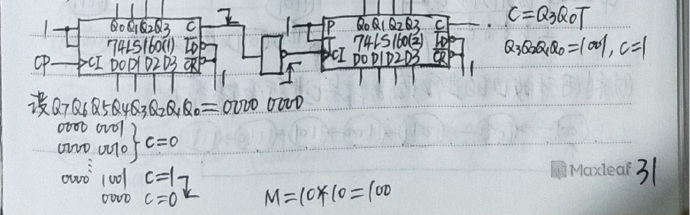

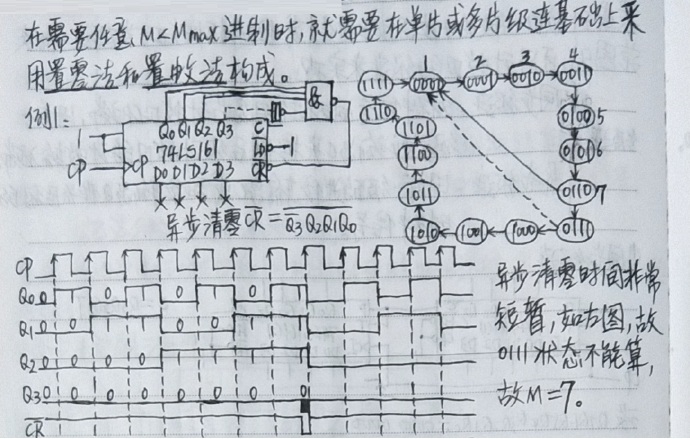

(3)用置零法接成任意进制计数器

在需要任意M

(4)利用置数法(置位法)获得任意进制计数器

通过给计数器重复置入某个值的方法跳过Mmax-M个状态,而获得模M计数器的。

(5)利用计数器的进位输出信号C进行反馈置数

------------------------------

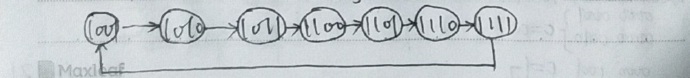

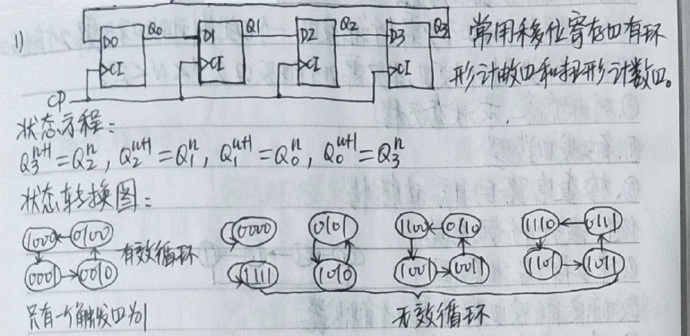

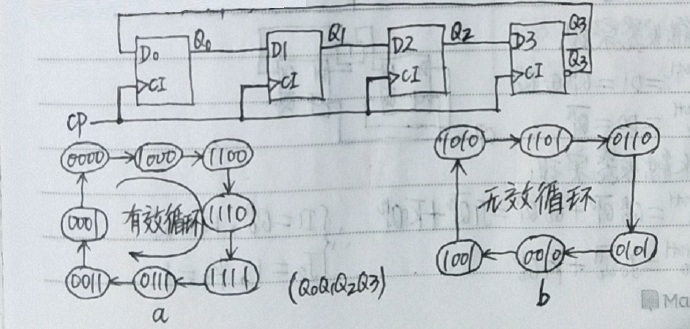

6)移位寄存器型计数器

(1)环形移位计数器

(2)扭环形计数器

----------------------------------------------------------------------------------------------------------------

五、时序逻辑电路的设计

同步时序电路的设计步骤:

(1)建立原始状态图

(2)确定触发器的数目

一个二进制计数器至少需1个触发器,一个四进制计数器至少需2个触发器。

设计一个N进制计数器至少需要n个触发器2^(n-1)

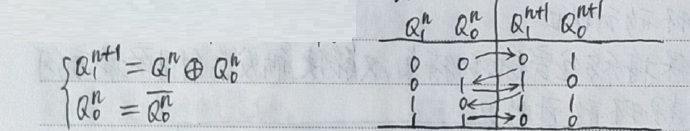

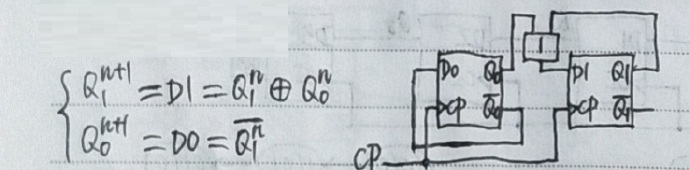

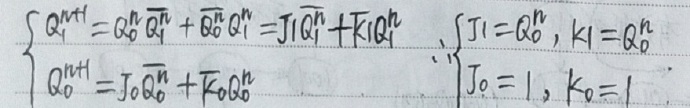

(3)列状态表、求状态方程

(4)触发器选型

(5)检查电路的自启动特性

例1:设计4分频电路

(1)建立原始状态图

(3)列状态表、求状态方程

----------------------------------------------------------------------------------------------------------------

最后

以上就是含糊发箍最近收集整理的关于时序逻辑电路笔记的全部内容,更多相关时序逻辑电路笔记内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复