我是靠谱客的博主 飞快蜗牛,这篇文章主要介绍Verilog数字系统设计——时序逻辑实验1(10进制计数器)Verilog数字系统设计五前言一、10进制计数器是什么?二、编程总结,现在分享给大家,希望可以做个参考。

Verilog数字系统设计五

时序逻辑实验1

文章目录

- Verilog数字系统设计五

- 前言

- 一、10进制计数器是什么?

- 二、编程

- 1.要求:

- 2.实现代码:

- 3.仿真测试:

- 总结

前言

随着人工智能的不断发展,机器学习这门技术也越来越重要,很多人都开启了学习机器学习,本文就介绍了机器学习的基础内容。提示:以下是本篇文章正文内容,编程实现10进制计数器,具有异步复位功能,十位和个位用8421BCD码表示

一、10进制计数器是什么?

示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。

二、编程

1.要求:

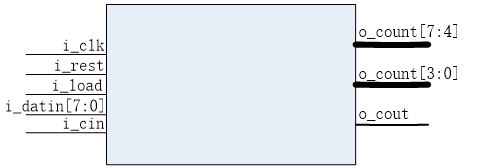

编程实现10进制计数器,具有异步复位功能,十位和个位用8421BCD码表示,各端口定义如下图所示:

2.实现代码:

always代码如下:

module decimalCounter(o_count,o_cout,i_clk,i_reset,i_load,i_datin,i_cin);

output [7:0] o_count;

output o_cout;

input [7:0] i_datin;

input i_clk,i_reset,i_load,i_cin;

reg[7:0] o_count;

always @(posedge i_clk or posedge i_reset)

begin

if (i_reset) o_count=0;

else if(i_load) o_count=i_datin;

else if(i_cin)

begin

if(o_count[3:0]==4'b1001) //ge wei is 9

begin

o_count[3:0]=0;

if(o_count[7:4]==4'b1001)

o_count[7:4]=4'b0000;

else

o_count[7:4]= o_count[7:4]+1;

end

else

o_count[3:0]=o_count[3:0]+1;

end

end

assign o_cout=((o_count==8'h99)&i_cin)?1:0;

endmodule

测试代码如下:

decimalCounter myDecimalCounter(

.o_count(o_count_t),

.o_cout(o_cout_t),

.i_clk(i_clk_t),

.i_reset(i_reset_t),

.i_load(i_load_t),

.i_datin(i_datin_t),

.i_cin(i_cin_t));

initial

begin

i_datin_t[7:0] = 0;

i_clk_t = 0;

i_reset_t = 1;

i_load_t =0;

i_cin_t = 0;

#10 i_reset_t = 0;

#20 i_datin_t=8'd7;

#80 i_load_t =1;

#40 i_load_t =0;

#360 i_datin_t=8'd99;

#5 i_load_t =1;

#40 i_load_t =0;

#20 i_datin_t=8'd5;

end

always #100 i_cin_t=~i_cin_t;

always #20 i_clk_t = ~i_clk_t;

always #820 i_reset_t=~i_reset_t;

endmodule

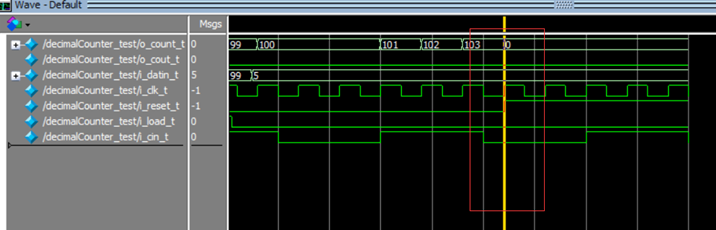

3.仿真测试:

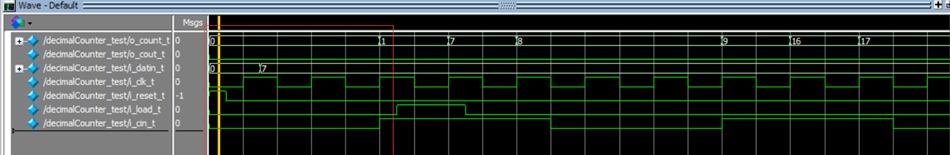

① 在初始化是先产生复位信号,使得计数初值位0 ,进位信号在置位信号前到来,在时钟上升沿到来时计数值加1;:

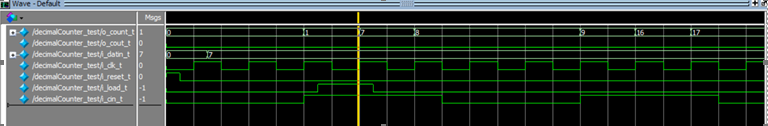

②datin值为7时,置位信号到来,在下一个时钟上升沿将,datin的值赋给计数值,进位信号有效,下一个时钟上升沿时,计数值加一为8;

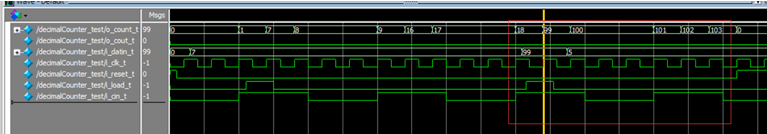

③datin值为99时,置位信号到来,在下一个时钟上升沿将,datin的值赋给计数值,进位信号有效,下一个时钟上升沿时,计数值加一为100,等待进位信号有效继续在每个时钟上升沿到来时加一;

④,在复位信号到来时,将计数值清零。

总结

提示:

以上就是今天要分享的内容,本文仅仅简单介绍了Verilog实现10进制计数器,具有异步复位功能,十位和个位用8421BCD码表示功能。

最后

以上就是飞快蜗牛最近收集整理的关于Verilog数字系统设计——时序逻辑实验1(10进制计数器)Verilog数字系统设计五前言一、10进制计数器是什么?二、编程总结的全部内容,更多相关Verilog数字系统设计——时序逻辑实验1(10进制计数器)Verilog数字系统设计五前言一、10进制计数器是什么内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复