数字电路-时序逻辑电路

- Mealy machine and Moore machine

- Latches and Filp-Flops(锁存器与触发器)

- S-R Latch

- D Latch

- D Flip-Flop

- Edge-Triggered J-K Flip-Flop (边沿J-K触发器)

- T Flip-Flop

- Analysis and Design(时钟同步状态机分析和设计)

- Analysis

- Design

- State Minimization(状态化简)

Mealy machine and Moore machine

- Mealy (米里机):A sequential circuit whose outputs depends on both states and inputs.(输出取决于输入和当前状态)

- Moore (摩尔机): A sequential circuit whose outputs depends on the states alone.(输出只取决于当前状态)

Latches and Filp-Flops(锁存器与触发器)

- Latch(锁存器) can change its outputs at any time when its enable is asserted.

- Flip-Flop(触发器) samples its inputs and changes its outputs at each tick of the clock.

S-R Latch

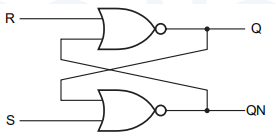

由或非门构成的S-R latch

-

结构

-

Function table (功能表)

当S=0,R=0 ,如果Q=QN’,则保持不变。

当S=0,R=0, 如果Q=QN,则振荡。 -

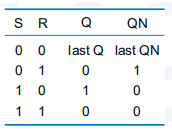

Logic symbol(逻辑符号)

-

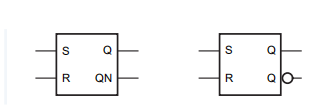

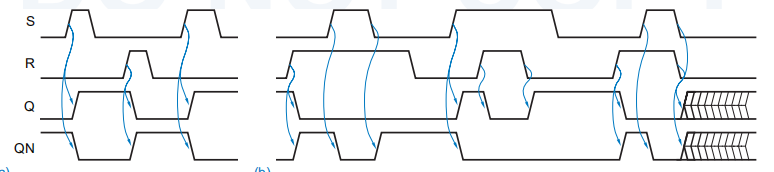

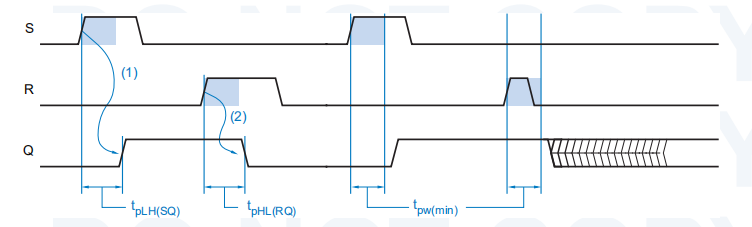

Timing Diagram

-

逻辑功能表

| S | R | Q | Q* | 功能 |

|---|---|---|---|---|

| 0 | 0 | 0 1 | 0 1 | 保持 |

| 0 | 1 | 0 1 | 0 0 | 置0 |

| 1 | 0 | 0 1 | 1 1 | 置1 |

| 1 | 1 | 0 1 | d d | 不定 |

S:使Q输出为1

R:使Q输出为0

特征方程:Q*=S+R’·Q

- Timing parameters(时间参数)/ minimun-pulse-width(最小脉冲宽度)

如果加在输入端S和R上的信号脉宽小于最小脉宽tpw(min),那么锁存器就可能进入亚稳态,并且停留在这一状态上的时间将是随机的。要确保锁存器脱离亚稳态,只有在S和R端上加一个满足或超过最小脉宽要求的脉冲才行。

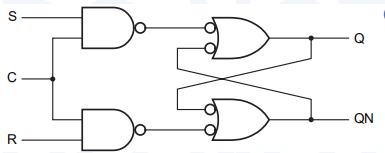

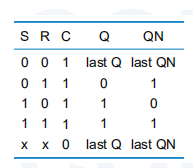

- 具有使能端的S-R Latch

- 结构

- Function table

- logic symbol

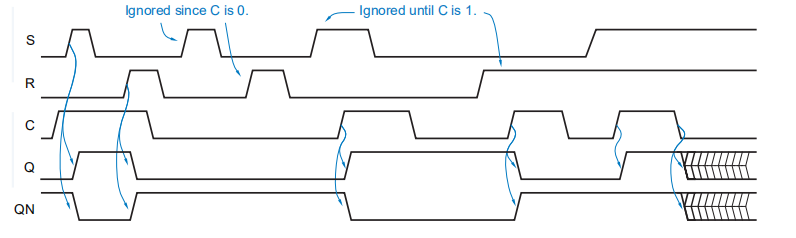

- Timing Diagram

当C=1时的行为特性与S-R锁存器相同;而当C=0时电路处于保持状态。

当S和R都为1时,如果C从1变到0,则电路的下一个状态是不可预测的,并且输出可能进入亚稳态。

- 结构

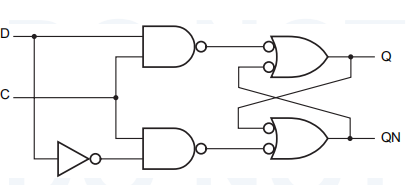

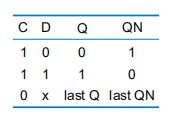

D Latch

- 结构

- Function table

特征方程:Q*= D - logic symbol

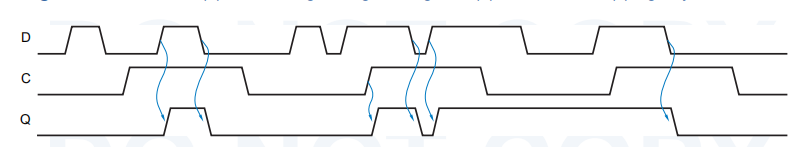

- Timing Diagram

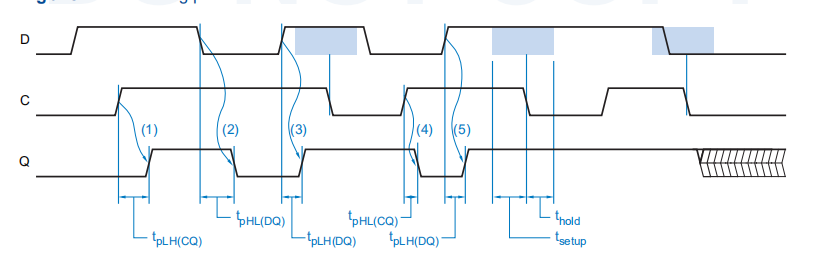

- Timing parameters

如果D输入信号在建立时间tsetup和保持时间thold窗内的任何时刻发生变化的话,锁存器的输出就是不可预测的,并且可能进入亚稳态。

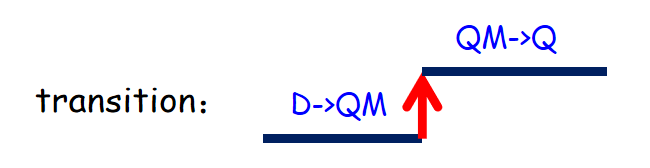

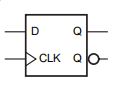

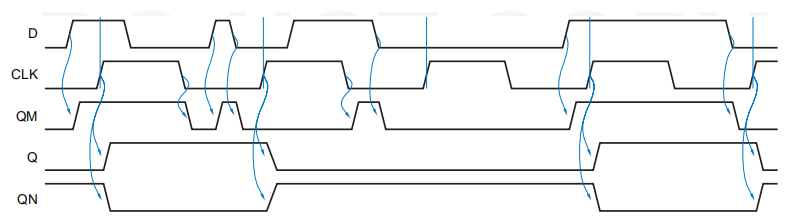

D Flip-Flop

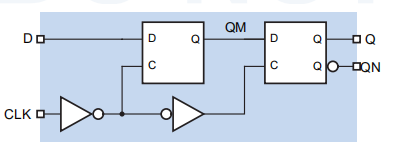

一对D锁存器可以构成一个正边沿触发式D触发器(上升沿触发式D触发器)

-

电路

-

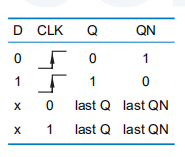

Function table

CLK:Dynamic-input indicator(动态输入指示符)CLK is low ,QM = D ,output Q remains.

CLK is high , QM remains ,output Q = QMThe input can not change the output directly.

特征方程:Q* = D

-

logic symbol

-

正边沿触发式D触发器功能特性

-

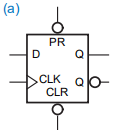

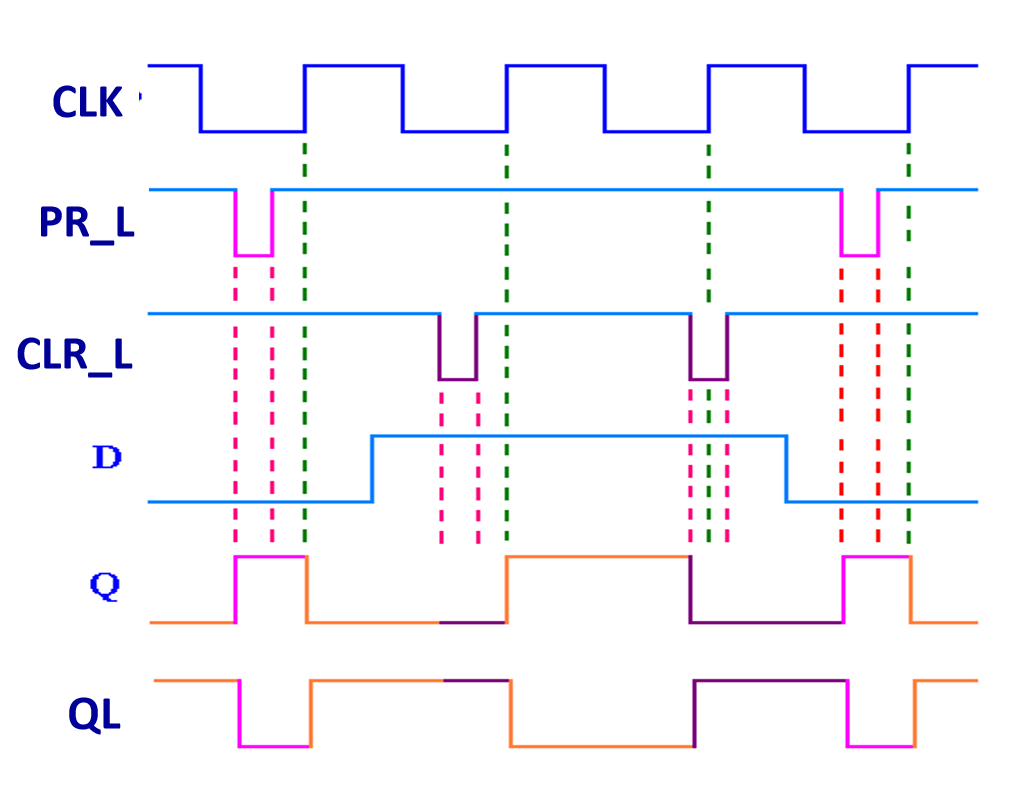

D FF with PR and CLR

asynchronous inputs (异步输入端)

PR(预置(preset))

CLR(清零(clear))- logic symbol

- logic symbol

-

Timing diagram

-

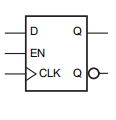

Edge-Triggered D FF with Enable

特征方程:Q* = EN·D+EN’·Q

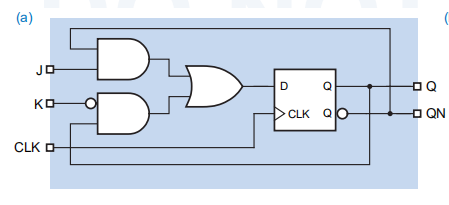

Edge-Triggered J-K Flip-Flop (边沿J-K触发器)

- 电路

- logic symbol

- State transition truth table

| J | K | Q | Q* | 状态 |

|---|---|---|---|---|

| 0 | 0 | 0 1 | 0 1 | keep |

| 0 | 1 | 0 1 | 0 0 | reset |

| 1 | 0 | 0 1 | 1 1 | set |

| 1 | 1 | 0 1 | 1 0 | jump |

Characteristic equation (特征方程):Q* = J·Q’ + K’·Q

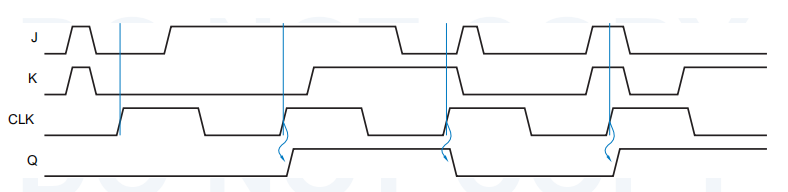

- Timing Diagram

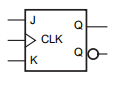

T Flip-Flop

在每一个时钟脉冲的有效边沿都会改变状态。

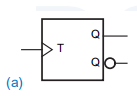

- logic symbol

- Timing diagram

特征方程:Q * = T Q ’ +T ’ Q - T FF with EN

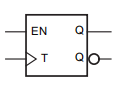

- logic symbol

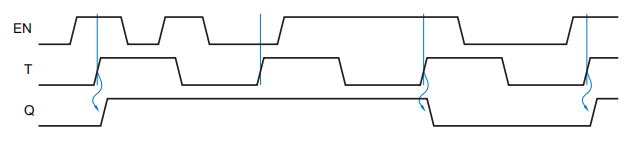

- Timing diagram

特征方程:Q* = EN·Q’+EN’·Q

- logic symbol

Analysis and Design(时钟同步状态机分析和设计)

Analysis

3-2-1 method

- (1)write the excitation equation from the logic diagram;

(2)write the transition equation;

(3) write the output equation. - (1)create transition/output table;

(2)create state/output table. - Draw state diagram/Timing diagram.

详细步骤:

- 确定触发器控制输入的激励方程。

- 将激励方程带入触发器的特征方程得到转移方程。

- 用转移方程构造转移表。

- 确定输出方程。

- 在转移表中对每一种状态组合(对于Moore型机)或者状态/输入组合(对于Mealy型机)添加输出值,就构造成了转移/输出表。

- 对状态命名并用状态名代替转移/输出表中的状态变量取值组合,就得到了状态/输出表。

在使用321方法之前,判断该电路是米里机还是摩尔机。

具体问题具体分析。

Design

这是对于Analysis的逆过程,进行123method即可。

State Minimization(状态化简)

- 如果S1和S2是等价或是等价对 用(S1,S2)表示

- 输入序列可以是任意长度和组合。

- Transferability: (S1, S2) ∧ (S2, S3) → (S1, S2, S3)

- 如果(S1,S2) 和 (S2,S3) 那么{ S1,S2,S3} 是一个等价类。

- 找到最大等价类ECS

Minimization Steps

- Draw the State Implication Table (状态隐含表) 画行列都比状态数少1的三角形网.

- Compare sequentially to find equivalent state pairs, and thus find the maximum ECs using the transferability.

- Determine the final states.

内容参考:《数字设计原理与实践》第四版

最后

以上就是火星上小猫咪最近收集整理的关于数字电路-时序逻辑电路(笔记(二))的全部内容,更多相关数字电路-时序逻辑电路(笔记(二))内容请搜索靠谱客的其他文章。

发表评论 取消回复