山东大学计算机组成与设计实验七 节拍脉冲发生器时序电路实验,

山东大学计算机组成与设计实验,

山东大学计算机组成与设计实验报告,

计算机组成原理实验报告,

山东大学计算机组成原理实验报告

文章目录

- 实验7 节拍脉冲发生器时序电路实验

- 1、实验目的:

- 2、实验原理:

- (1)原理图1:

- 实验结果:

- 结果分析:

- (2)原理图2:

- 实验结果:

- 结果分析:

实验7 节拍脉冲发生器时序电路实验

1、实验目的:

掌握节拍脉冲发生器的设计方法,理解节拍脉冲发生器的工作原理。

2、实验原理:

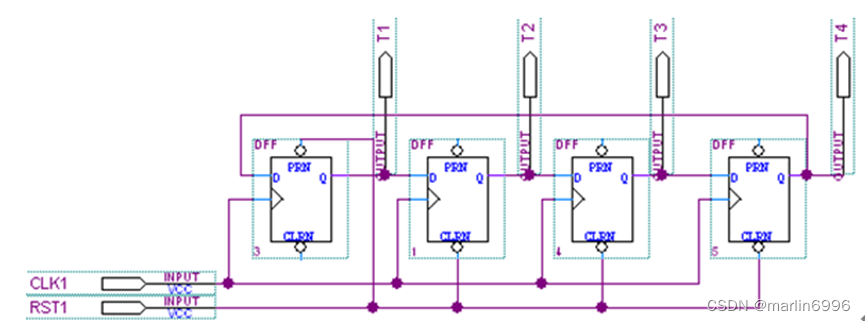

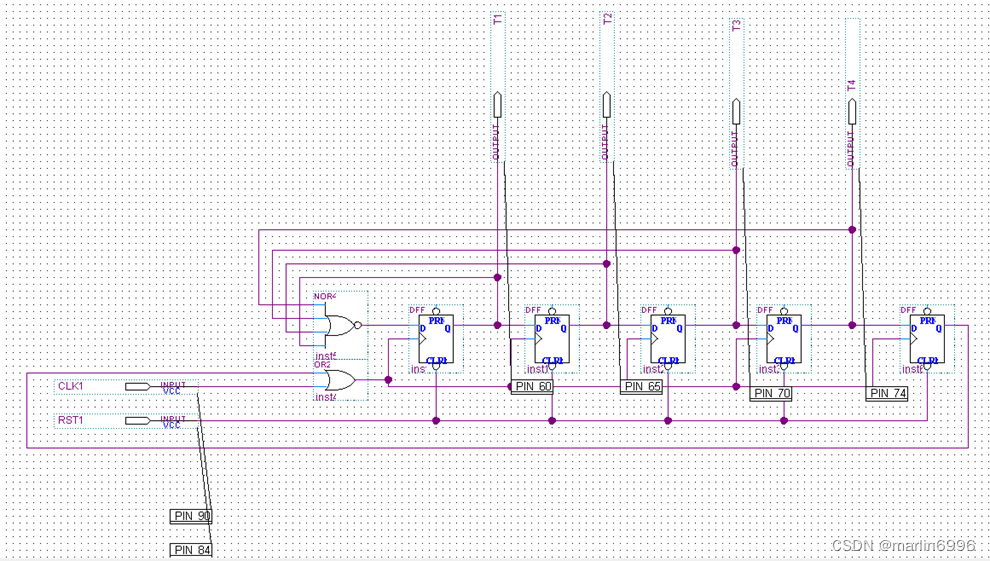

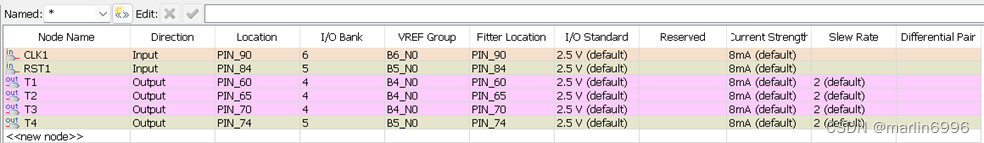

连续节拍发生电路可由4个D触发器组成(见图11-1),可产生4个等间隔的时序信号T1T4,其中CLK1为时钟信号,由实验台右边的方波信号源clock0提供,clock0具有1Hz50MHz的多种方波信号频率。实验者可根据实验自行选择信号频率。当RST1为低电平时,T1输出为“1”,而T2、T3、T4输出为“0”;当RST1由低电平变为高电平后,T1~T4将在CLK1的输入脉冲作用下,周期性地轮流输出正脉冲,机器进入连续运行状态(EXEC)。

图11-1 节拍脉冲发生器的工作原理

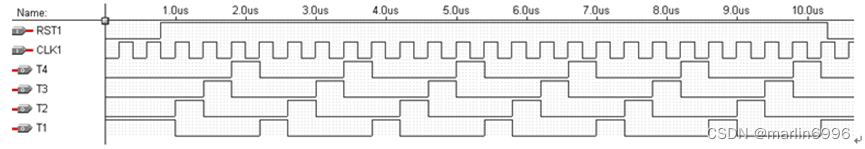

T1~T4以及CLK1、RST1的工作波形如图11-2所示。

图11-2 节拍脉冲发生器工作波形

3、实验任务:

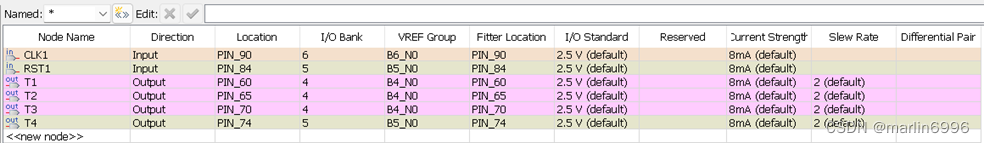

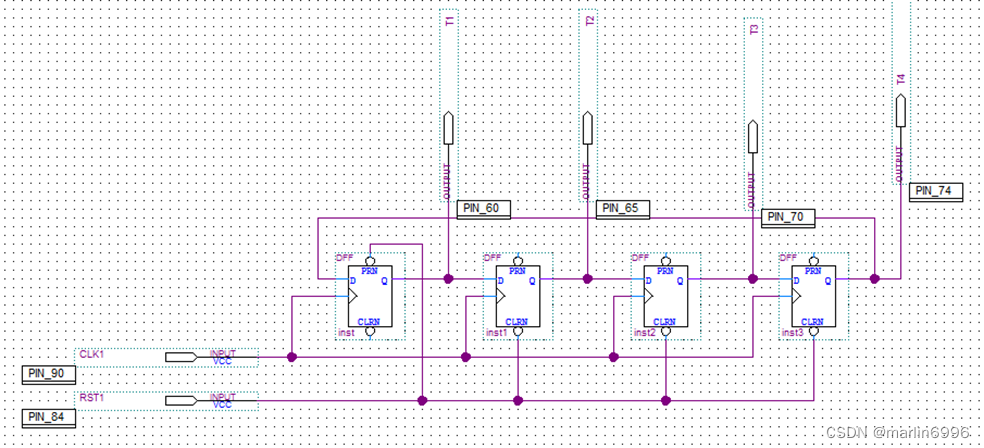

(1)连续节拍发生电路设计

设计工程文件,硬件电路如图11-1所示。使实验平台工作于模式5,主系统时钟源接4Hz,键8控制RST1,高电平时可以看到,发光管D1、D2、D3、D4分别显示T1、T2、T3、T4的输出电平,锁定引脚并硬件下载测试。引脚锁定后进行编译、下载和硬件测试实验。将实验过程和实验结果写进实验报告。

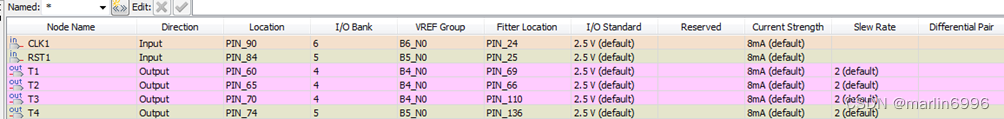

(2)单步节拍发生电路设计

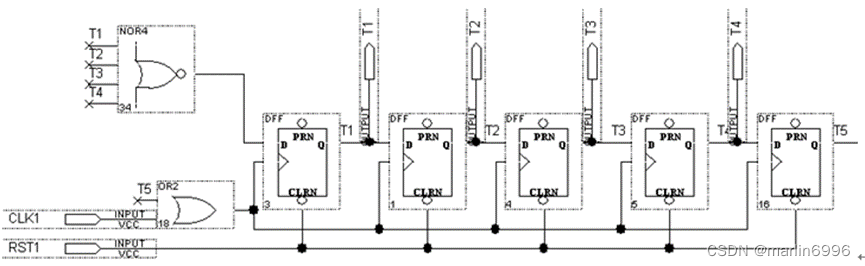

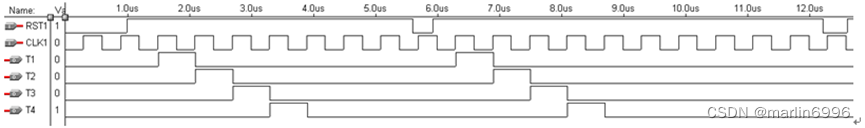

用单步节拍发生电路可以对微程序进行单步运行调试,电路如图11-3所示。该电路每当RST1出现一个负脉冲后,仅输出一组T1、T2、T3、T4节拍信号,直到RST1出现下一个负脉冲,波形如图11-4所示。

图11-3 单步运行电路工作原理

图11-4 单步运行电路工作波形

设计工程文件,硬件电路如图11-3所示。使实验平台工作于模式5,主系统时钟源接4Hz,键8控制RST1,高电平时可以看到,发光管D1、D2、D3、D4分别显示T1、T2、T3、T4的输出电平,锁定引脚并硬件下载测试。引脚锁定后进行编译、下载和硬件测试实验。将实验过程和实验结果写进实验报告。

(1)原理图1:

实验结果:

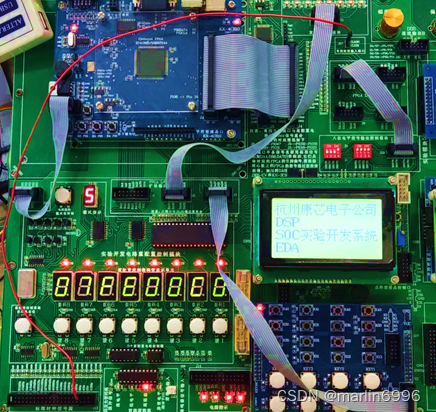

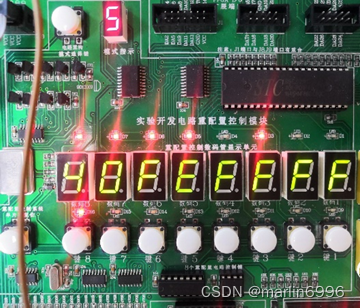

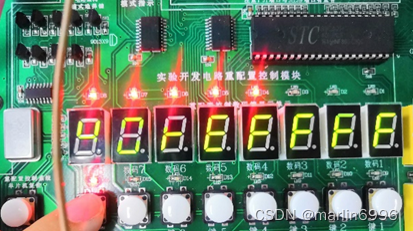

(1)连续节拍发生电路设计:主系统时钟源接4Hz

发光管D1、D2、D3、D4分别显示T1、T2、T3、T4的输出电平(依次循环点亮,从右至左)

结果分析:

实验中选择实验电路模式为5,测试时会发现当RST1为低电平时,T1输出为“1”,而T2、T3、T4输出为“0”;当RST1由低电平变为高电平后,T1~T4将在CLK1的输入脉冲作用下,周期性地轮流输出正脉冲,机器进入连续运行状态结合课堂知识易知实验结果正确。

(2)原理图2:

实验结果:

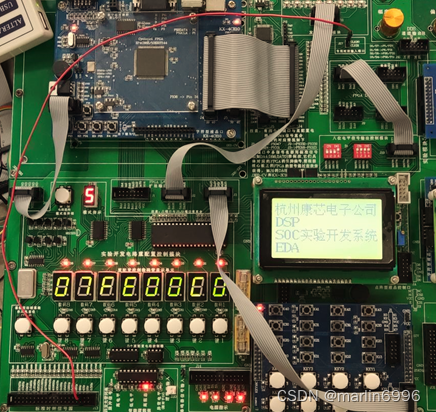

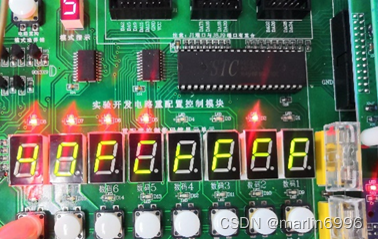

单步节拍发生电路设计: 主系统时钟源接4Hz

每当RST1出现一个负脉冲后发光管D1、D2、D3、D4分别显示T1、T2、T3、T4的输出电平(依次循环点亮,从右至左,手在控制负脉冲产生)

结果分析:

实验中选择实验电路模式为5,测试时会发现电路每当RST1出现一个负脉冲后,仅输出一组T1、T2、T3、T4节拍信号,直到RST1出现下一个负脉冲。结合课堂知识易知实验结果正确。并且实验结果的波形图和预期波形图相同。

最后

以上就是落后西牛最近收集整理的关于山东大学计算机组成与设计实验七 节拍脉冲发生器时序电路的全部内容,更多相关山东大学计算机组成与设计实验七内容请搜索靠谱客的其他文章。

发表评论 取消回复