我是靠谱客的博主 热情眼神,这篇文章主要介绍南京邮电大学电工电子(数电)实验报告——二进制全加器 & 数据选择器 & 集成触发器一、设计二进制全加器二、数据选择器及应用三、集成触发器及应用,现在分享给大家,希望可以做个参考。

文章目录

- 一、设计二进制全加器

- (1)实验目的

- (2)设计原理或设计过程

- (3)实验电路图

- (4)RTL代码设计(加分项)

- (5)ISE原理图输入的实验数据分析和实验结果

- 二、数据选择器及应用

- (1)实验目的

- (2)实验原理或设计过程

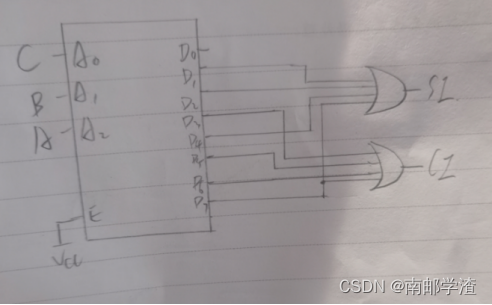

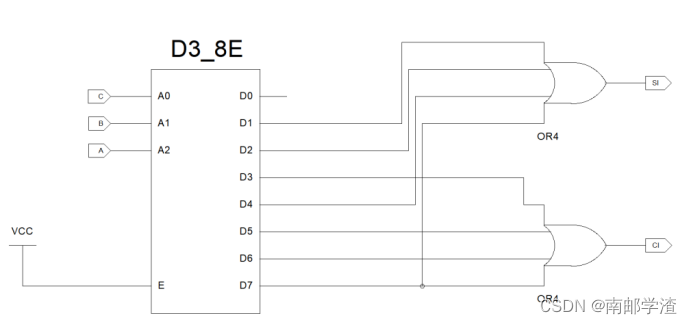

- (3)实验电路图

- (4)RTL代码设计(加分项)

- (5)ISE原理图输入的实验数据分析和实验结果

- 三、集成触发器及应用

- (1)实验目的

- (2)实验原理或设计过程

- (3)实验电路图

- (4)RTL代码设计(加分项)

- (5)ISE原理图输入的实验数据分析和实验结果

一、设计二进制全加器

(1)实验目的

1、掌握常用译码器的工作原理与逻辑功能。

2、了解动态扫描显示电路的工作原理与优缺点。

3、掌握十进制数字动态显示电路的设计方法。

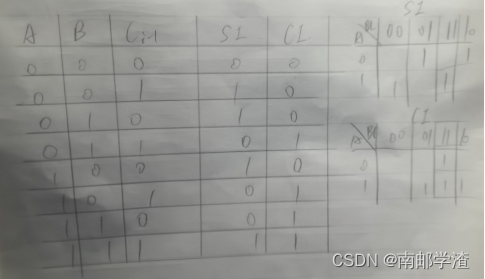

(2)设计原理或设计过程

(3)实验电路图

(4)RTL代码设计(加分项)

- RTL代码

module full_adder(

input wire in1,

input wire in2,

input wire cin,

output wire cout,

output wire sum

);

wire sum0;

wire cout0;

wire cout1;

assign {cout0,sum0}=in1+in2;

assign {cout1,sum}=cin+sum0;

assign cout=cout0 | cout1;

endmodule

- 仿真测试模块代码

三个输入端产生0到1的随机数。

`timescale 1ns/1ns

module full_adder_tb;

reg in1;

reg in2;

reg cin;

wire cout;

wire sum;

full_adder full_adder(

.in1(in1),

.in2(in2),

.cin(cin),

.cout(cout),

.sum(sum)

);

initial begin

in1=0;

in2=0;

cin=0;

end

always #10 in1<={$random}%2;

always #10 in2<={$random}%2;

always #10 cin<={$random}%2;

initial begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t: in1=%d in2=%d cin=%d cout=%d sum=%d",$time,in1,in2,cin,cout,sum);

end

endmodule

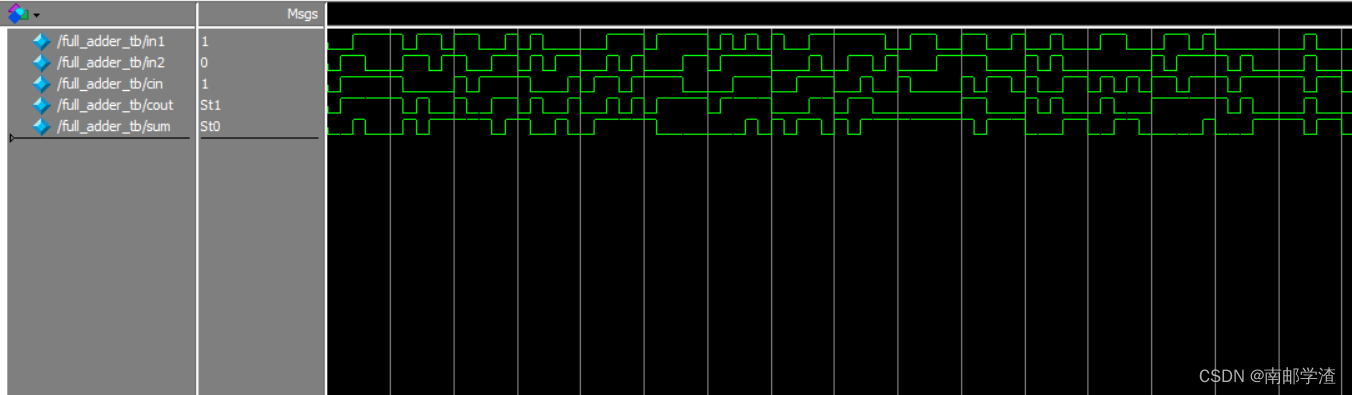

- 仿真波形图

(5)ISE原理图输入的实验数据分析和实验结果

二、数据选择器及应用

(1)实验目的

1、熟悉中规模集成电路数据选择器的工作原理与逻辑功能。

2、掌握数据选择器的应用。

(2)实验原理或设计过程

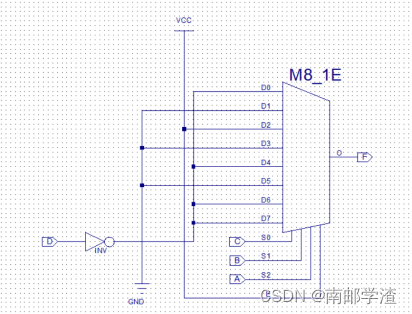

1.用数据选择器M8_1E实现函数F=(m0,m4,m5.m8.m12,m14)

用M8_1E,画出F的卡诺图,降一维,实现电路。

(3)实验电路图

(4)RTL代码设计(加分项)

- RTL代码

module mux(

input wire A,

input wire B,

input wire C,

input wire D,

output reg F

);

always @(*)

case({C,B,A})

3'd0,3'd4,3'd6,3'd7 : F = ~D;

3'd1,3'd3,3'd5 : F = 1'b0;

3'd2 : F = 1'b1;

endcase

endmodule

- 仿真测试模块代码

`timescale 1ns/1ns

module mux_tb;

reg A;

reg B;

reg C;

reg D;

wire F;

mux mux_inst(

.A(A),

.B(B),

.C(C),

.D(D),

.F(F)

);

initial begin

A=1'b0;

B=1'b0;

C=1'b0;

D=1'b0;

end

always #10 A <= {$random}%2;

always #10 B <= {$random}%2;

always #10 C <= {$random}%2;

always #10 D <= {$random}%2;

endmodule

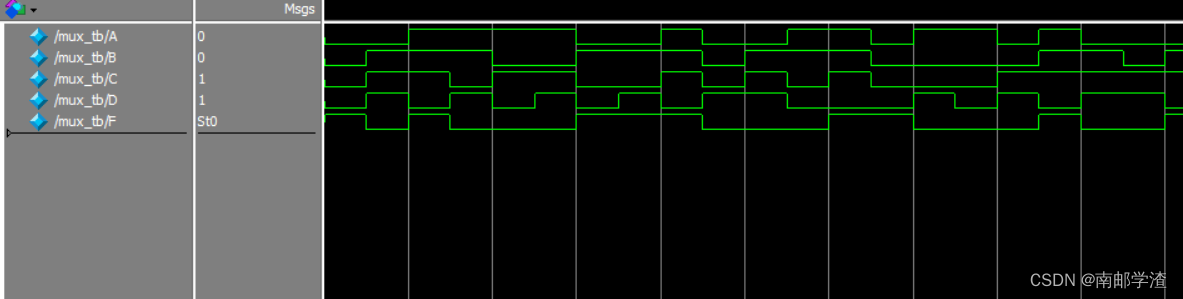

- 仿真波形图

(5)ISE原理图输入的实验数据分析和实验结果

三、集成触发器及应用

(1)实验目的

1、掌握集成触发器的逻辑功能。

2、熟悉用触发器构成计数器的设计方法。

3、掌握集成触发器的基本应用。

(2)实验原理或设计过程

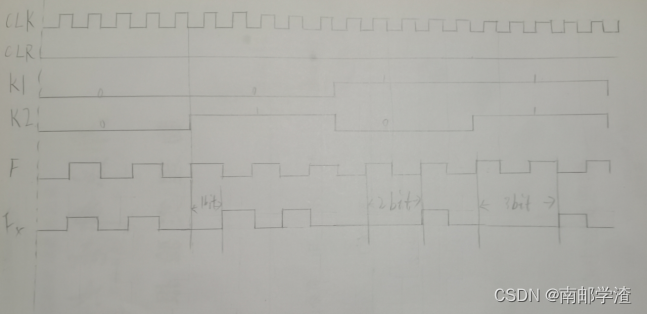

设计一个3bit可控延时电路,该电路有一个输入信号CP,一个串行输入信号F1,一个串行输出信号F2,F1和F2与CP同步,另有两个控制信号K1和K2。对该电路的逻辑功能要求:(1)当K1K2=00,F1和F2没有延时;(2)当K1K2=01时,延时一个时钟周期;(3)当K1K2=10,延时两个时钟周期;(4)当K1K2=11,延时三个时钟周期。

①串行输入信号F1:可用2位二进制计数器的Tc输出端。

②3bit延时电路:运用D触发器实现,将F1置于触发器D端,在后续CP作用下,触发器Q端输出即为延迟一个时钟周期的F2,将3个D触发器级联,可实现3bit延时。

③控制电路:利用四选一数据选择器在开关控制下依次选择F1,Q1,Q2,Q3到数据选择器的输出端即可。

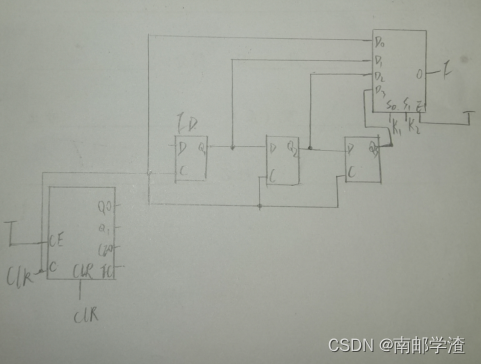

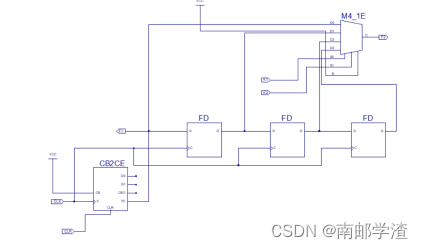

(3)实验电路图

(4)RTL代码设计(加分项)

- RTL代码

module bit_3(

input wire clk,

input wire [1:0]K,

input wire clr,

output reg F1,

output reg F2

);

reg Q1;

reg Q2;

reg Q3;

reg clk_4;

reg [1:0]cnt;

always @(posedge clk or negedge clr)

if(!clr)

cnt <= 1'b0;

else if(cnt == 2'd3)

cnt <= 1'b0;

else

cnt <= cnt + 1'b1;

always @(posedge clk or negedge clr)

if(!clr)

clk_4 <= 1'b0;

else if(cnt == 2'd2)

clk_4 <= ~clk_4;

always @(posedge clk_4 or negedge clr)

if(!clr)

F1 <= 1'b0;

else

F1 <= ~F1;

always @(posedge clk or negedge clr)

if(!clr) begin

Q1 <= 1'b0;

Q2 <= 1'b0;

Q3 <= 1'b0;

end

else begin

Q1 <= F1;

Q2 <= Q1;

Q3 <= Q2;

end

always @(*)

if(!clr)

F2 <= 1'b0;

else begin

case(K)

2'b00 : F2 = F1;

2'b01 : F2 = Q1;

2'b10 : F2 = Q2;

2'b11 : F2 = Q3;

endcase

end

endmodule

- 仿真测试模块代码

`timescale 1ns/1ns

`define clk_period 20

module bit_3_tb;

reg clk;

reg [1:0]K;

reg clr;

wire F1;

wire F2;

bit_3 bit_3_inst(

.clk(clk),

.K(K),

.clr(clr),

.F1(F1),

.F2(F2)

);

initial begin

clr = 1'b0;

K = 1'b0;

#20;

clr = 1'b1;

K = 2'b00;

#(`clk_period*50);

K = 2'b01;

#(`clk_period*50);

K = 2'b10;

#(`clk_period*50);

K = 2'b11;

#(`clk_period*50);

end

initial clk = 1'b1;

always #(`clk_period/2) clk = ~clk;

endmodule

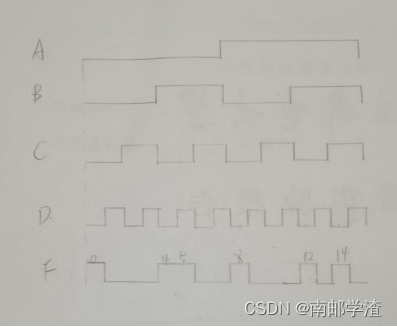

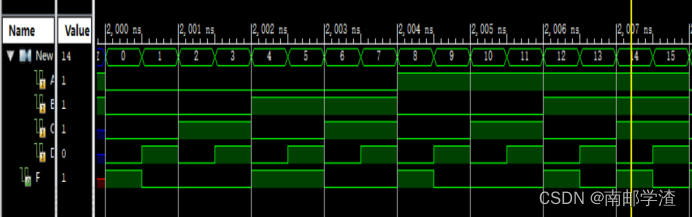

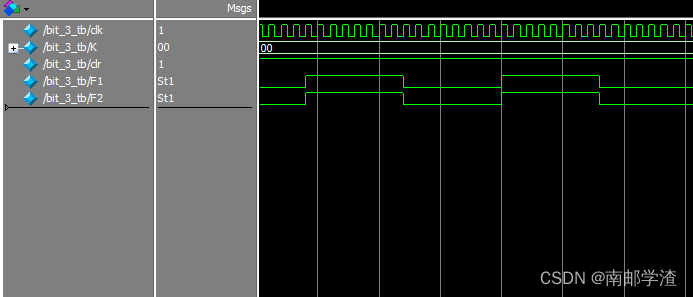

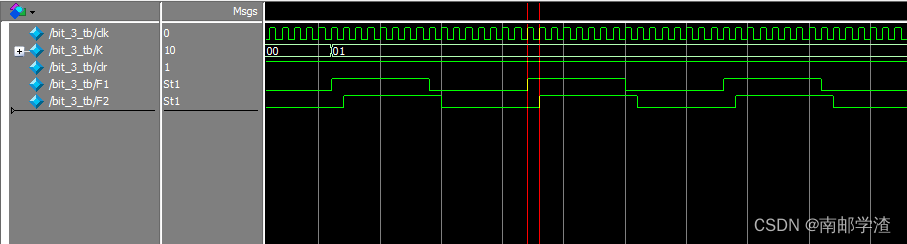

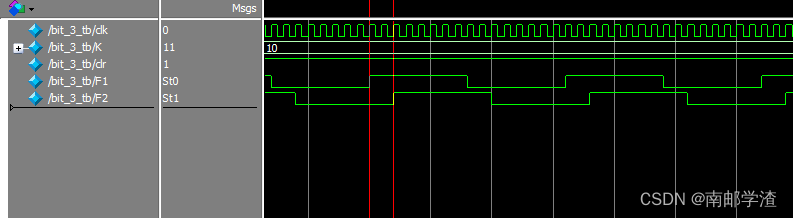

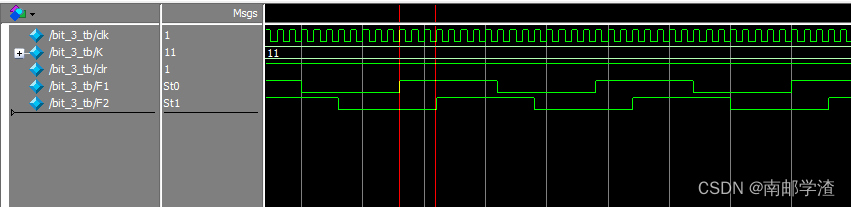

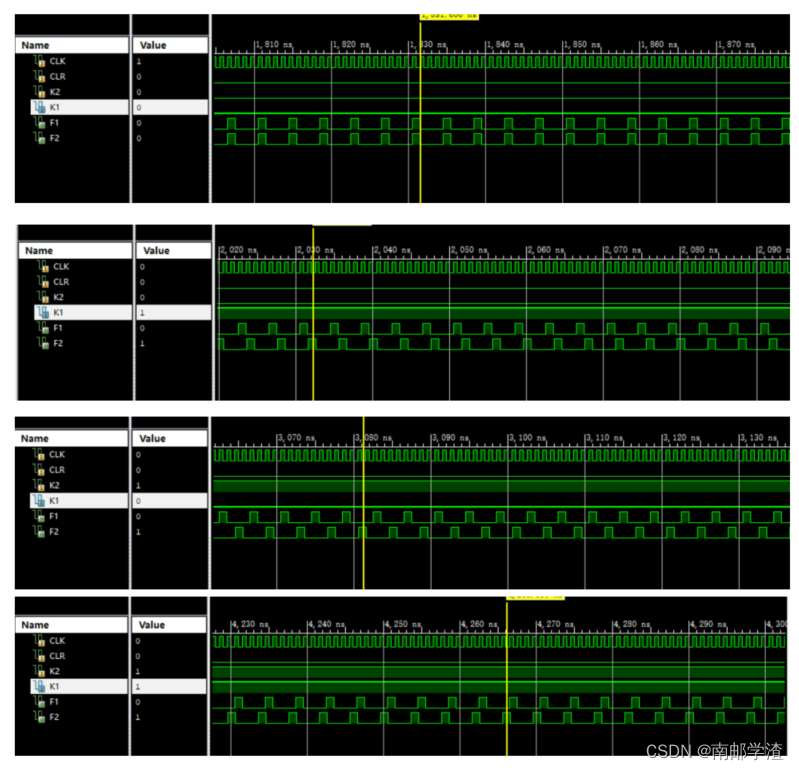

- 仿真波形图

K=00

K=01

K=10

K=11

(5)ISE原理图输入的实验数据分析和实验结果

最后

以上就是热情眼神最近收集整理的关于南京邮电大学电工电子(数电)实验报告——二进制全加器 & 数据选择器 & 集成触发器一、设计二进制全加器二、数据选择器及应用三、集成触发器及应用的全部内容,更多相关南京邮电大学电工电子(数电)实验报告——二进制全加器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复