文章目录

- 逻辑变量与逻辑函数

- 逻辑运算

- 基本逻辑运算及对应的逻辑门

- 1.与运算

- 与逻辑举例

- 状态表与真值表

- 与逻辑符号

- 与逻辑表达式

- 与门电路

- 2. 或运算

- 或逻辑举例

- 电路状态表

- 状态表与真值表

- 或逻辑符号

- 或逻辑表达式

- 或门电路

- 3. 非运算

- 非逻辑举例

- 电路状态表

- 状态表与真值表

- 非逻辑符号

- 非逻辑表达式

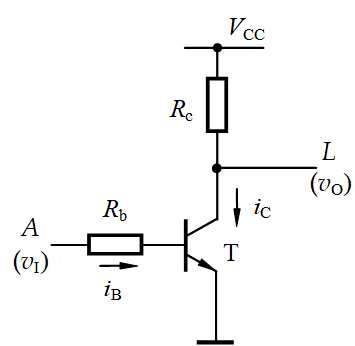

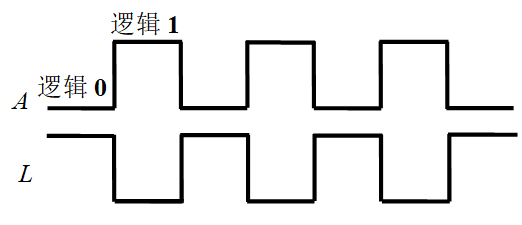

- 三极管实现的非门电路

- 常用复合逻辑运算及对应的逻辑门

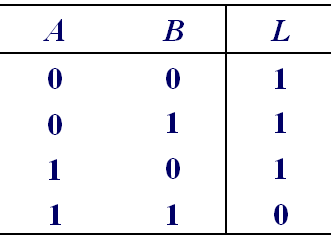

- 1. 与非运算

- 逻辑真值表

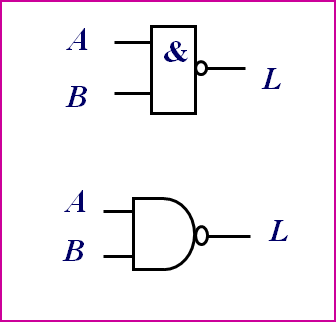

- 与非逻辑符号

- 与非逻辑表达式

- 2. 或非运算

- 逻辑真值表

- 或非逻辑符号

- 或非逻辑表达式

- 3. 异或逻辑

- 异或逻辑真值表

- 异或逻辑符号

- 异或逻辑表达式

- 4.同或运算

- 同或逻辑真值表

- 同或逻辑逻辑符号

- 同或逻辑表达式

- 集成逻辑门电路简介

- 三态门

- 三态输出门电路逻辑符号

- 三态输出门的真值表

- 应用举例

- (1) 构成总线传输结构

- (2) 实现信号的双向传输

逻辑变量与逻辑函数

逻辑是指事物因果之间所遵循的规律。为了避免用冗繁的文字来描述逻辑问题,逻辑代数采用逻辑变量和一套运算符组成逻辑函数表达式来描述事物的因果关系。

逻辑代数中的变量称为逻辑变量,一般用大写字母A、B、C…表示。逻辑变量的取值只有两种,即逻辑0和逻辑1。 0和1称为逻辑常量。这里0和1本身并没有数值意义,它仅仅是一种符号,代表事物矛盾双方的两种状态。

数字电路的输出与输入之间的关系是一种因果关系, 因此它可以用逻辑函数来描述,并称为逻辑电路。

对于任何一个电路,若输入逻辑变量A、 B、 C … 的取值确定后,其输出逻辑变量L的值也被唯一地确定了,则可以称L是A、 B、 C … 的逻辑函数, 并记为

L

=

f

(

A

,

B

,

C

,

⋯

)

begin{array}{c} L = f(A, B, C, cdots) end{array}

L=f(A,B,C,⋯)

逻辑运算

当0和1表示逻辑状态时,两个二进制数码按照某种特定的因果关系进行的运算。

基本逻辑运算及对应的逻辑门

在逻辑代数中,有与、或、非三种基本的逻辑运算。还有 与非、或非、同或、异或等常用的复合逻辑运算。

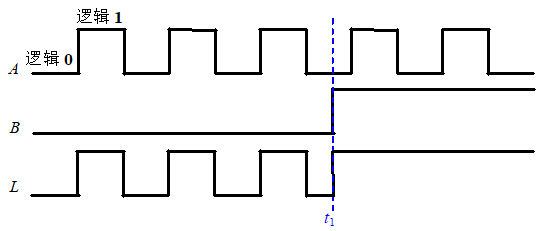

逻辑运算的描述方式:逻辑代数表达式、真值表、逻辑图、卡诺图、波形图和硬件描述语言(HDL) 等。

1.与运算

(1) 与逻辑:只有当决定某一事件的条件全部具备时,这一事件才会发生。这种因果关系称为与逻辑关系。

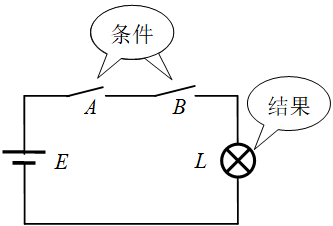

与逻辑举例

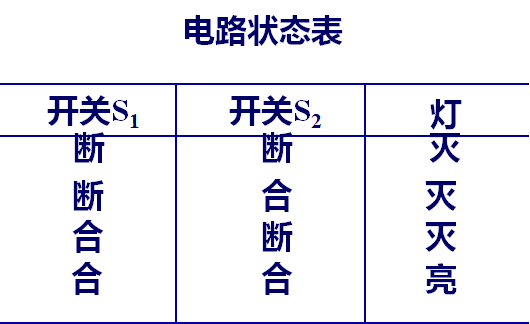

状态表与真值表

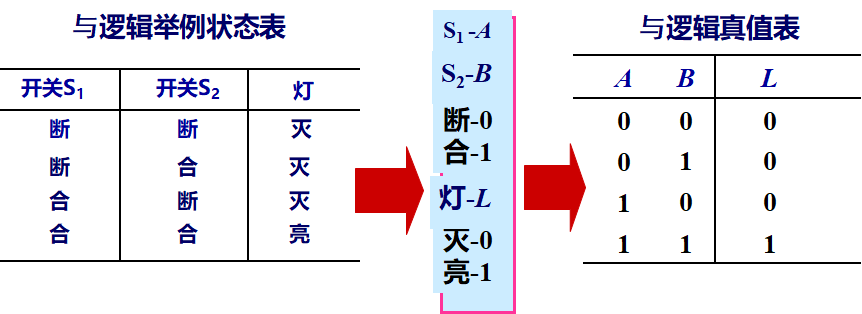

与逻辑符号

与逻辑表达式

与逻辑:

L

=

A

⋅

B

=

A

B

L = A ·B= AB

L=A⋅B=AB

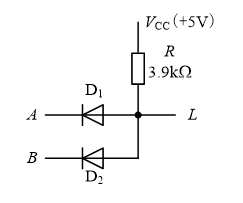

与门电路

实现与逻辑运算(即满足与逻辑真值表)的电子电路称为与门电路(简称与门)

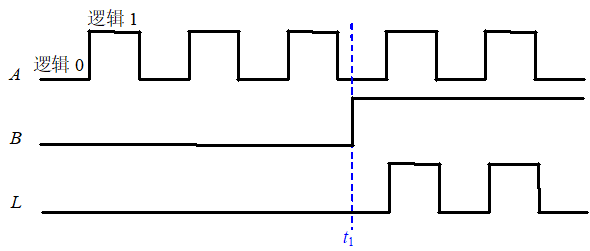

2. 或运算

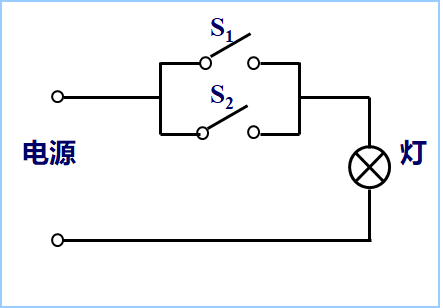

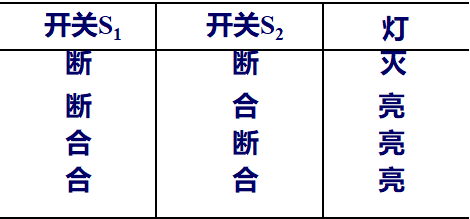

只要在决定某一事件的各种条件中,有一个或几个条件具备时,这一事件就会发生。这种因果关系称为或逻辑关系。

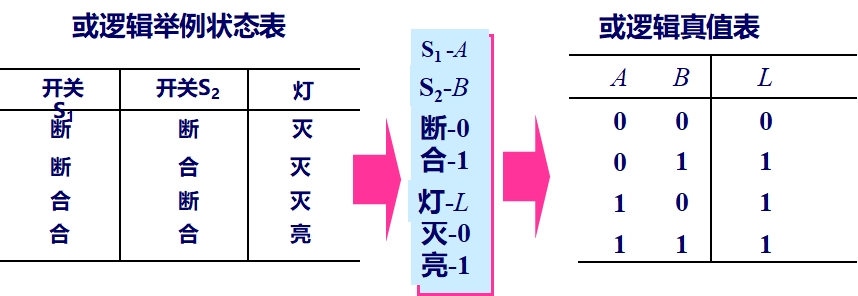

或逻辑举例

电路状态表

状态表与真值表

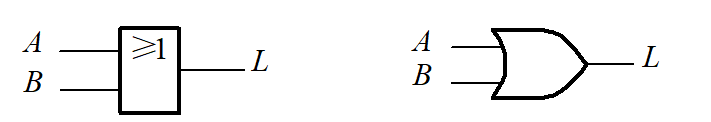

或逻辑符号

或逻辑表达式

或逻辑:

L

=

A

+

B

L = A +B

L=A+B

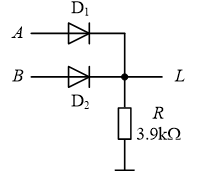

或门电路

实现或逻辑运算(即满足或逻辑真值表)的电子电路称为或门电路(简称或门)。

3. 非运算

事件发生的条件具备时,事件不会发生;事件发生的条件不具备时,事件发生。这种因果关系称为非逻辑关系。

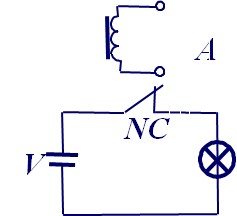

非逻辑举例

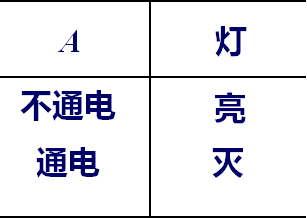

电路状态表

状态表与真值表

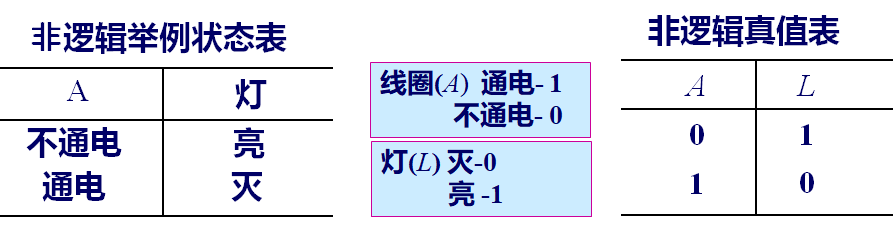

非逻辑符号

非逻辑表达式

L = A ˉ L=bar{A} L=Aˉ

三极管实现的非门电路

常用复合逻辑运算及对应的逻辑门

在逻辑代数中,有与、或、非三种基本的逻辑运算。还有 与非、或非、同或、异或等常用的复合逻辑运算。

逻辑运算的描述方式:逻辑代数表达式、真值表、逻辑图、卡诺图、波形图和硬件描述语言(HDL) 等。

1. 与非运算

两输入变量与非

逻辑真值表

与非逻辑符号

与非逻辑表达式

L = A ⋅ B ‾ L=overline{A cdot B} L=A⋅B

2. 或非运算

两输入变量或非

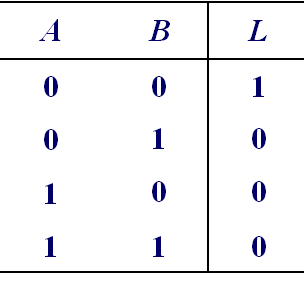

逻辑真值表

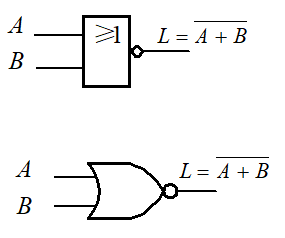

或非逻辑符号

或非逻辑表达式

L = A + B ‾ L=overline{A+B} L=A+B

3. 异或逻辑

若两个输入变量的值相异,输出为1,否则为0。

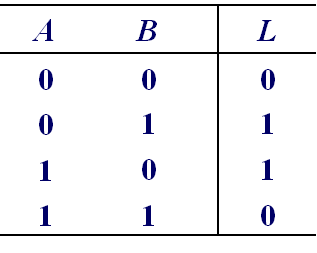

异或逻辑真值表

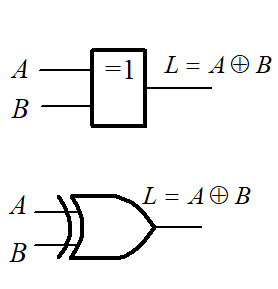

异或逻辑符号

异或逻辑表达式

L = A ˉ B + A B ˉ = A ⊕ B L=bar{A} B+A bar{B}=A oplus B L=AˉB+ABˉ=A⊕B

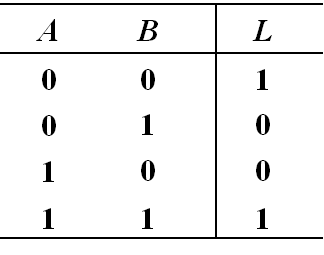

4.同或运算

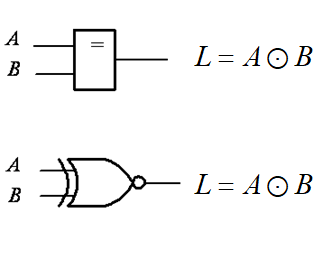

若两个输入变量的值相同,输出为1,否则为0。

同或逻辑真值表

同或逻辑逻辑符号

同或逻辑表达式

L = A ˉ B ˉ + A B = A ⊙ B L=bar{A} bar{B}+A B=A odot B L=AˉBˉ+AB=A⊙B

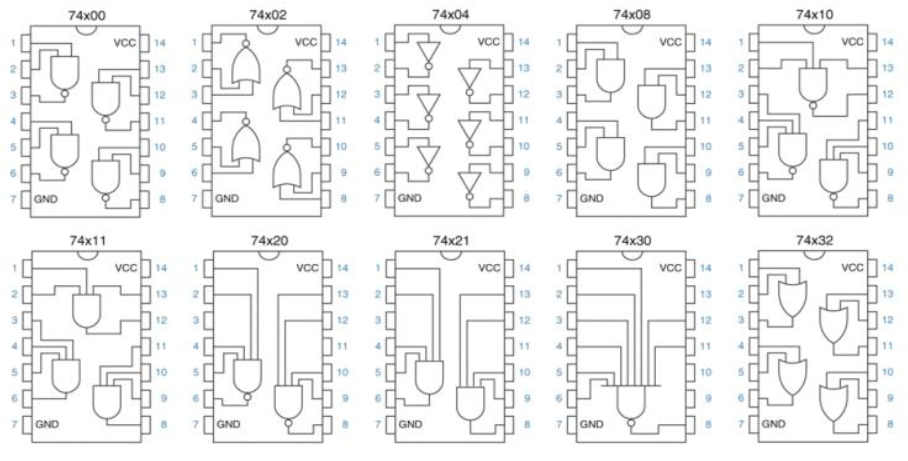

集成逻辑门电路简介

逻辑运算都可以用SSI集成电路实现 。

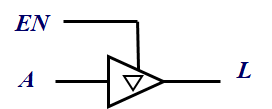

三态门

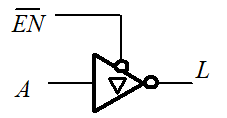

三态输出门电路逻辑符号

高电平有效的同相三态门

低电平使能的三态输出非门电路

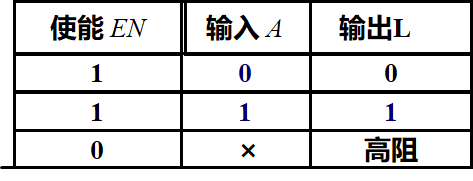

三态输出门的真值表

高电平使能的三态输出门的真值表

低电平使能的三态输出门的真值表

应用举例

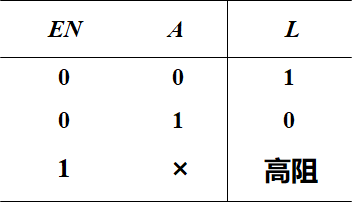

(1) 构成总线传输结构

为了减少复杂的系统中各个单元电路之间的连线,数字系统中信号的传输常常采取一种称为“总线”(Bus)的结构形式,以达到在同一导线上分时传递若干路信号的目的。

工作时只要控制各个 E N n EN_n ENn端的逻辑电平,保证在任何时刻仅有一个三态输出门电路被使能,就可以把各个输出信号按要求顺序送到总线上,而互不干扰。

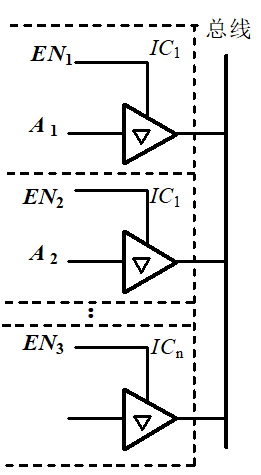

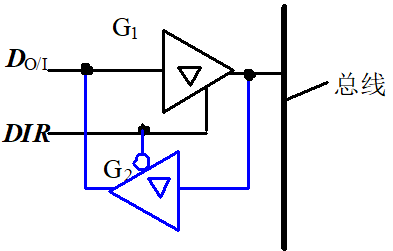

(2) 实现信号的双向传输

DIR (EN) 为传送控制信号。

当DIR=1时, G1工作,G2为高阻态,数据线DO/I上的数据经G1送到总线上;

当DIR=0时, G2工作, 而G1为高阻态,来自总线的数据经G2送到的DO/I线上。

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月

最后

以上就是彪壮冰棍最近收集整理的关于FPGA:逻辑运算及逻辑门的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复