我是靠谱客的博主 甜甜口红,这篇文章主要介绍【FPGA】EDA技术综合设计 带同步复位和使能控制端的4位二进制加1计数器带同步复位和使能控制端的4位二进制加1计数器:,现在分享给大家,希望可以做个参考。

带同步复位和使能控制端的4位二进制加1计数器:

1、设计原理

计数器的原理本质上和分频器一样,对板子上的原有时钟的周期进行计数,达到一定周期后进行重新计数,这时记为一个数,Q加1,达到最大值后,Q清零,使能端en,当en为低电平无效的时候,不进行计数,Q保持为0,按下复位键后计数器进行重新计数。

2、设计源文件

`timescale 1ns / 1ps

/

// Create Date: 2022/06/07 21:13:22

// Module Name: couter_4

/

module couter_4(clk,rst,en,D,W, Q);

input clk;//时钟输入

input rst;//复位

input en;//使能

output reg[6:0]D;//段选

output reg[1:0]W;//位选

output reg[3:0]Q;//四位二进制输出

reg [25 : 0] cnt_reg=7'h0000000; //计数值

reg[13:0]x=14'b00000000000000;//两位数码管的段码组合

initial begin//初始化

D=7'b0000000;//不亮

Q=4'b0000;

W=2'b00;

end

always @(posedge clk)

begin

if(en==1)

begin

if (rst == 1) //判断是否清零复位

cnt_reg <= 0; //如果是,清零

else

cnt_reg <= cnt_reg + 1; //没有清零,能使能,计数器才加一

end

else

cnt_reg <= 0;

end

//动态显示计数

reg [19:0] clkdiv;

always@(posedge clk)

begin

if(rst==1)

clkdiv<=0;

else

clkdiv<=clkdiv+1;

end

wire s; //位选选择

assign s=clkdiv[19];//令s为clkdiv的第一个值,实现较长时间内s的状态改变

//位选动态显示

always@(*)

begin

W=2'b00;

W[s]=1;//第s位选中的位选端打开,进行显示

end

//对段选码输出十位和个位的选择

always@(*)

case(s)

0:D=x[6:0];

1:D=x[13:7];

default:;

endcase

always @(posedge clk)

begin

if (en == 1) //判断是否使能

begin

if(rst == 1)//判断是否复位

Q <=4'b0000;//如果是,清零

else

if(cnt_reg == 7'h5f5e100)//100000000,1hz

Q<=Q+1;

end

else

Q <=4'b0000;

end

always@(*)

begin

case(Q)

4'b0000:x = 14'b01111110111111; // 00

4'b0001:x = 14'b01111110000110; // 01

4'b0010:x = 14'b01111111011011; // 02

4'b0011:x = 14'b01111111001111; // 03

4'b0100:x = 14'b01111111100110; // 04

4'b0101:x = 14'b01111111101101; // 05

4'b0110:x = 14'b01111111111101; // 06

4'b0111:x = 14'b01111110000111; // 07

4'b1000:x = 14'b01111111111111; // 08

4'b1001:x = 14'b01111111100111; // 09

4'b1010:x = 14'b00001100111111; // 10

4'b1011:x = 14'b00001100000110; // 11

4'b1100:x = 14'b00001101011011; // 12

4'b1101:x = 14'b00001101001111; // 13

4'b1110:x = 14'b00001101100110; // 14

4'b1111:x = 14'b00001101101101; // 15

default:x = 14'b00000000000000;

endcase

end

endmodule

3、仿真测试文件

`timescale 1ns / 1ps

module sim_couter4();

reg clk;

reg rst;

reg en;

wire [6:0] D; //段选信号

wire [1:0] W; //片选信号

wire [3:0] Q; //四位二进制数计数器的值

couter_4 u1(clk,rst,en,D,W, Q);

parameter PERIOD = 10;

always begin

clk = 0;//开始时clk为0

#(PERIOD/2) clk = 1;

#(PERIOD/2);

end

initial begin

rst=1;//开始时清零位为1

en=0;//没有使能

#10

rst=0;//改变rst状态

en=1;//改变使能状态

#10

rst=1;

#10

rst=0;

end

endmodule

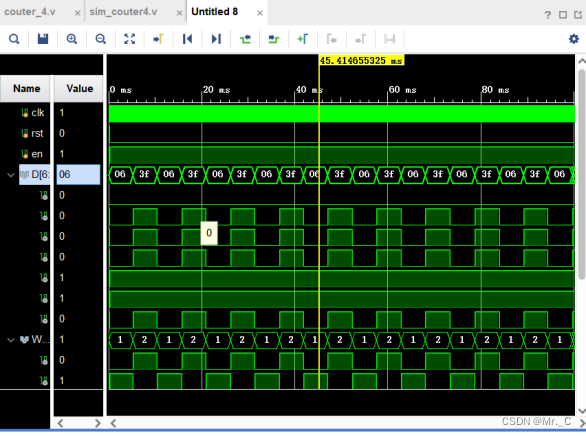

仿真结果

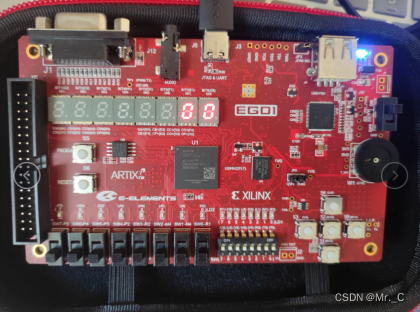

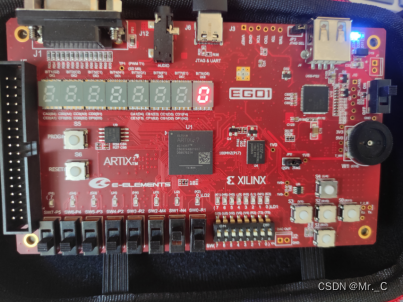

实验板部分结果

最后

以上就是甜甜口红最近收集整理的关于【FPGA】EDA技术综合设计 带同步复位和使能控制端的4位二进制加1计数器带同步复位和使能控制端的4位二进制加1计数器:的全部内容,更多相关【FPGA】EDA技术综合设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复