本实训帮助大家掌握常用组合逻辑功能模块的Verilog编程设计,包括多路选择器、译码器、优先编码器、比较器、数码驱动器、ALU。

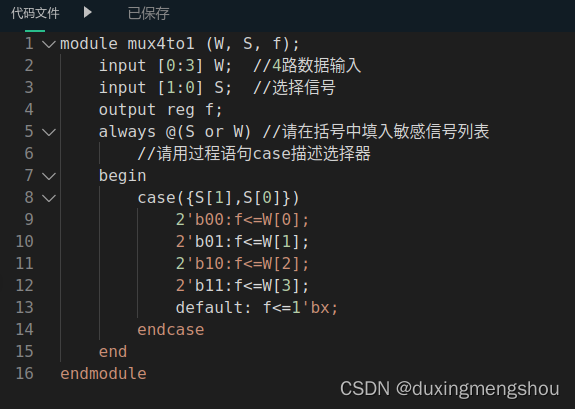

第1关:4选1多路选择器设计

本关任务:使用Verilog HDL描述4选1多路选择器并完成在线评测。

module mux4to1 (W, S, f);

input [0:3] W; //4路数据输入

input [1:0] S; //选择信号

output reg f;

always @(S or W) //请在括号中填入敏感信号列表

//请用过程语句case描述选择器

begin

case({S[1],S[0]})

2'b00:f<=W[0];

2'b01:f<=W[1];

2'b10:f<=W[2];

2'b11:f<=W[3];

default: f<=1'bx;

endcase

end

endmodule 第2关:3-8译码器设计

本关任务:使用Verilog HDL描述3-8译码器,并完成在线评测。

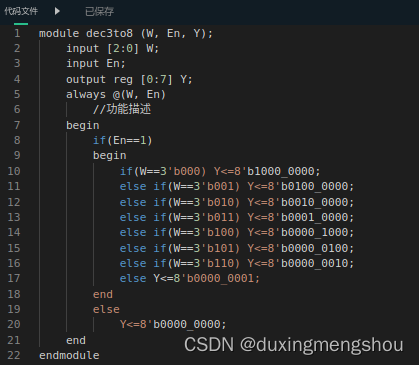

module dec3to8 (W, En, Y);

input [2:0] W;

input En;

output reg [0:7] Y;

always @(W, En)

//功能描述

begin

if(En==1)

begin

if(W==3'b000) Y<=8'b1000_0000;

else if(W==3'b001) Y<=8'b0100_0000;

else if(W==3'b010) Y<=8'b0010_0000;

else if(W==3'b011) Y<=8'b0001_0000;

else if(W==3'b100) Y<=8'b0000_1000;

else if(W==3'b101) Y<=8'b0000_0100;

else if(W==3'b110) Y<=8'b0000_0010;

else Y<=8'b0000_0001;

end

else

Y<=8'b0000_0000;

end

endmodule

第3关:4-2优先编码器设计

本关任务:使用Verilog HDL描述4-2优先编码器,并完成在线评测。

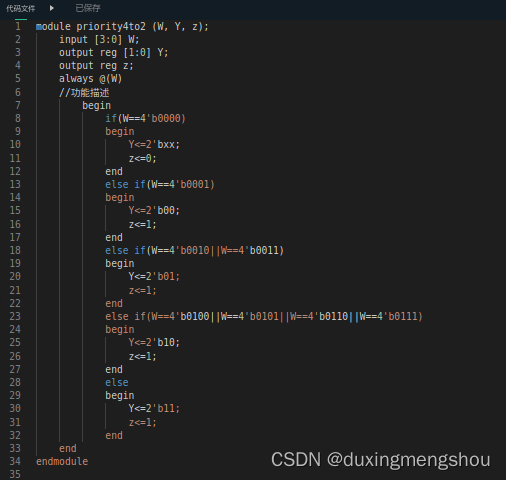

module priority4to2 (W, Y, z);

input [3:0] W;

output reg [1:0] Y;

output reg z;

always @(W)

//功能描述

begin

if(W==4'b0000)

begin

Y<=2'bxx;

z<=0;

end

else if(W==4'b0001)

begin

Y<=2'b00;

z<=1;

end

else if(W==4'b0010||W==4'b0011)

begin

Y<=2'b01;

z<=1;

end

else if(W==4'b0100||W==4'b0101||W==4'b0110||W==4'b0111)

begin

Y<=2'b10;

z<=1;

end

else

begin

Y<=2'b11;

z<=1;

end

end

endmodule

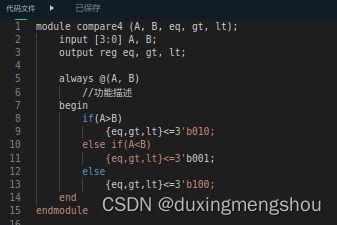

第4关:4位无符号比较器设计

本关任务:使用Verilog HDL描述4位无符号比较器并完成在线评测。

module compare4 (A, B, eq, gt, lt);

input [3:0] A, B;

output reg eq, gt, lt;

always @(A, B)

//功能描述

begin

if(A>B)

{eq,gt,lt}<=3'b010;

else if(A<B)

{eq,gt,lt}<=3'b001;

else

{eq,gt,lt}<=3'b100;

end

endmodule第5关:数码驱动器设计

本关任务:实验Verilog HDL描述7段数码驱动器电路,并完成在线评测。

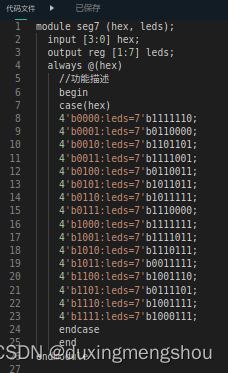

module seg7 (hex, leds);

input [3:0] hex;

output reg [1:7] leds;

always @(hex)

//功能描述

begin

case(hex)

4'b0000:leds=7'b1111110;

4'b0001:leds=7'b0110000;

4'b0010:leds=7'b1101101;

4'b0011:leds=7'b1111001;

4'b0100:leds=7'b0110011;

4'b0101:leds=7'b1011011;

4'b0110:leds=7'b1011111;

4'b0111:leds=7'b1110000;

4'b1000:leds=7'b1111111;

4'b1001:leds=7'b1111011;

4'b1010:leds=7'b1110111;

4'b1011:leds=7'b0011111;

4'b1100:leds=7'b1001110;

4'b1101:leds=7'b0111101;

4'b1110:leds=7'b1001111;

4'b1111:leds=7'b1000111;

endcase

end

endmodule

第6关:ALU设计

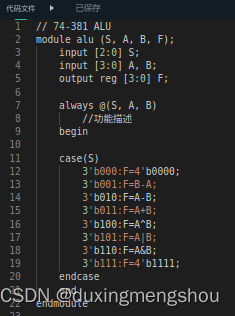

本关任务:用Verilog描述74-381ALU,并完成在线评测。

// 74-381 ALU

module alu (S, A, B, F);

input [2:0] S;

input [3:0] A, B;

output reg [3:0] F;

always @(S, A, B)

//功能描述

begin

case(S)

3'b000:F=4'b0000;

3'b001:F=B-A;

3'b010:F=A-B;

3'b011:F=A+B;

3'b100:F=A^B;

3'b101:F=A|B;

3'b110:F=A&B;

3'b111:F=4'b1111;

endcase

end

endmodule

最后

以上就是糊涂皮皮虾最近收集整理的关于常用组合电路模块设计(Verilog)——头歌平台作业的全部内容,更多相关常用组合电路模块设计(Verilog)——头歌平台作业内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复