名词解释

HDL :Hardware Description Language,硬件描述语言

EDA:Electronic Design Automation,电子设计自动化

FPGA:Field Programmable Gate Array,现场可编程门阵列

IP:Intelligent Property,知识产权

IC:Integrated Circuit,集成电路

RTL:Register Transfer Level,寄存器传输级

简答题

1.'timescale <时间单位>/<时间精度>

时间单位:用于定义模块中仿真时间和延迟时间的基准单位

时间精度:用于声明该模块仿真时间的精确程度

2.reg型数据与wire型数据的区别:

reg型数据保持最后一次的赋值,而wire型数据需要有持续的驱动。

一般情况下,reg型数据的默认初始值为不定值x,缺省时的位宽为1位。

注意:在过程块内被赋值的每一个信号都必须定义成reg型,并且只能在always或initial过程块中赋值,大多数reg型信号常常是寄存器或触发器的输出。

3.always语句和initial语句关键区别是什么,能否相互嵌套?

always语句是循环语句,只有当触发条件满足时,其后语句块才开始执行,并且触发状态会一直存在,多个always语句块并行执行;

initial语句在仿真开始时就被执行,并且只执行一次,块内语句可顺序执行也可并行执行。

不能嵌套

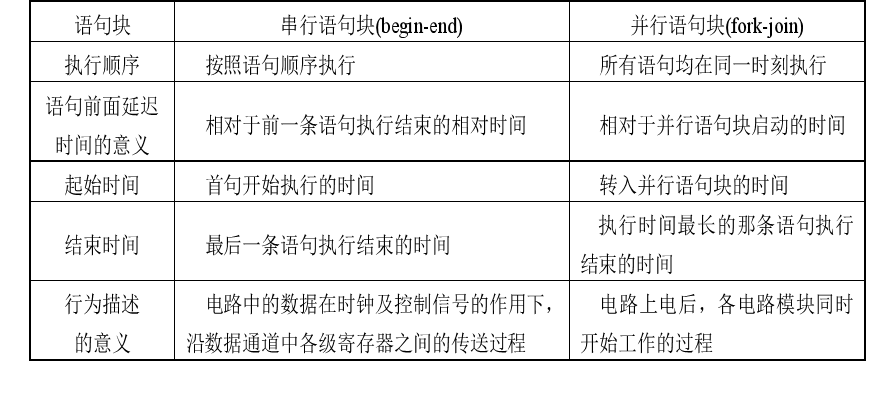

4.简述begin-end和fork-join语句块的区别。

begin-end 语句块为串行语句块,其内语句按顺行方式顺序执行,可用于可综合、仿真测试程序;

fork-join 语句块为并行语句块,其内语句按并行方式执行,不可用于可综合电路程序。

串行语句块和并行语句块的对比

5. 简述define和parameter的区别。

1)语法区别

声明 'define xx XX parameter yy=YY

使用 'xx yy

2) 作用域

define 从编译器读到这条指令开始到编译结束都有效,或者遇到 'undef 命令使之失效

parameter 作用于声明的文件

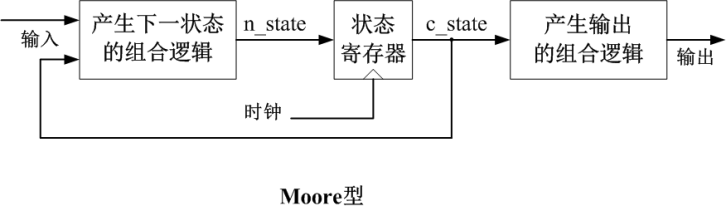

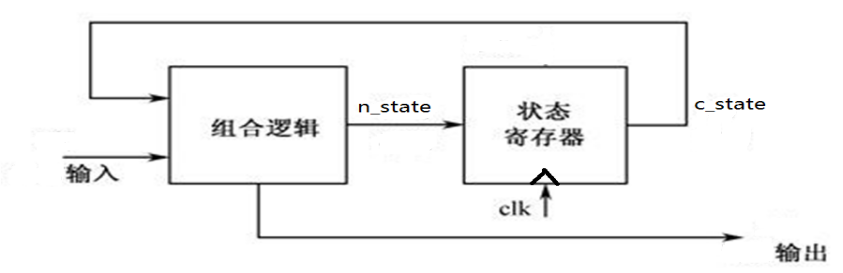

6.moore型和mealy型有什么区别?

moore: 输出只和当前状态有关;

当前状态是与输入信号有关的,只是输入与输出之间没有组合逻辑, 所以一般来说,moore的状态会多一些

mealy:输出和当前状态和输入都有关

同一个状态mealy型比moore型超时一个周期输出。状态数大于2N时,MOORE的状态更多更复杂。

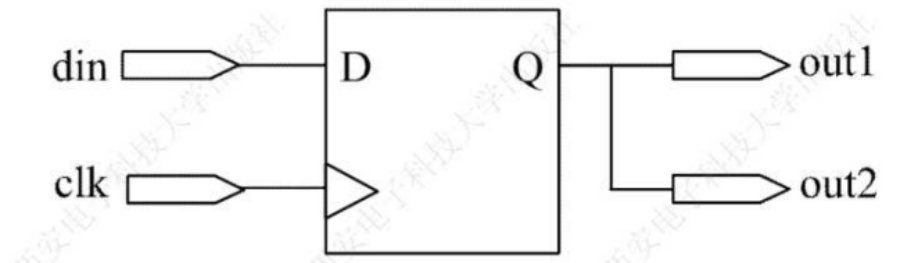

7.试举例说明阻塞赋值语句和非阻塞赋值语句的区别。

//阻塞赋值语句

always@ (posedgeg clk)

begin

out1 = din;

out2 = out1;

end

//在执行阻塞赋值语句的过程中,din的值先传给out1,然后out1的值再传给out2

//该程序段描述了一个寄存器,其电路结构图如下

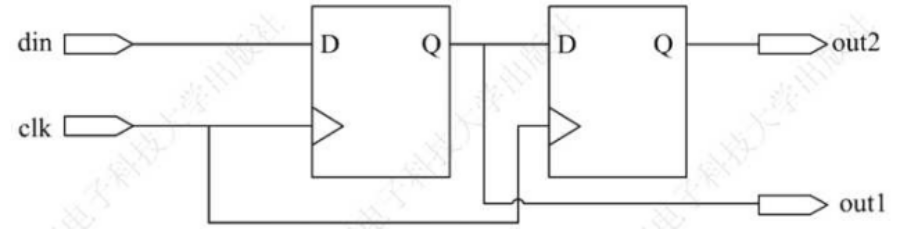

//非阻塞赋值

always@ (posedge clk)

begin

out1 <= din;

out2 <= out1;

end

//在执行非阻塞赋值语句的过程中,din的值先传给out1,同时out1的值传给out2

//该程序段描述了2个寄存器,其电路结构图如下

参考链接 http://www.doc88.com/p-9929960255990.html

最后

以上就是含糊蓝天最近收集整理的关于Verilog HDL 复习笔记(一) 名词解释简答题的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复