我是靠谱客的博主 诚心镜子,这篇文章主要介绍设计一个同步时序逻辑电路, 使得每输入4个周期的CLK脉冲, 便输出一个正脉冲, 其宽度为CLK脉冲的周期. 要求用与非门及下降沿触发的JK触发器实现. 如果要求输出脉宽为CLK脉宽, 该如何修改?,现在分享给大家,希望可以做个参考。

从题目要求中, 可以提取出以下关键信息:

①要求使用下降沿触发的JK触发器设计电路,

②如果需要使用逻辑门, 只能使用与非门.

③每输入4个周期的CLK脉冲, 便输出一个正脉冲——换种说法说就是要求设计一个同步4进制加法计数器, 并设计进位输出.

④要求输出脉冲宽度为CLK脉冲宽度, 则当进位输出和CLK信号都为高电平时, 输出才为1; 其它情况输出为0.

第一步, 设计同步4进制加法计数器.

列状态表:

| 状态表 | ||||

| Q1 | Q0 | Q1* | Q0* | Z |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

列状态激励表:

| 状态激励表 | ||||||||

| Q1 | Q0 | Q1* | Q0* | J1 | K1 | J0 | K0 | Z |

| 0 | 0 | 0 | 1 | 0 | × | 1 | × | 0 |

| 0 | 1 | 1 | 0 | 1 | × | × | 1 | 0 |

| 1 | 0 | 1 | 1 | × | 0 | 1 | × | 0 |

| 1 | 1 | 0 | 0 | × | 1 | × | 1 | 1 |

求出状态激励方程:

| J0=K0=1. | |

| J1=Q0. | |

| K1=Q0. |

求出状态方程:

| Q0*=J0Q0'+K0'Q0=Q0'. | |

| Q1*=J1Q1'+K1'Q1=Q1'Q0+Q1Q0'=Q1异或Q0. |

求出第一问的输出方程, 并按照与非式的规则进行变形:

求出第二问的输出方程, 并按照与非式的规则进行变形:

根据上面的设计, 绘制出电路原理图.

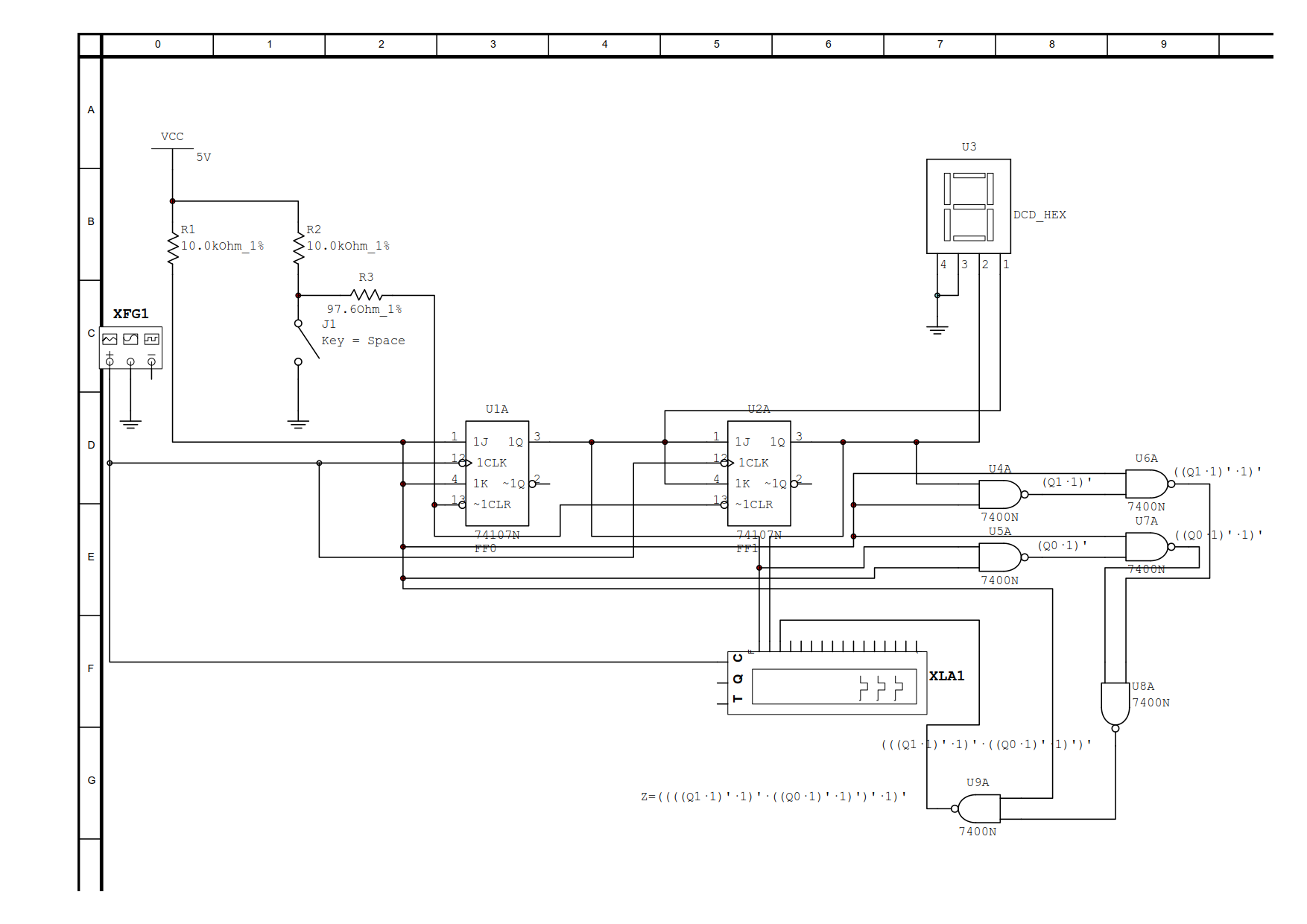

第一问原理图:

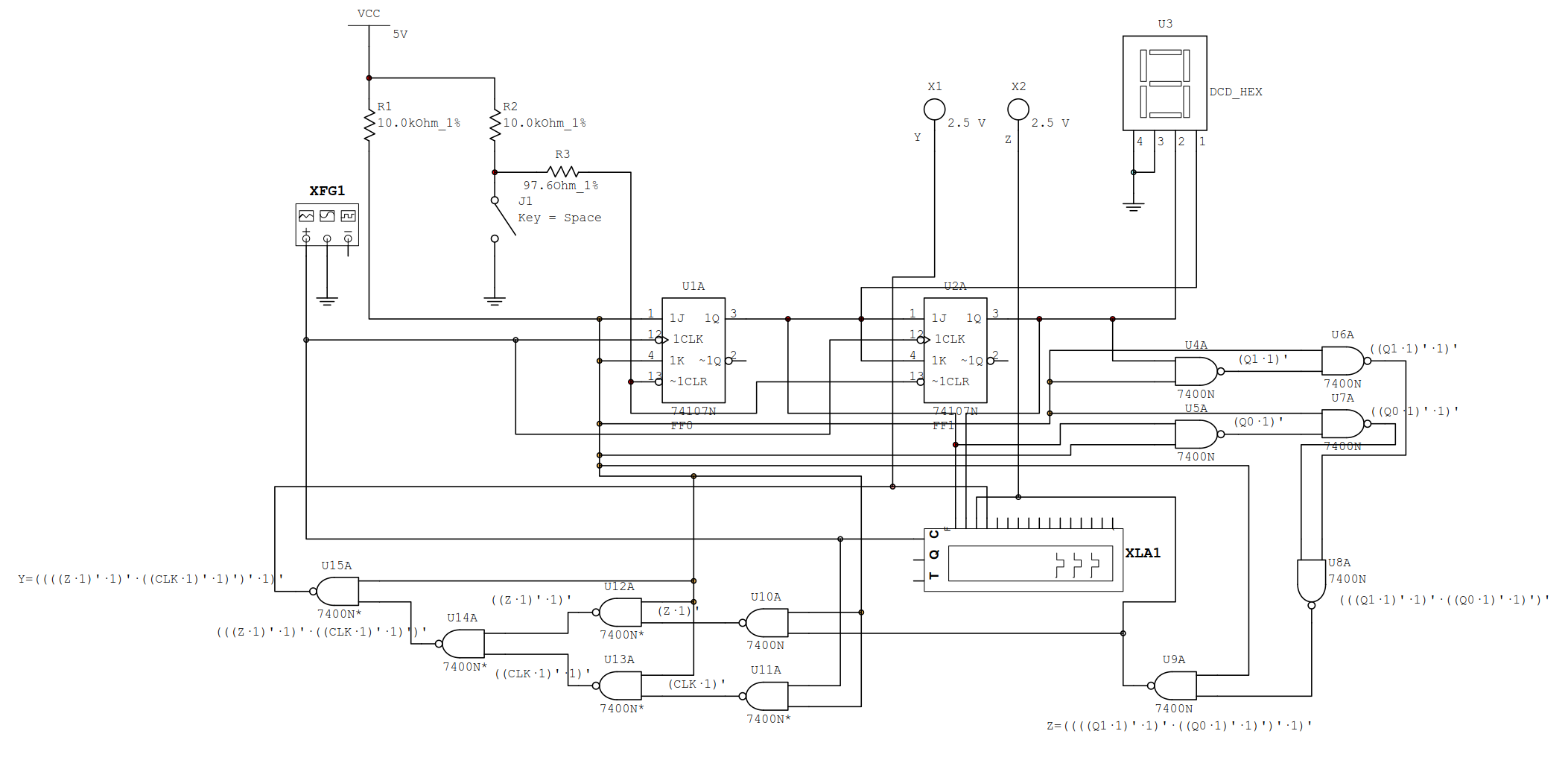

第二问原理图:

最后

以上就是诚心镜子最近收集整理的关于设计一个同步时序逻辑电路, 使得每输入4个周期的CLK脉冲, 便输出一个正脉冲, 其宽度为CLK脉冲的周期. 要求用与非门及下降沿触发的JK触发器实现. 如果要求输出脉宽为CLK脉宽, 该如何修改?的全部内容,更多相关设计一个同步时序逻辑电路,内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复