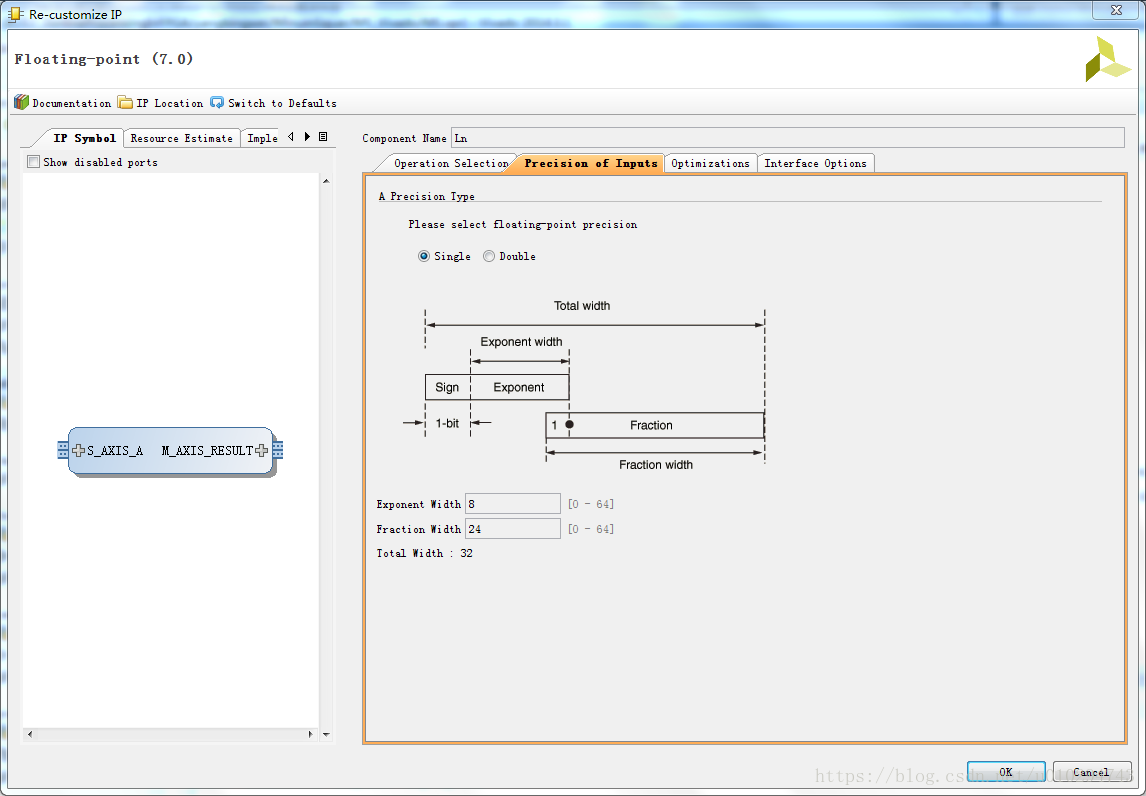

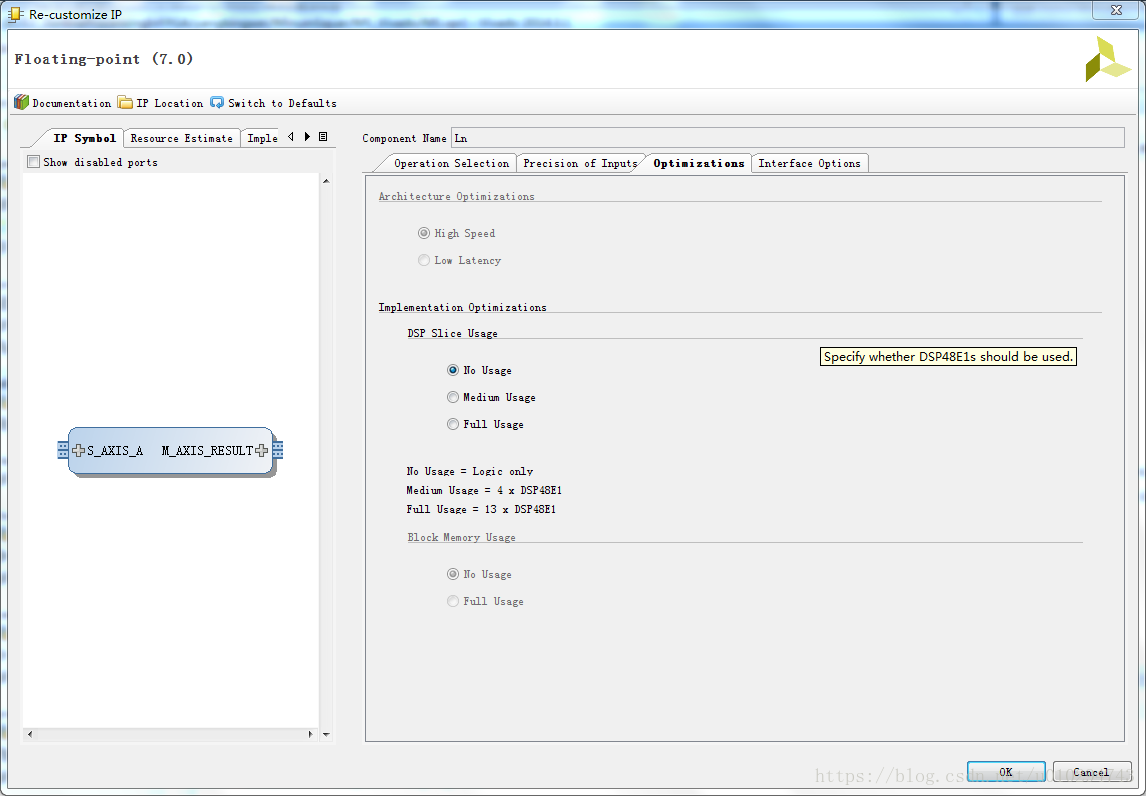

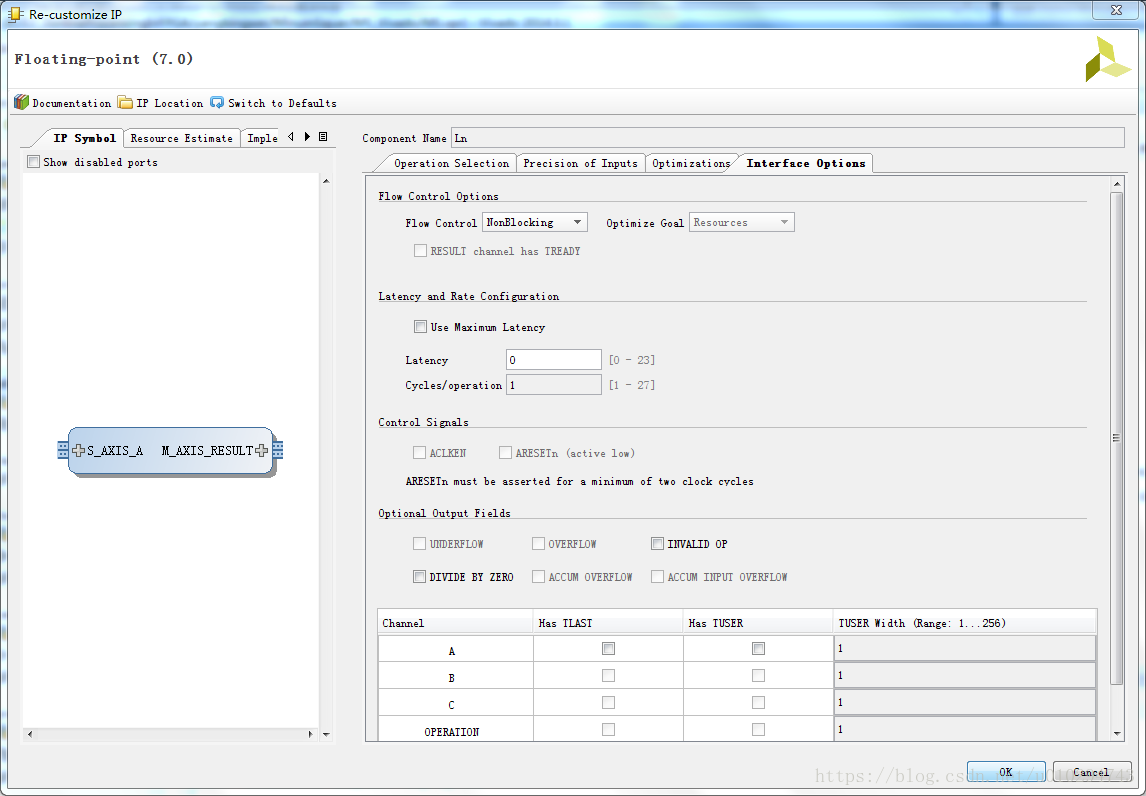

IP核设置

Ln(x)函数计算IP核设置为一个组合电路模块,不需要时钟

测试代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2018/06/19 15:45:55

// Design Name:

// Module Name: MS

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module MS(

input clk,

input rst,

input [31:0] din

);

//reg clk;

//Ln函数寄存器,浮点数输入

reg in_valid;

reg [31:0] Ln_indata;

wire out_valid;

wire [31:0] Ln_outdata;

Ln Ln (

.s_axis_a_tvalid(in_valid), // input wire s_axis_a_tvalid

.s_axis_a_tdata(Ln_indata), // input wire [31 : 0] s_axis_a_tdata

.m_axis_result_tvalid(out_valid), // output wire m_axis_result_tvalid

.m_axis_result_tdata(Ln_outdata) // output wire [31 : 0] m_axis_result_tdata

);

always@(clk)

if(!rst)

begin

Ln_indata<=32'b0;

in_valid<=1'b0;

end

else

begin

Ln_indata<=din;

in_valid<=1'b1;

end

endmodule

testbench

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2018/06/19 16:53:43

// Design Name:

// Module Name: MS_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module MS_tb(

);

reg clk;

reg rst;

reg[31:0] din;

MS ms(

.clk(clk),

.rst(rst),

.din(din)

);

initial

begin

clk =1'b0;

rst =1'b0;

din=32'b0;

#100

rst=1'b1;

din=32'h40000000;

end

always #10 clk=~clk;

endmodule

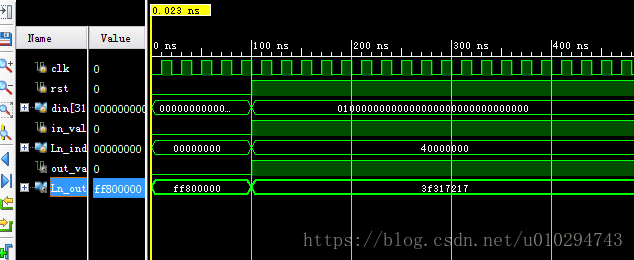

前Simulation结果

输入为Ln(2)

输出满足要求

备注:数据是单精度的浮点数

最后

以上就是称心毛巾最近收集整理的关于Vivado IP核使用 Ln(x)函数计算的全部内容,更多相关Vivado内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复