Vivado 除法IP的使用

- 1 Divider Generator IP的例化

- 2 代码

- 2.1 顶层文件

- 2.2 testbench文件

- 3 仿真结果

1 Divider Generator IP的例化

第一页配置:

**Algorithm Type:**选择不同的算法模式,其中Radix2为常用的模式,LutMult当时数较小的时候使用,High Radix是当数很大的时候使用。常用的是Radix2,此处也是选择的为Radix2.

Dividend Width:被除数的位数。

Divisor Width:除数的位数。

Remainder Type:选择余数的模式。有两种模式:Remainder:余数,以及Fractional分数模式。

Remainder模式的余数模式位数固定,由系统根据除数自动设定。而选择Fractional Width模式,则可以在Fractional Width那一栏选择自己想要的余数位数。常用模式为Remainder模式。

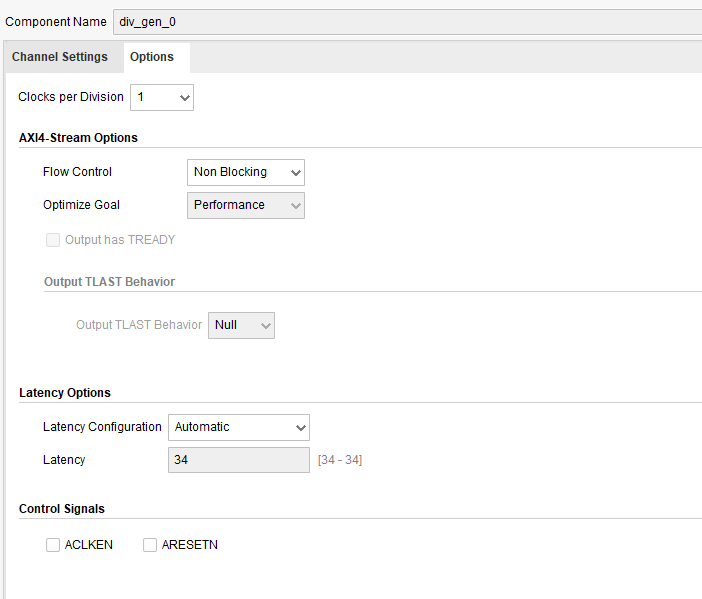

第二页配置保持默认即可,如下图所示。

2 代码

2.1 顶层文件

`timescale 1ns / 1ps

/*

Algorithm Type:选择不同的算法模式,其中Radix2为常用的模式,

LutMult当时数较小的时候使用,High Radix是当数很大的时候使用。

常用的是Radix2,此处也是选择的为Radix2.

Dividend Width:被除数的位数。

Divisor Width:除数的位数。

Remainder Type:选择余数的模式。

有两种模式:Remainder:余数,以及Fractional分数模式。

Remainder模式的余数模式位数固定,由系统根据除数自动设定。

而选择Fractional Width模式,则可以在Fractional Width那一栏选择自己想要的余数位数。

常用模式为Remainder模式。

*/

module top(

input clk ,//系统时钟

input rst_n //系统复位

);

//------根据给的信号频率Rev_Freq得到对应权值的地址

// 输入参数

wire Ctl_Men ;//信号频率有效信号

wire [31:0] Rev_Freq ; //信号频率 根据信号映射到addr,不是告诉的Cali_Freq_Band

assign Ctl_Men=1'b1 ;

assign Rev_Freq=32'd339 ; //

// 输出参数

wire [63 : 0] m_axis_dout_tdata;

wire div_tvalid; //除法结果有效

div_gen_0 Inst_div_gen_0 (

.aclk(clk), // input wire aclk

.s_axis_divisor_tvalid(1'b1), // input wire s_axis_divisor_tvalid

.s_axis_divisor_tdata(32'd100), // input wire [31 : 0] Divisor:除数 50KHz

.s_axis_dividend_tvalid(Ctl_Men), // input wire s_axis_dividend_tvalid

.s_axis_dividend_tdata(Rev_Freq), // input wire [31 : 0] Dividend:被除数。

.m_axis_dout_tvalid(div_tvalid), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata(m_axis_dout_tdata) // output wire [63 : 0] m_axis_dout_tdata

);

wire [31 : 0] data_intergral;//整数部分

wire [31 : 0] data_remainder;//余数部分

assign data_intergral=m_axis_dout_tdata[63:32];

assign data_remainder=m_axis_dout_tdata[31:0];

endmodule

2.2 testbench文件

`timescale 1ns / 1ps

module sim_top;

reg clk;

reg rst_n;

//例化源文件

top top_inst(

.clk (clk ),

.rst_n (rst_n )

);

initial

begin

//初始化输入

clk=0;

rst_n=0;

#20

rst_n=1;

end

// create clock;

always #5 clk=~clk;//每次间隔5ns,取一次反,也就是周期为10ns,所以频率为100MHz

endmodule

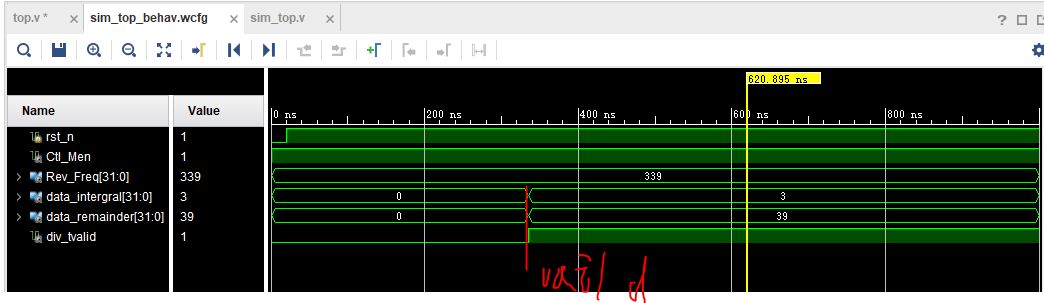

3 仿真结果

最后

以上就是无情墨镜最近收集整理的关于Vivado 除法IP的使用1 Divider Generator IP的例化2 代码3 仿真结果的全部内容,更多相关Vivado内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复