〇、前情提要

帮可爱的涛涛看题,顺便复习一下verilog。

参考:

- Verilog测试:TestBench结构

https://blog.csdn.net/qq_26652069/article/details/96422293 - 占空比的故事

http://www.360doc.com/content/18/0928/00/11935121_790268293.shtml - Verilog仿真时钟产生方法学习

https://blog.csdn.net/flomingo1/article/details/102676669

一、题目分析

原题

设计一个测试文件,产生一个周期为2微秒,占空比为3:1的时钟信号

测试文件

参考:

Verilog测试:TestBench结构

https://blog.csdn.net/qq_26652069/article/details/96422293

完整的TESTBENCH文件结构

module Test_bench()//一般简单的测试文件无输入输出

信号或变量声明定义

逻辑设计中输入信号在这里对应reg型变量

逻辑设计中的输出信号在这里对应wire型

使用initial或always语句块产生激励

例化猜测是模块UT

监控和比较输出响应

endmodule

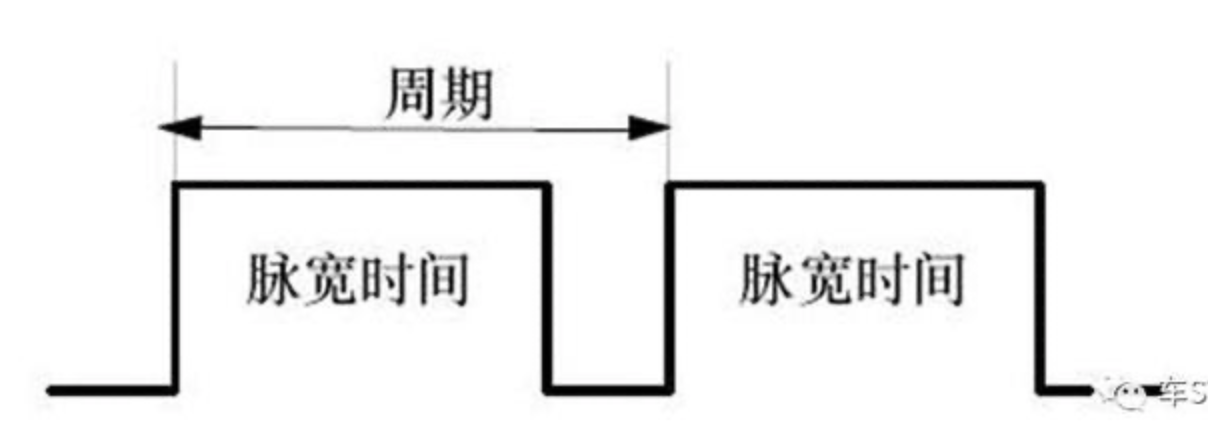

周期为2微秒

T=2微秒=2000ns

占空比为3:1

参考:

占空比的故事

http://www.360doc.com/content/18/0928/00/11935121_790268293.shtml

上面这篇文章解释得很不错,小白更容易理解。

占空比就是在一个工作周期内。通电的时间占这个周期的比值,这个周期指的是通电时间和断电时间的和。

于是我就理解成 高1低3的比例

t=T/4=500ns

二、开写

参考:

Verilog仿真时钟产生方法学习

https://blog.csdn.net/flomingo1/article/details/102676669

自定义占空比的时钟信号:

parameter High_time = 5,Low_time = 20;

// 占空比为High_time/(High_time+Low_time)

reg clk;

always begin

clk = 1;

#High_time;

clk = 0;

#Low_time;

end

改写后

`timescale 1ns/1ps

module Test_bench;

parameter High_time = 500,Low_time = 1500;

// 占空比为High_time/(High_time+Low_time)

reg clk;

always begin

clk = 1;

#High_time;

clk = 0;

#Low_time;

end

endmodule

想当年学数电的时候很喜欢教我们的孙老师,考了高分学得自以为很好(但其实是因为那时候还没搞工程认证,所以很简单),现在辅导学妹看得我一愣一愣的,知道但又不知道,不知道以后还会不会用到。

最后

以上就是激昂蜗牛最近收集整理的关于【verilog】设计一个测试文件,产生一个周期为2微秒,占空比为3:1的时钟信号的全部内容,更多相关【verilog】设计一个测试文件,产生一个周期为2微秒,占空比为3:1内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复