由于连接在主线上的每个设备的工作频率不同,因此需要把CPU的频率进行分频。偶数分频较为简单,这里不再赘述。下面是奇数分频占空比为50%的Verilog HDL代码。

// ---------odd_divider.v---------------

// 默认实现7分频的时钟信号

// 计数器要大于7的

// 分别在时钟信号的上升沿和下降沿对时钟信号分频

module odd_divide(clk_in, clk_out, rstn);

input clk_in;

input rstn;

output clk_out;

reg clk_out1, clk_out2;

reg [31:0] counter1, counter2;

parameter m = 7;

assign clk_out = clk_out1 & clk_out2;

always @(posedge clk_in or negedge rstn)

if (!rstn)

begin

counter1 <= 32'b0;

clk_out1 <= 0;

end

else if(counter1 == m / 2 - 1)

begin

counter1 <= counter1 + 1;

clk_out1 <= 1;

end

else if(counter1 == m - 1)

begin

counter1 <= 0;

clk_out1 <= 0;

end

else

begin

counter1 <= counter1 + 1;

end

always @(negedge clk_in or negedge rstn)

if (!rstn)

begin

counter2 <= 0;

clk_out2 <= 0;

end

else if (counter2 == m / 2 - 1)

begin

counter2 <= counter2 + 1;

clk_out2 <= 1;

end

else if(counter2 == m - 1)

begin

counter2 <= 0;

clk_out2 <= 0;

end

else

begin

counter2 <= counter2 + 1;

end

endmodule

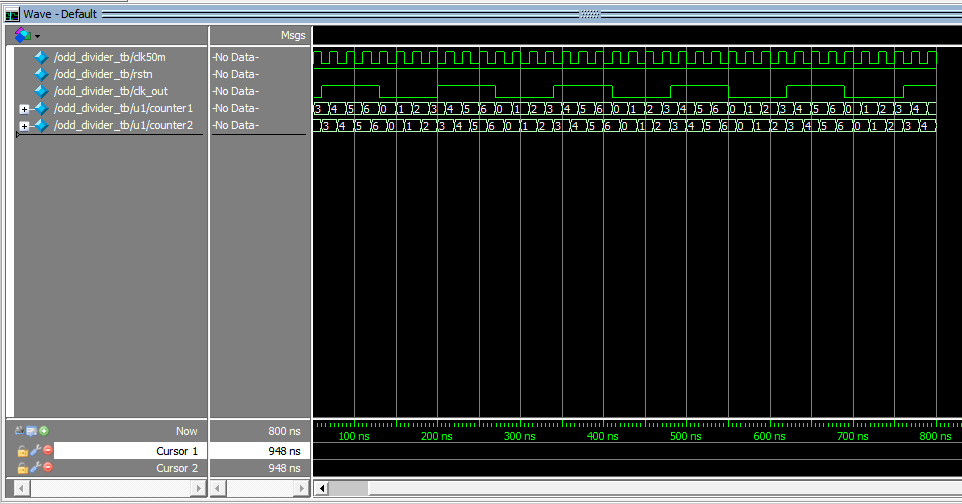

上述模块默认完成的是7分频,在modelsim中的波形:

测试的TestBench代码:

//-------odd_divider_tb.v-------------

`timescale 1ns/1ns

`include "./odd_divider.v"

module odd_divider_tb;

reg clk50m;

reg rstn;

wire clk_out;

initial

begin

clk50m = 0;

rstn = 0;

#10 rstn = 1;

end

always #10 clk50m = ~clk50m;

odd_divider u1(.clk_in(clk50m), .rstn(rstn), .clk_out(clk_out));

endmodule

原理:分别使用时钟信号的上升沿和下降沿,根据分频的要求计算时钟信号的翻转计数,然后将两个时钟信号求与运算。另外注意复位信号应为异步复位。

counter1 = m / 2 -1;

counter2 = m - 1;

assign clk_out = clk_out1 & clk_out2;

最后

以上就是无私小蚂蚁最近收集整理的关于Verilog HDL实现任意50%占空比的奇数分频的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复