状态机与时钟分频

题目描述

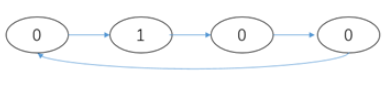

使用状态机实现时钟分频,要求对时钟进行四分频,占空比为0.25

信号示意图

题目解读

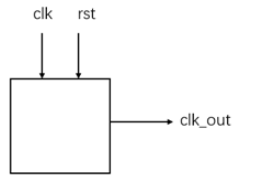

首先考虑输入输出,作为分频电路,有一个时钟输入端,clk,输出端div3,再加一个复位端(这里不加也可)所以输入 clk,rst输出 clk_out再考虑状态转换的问题。4分频占空比0.25,可以为0100或1000都行。

在时钟的作用下,应该不停的在这四种状态下转换,并且输出仅仅依赖于当前的状态,所有的整数分频器都可以按照次方法来实现。

`timescale 1ns/1ns

module huawei7(

input wire clk ,

input wire rst ,

output reg clk_out

);

parameter[1:0] S0=2'd0,

S1=2'd1,

S2=2'd2,

S3=2'd3;

reg[1:0] state,next_state;

always @ (posedge clk or negedge rst)

begin

if(!rst) state<=S0;

else state<= next_state;

end

always @ (state)

begin

最后

以上就是轻松店员最近收集整理的关于状态机与时钟分频的全部内容,更多相关状态机与时钟分频内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复