实现信号分频的Verilog方法有很多种,如果从本质上理解了分频这一思路则遇到任何的分频情况都能迎刃而解。因此首先来谈谈什么是分频。

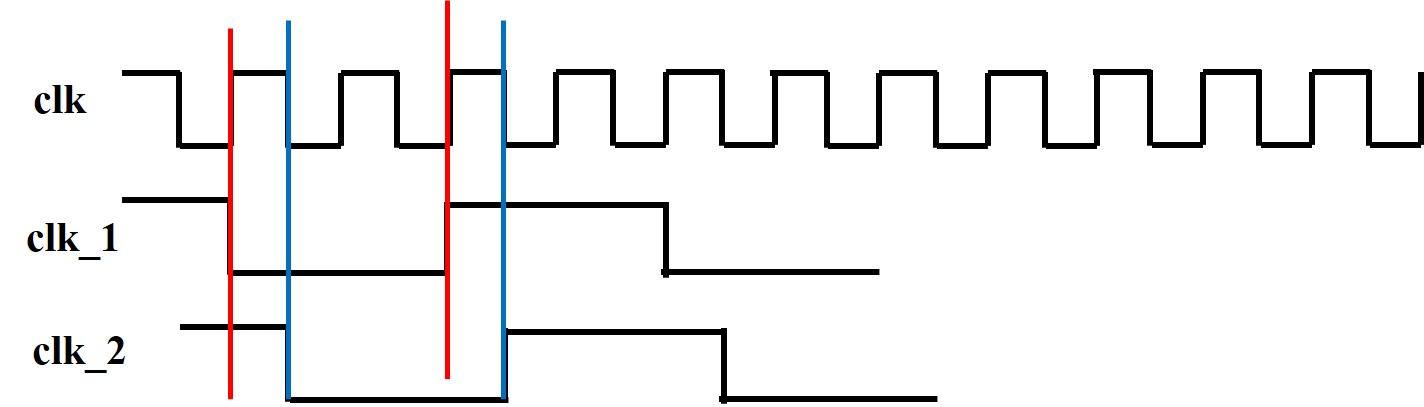

对于偶数分屏,如四分频,我们可以发现其分频后的时钟的跳变,无论是上升沿还是下降沿都是统一在原始时钟信号的上升沿如clk1, 或者是下降沿如clk2。如下图所示;

因此对于偶数的分频,我们可以用一个计数器来实现;

module div_2(clk,rst,clk2);

input clk,rst;

output clk2;

reg [2:0] cnt;

always@(posedge clk or negedge rst)

if(!rst)

begin

cnt<=0;

clk2<=0;

end

else if(cnt == 3'b011)

begin

cnt <= 0

clk2 = clk2;

end

else if(cnt == 0)

begin

cnt <= cnt +1;

clk2 = ~clk2

end

else

begin

cnt <= cnt + 1;

clk2 = clk;

end

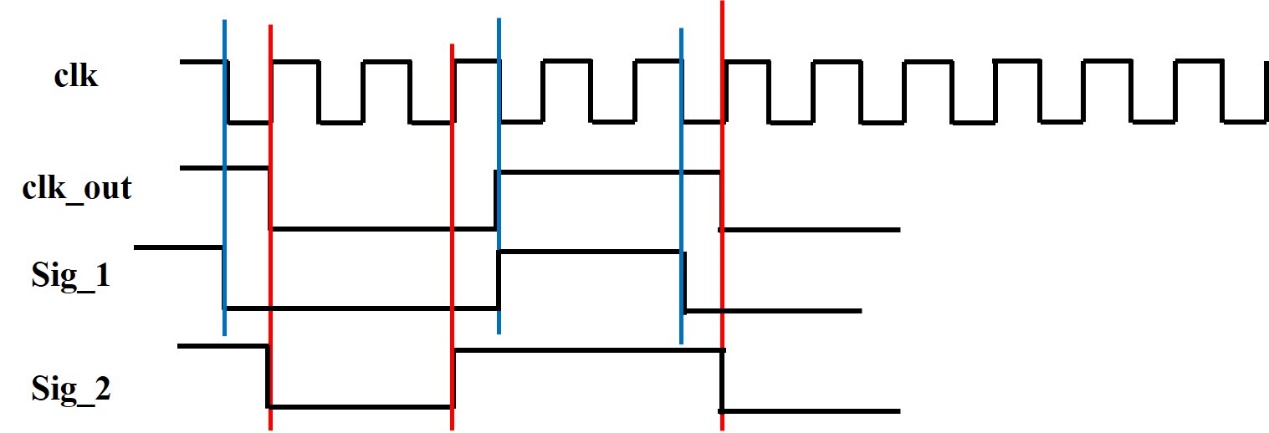

endmodule而对于奇数分频,显然一个输出时钟的周期包含原始周期个数为奇数个,则该输出的时钟的跳变则必定会出现在原始时钟的不同跳变沿上,如图2所示,这是一个5分频的信号图。可以看到原始信号clk的上升沿和下降沿都可能存在着clk_out的跳变。而计数器实现的倍频信号则只能实现但跳变沿的输出时钟,因此,该奇数分频的信号需要两个不同跳变沿的输出信号(Sig_1和Sig_2)进行合成。所以通过分析clk_out的波形,即当clk_out在clk上升沿时跳变时(红色线),则让Sig_2起作用;反之,则让Sig_1起作用(蓝线)。因此我们可以得到两个不是50%占空比的时钟信号Sig_1和Sig_2.因此我们可以开始用计数器实现这一功能,但相比偶数计数器,这两个计数器需要在0和中间某个数字处进行翻转,当设计5分频时,该数字为3。推理可得当需要设计N分频时钟时,需要在0和(N+1)/2处设置翻转。

示例如下,当设计13分频的时钟信号时需要在0和7处进行翻转:

module tclk_gena(clk, rst_n,tclk);

input clk;

input rst_n;

reg [4:0] cnt1;

reg [4:0] cnt2;

output wire tclk;

reg clk1;

reg clk2;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

cnt1 <= 0;

clk1 = 1'b1;

end

else if(cnt1 == 0)

begin

cnt1 <= cnt1 + 1'b1;

clk1 = ~clk1;

end

else if(cnt1 == 4'b00111)

begin

cnt1 <= cnt1 + 1'b1;

clk1 = ~clk1;

end

else if(cnt1 == 4'b01100)

begin

cnt1 <= 4'b00000;

clk1 <= clk1;

end

else

begin

cnt1 <= clk1;

cnt1 <= cnt1 + 4'b1;

end

always@(negedge clk or negedge rst_n)

if(!rst_n)

begin

cnt2 <= 0;

clk2 = 1'b1;

end

else if(cnt2 == 0)

begin

cnt2 <= cnt2 + 1'b1;

clk2 = ~clk2;

end

else if(cnt2 == 4'b00111)

begin

cnt2 <= cnt2 + 1'b1;

clk2 = ~clk2;

end

else if(cnt2 == 4'b01100)

begin

cnt2 <= 4'b00000;

clk2 <= clk2;

end

else

begin

cnt2 <= clk2;

cnt2 <= cnt2 + 4'b1;

end

assign tclk = ~(clk1 | clk2);

endmodule 测试代码如下

`timescale 1ns/1ns

`define clk_period 20

module tclk_gena_tb;

reg clk;

reg rst_n;

wire tclk;

tclk_gena tclk_gena(

.clk(clk),

.rst_n(rst_n),

.tclk(tclk)

);

initial

clk = 1'b1;

always #(`clk_period/2) clk = ~clk;

initial

begin

rst_n = 0;

#(`clk_period*20);

rst_n = 1;

#(`clk_period*200);

$stop;

end

endmodule

最后

以上就是义气黄豆最近收集整理的关于奇数分频和偶数分频的Verilog实现——对分频本质上的理解的全部内容,更多相关奇数分频和偶数分频内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复