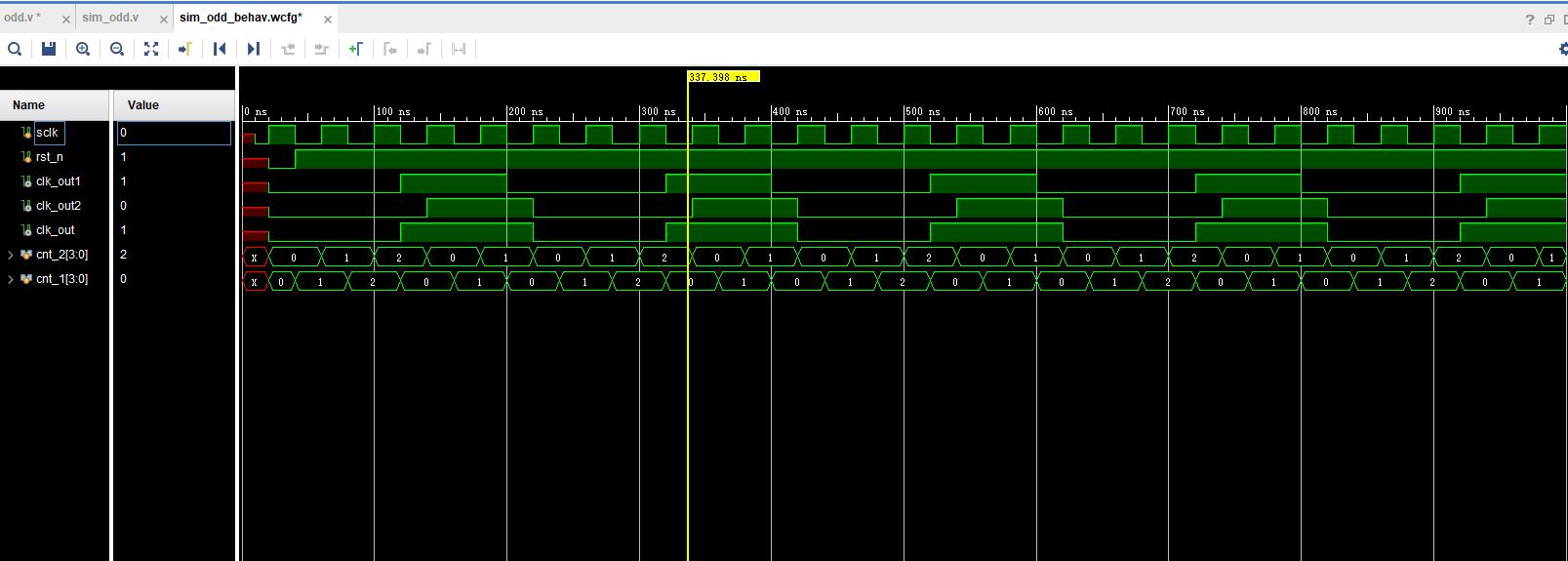

奇数分频:注意的在于,上升沿触发和下降沿触发,然后分别输出两个时钟,相或就可以实现了,参考https://blog.csdn.net/qq_36147669/article/details/78888409

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2019/05/28 14:25:57

// Design Name:

// Module Name: odd

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module odd(

input sclk,

input rst_n,

output reg clk_out1,

output reg clk_out2,

output clk_out

);

parameter COUNT = 5;

reg [3:0] cnt_1;

reg [3:0] cnt_2;

always @ (negedge sclk or negedge rst_n)

if(!rst_n) begin

clk_out1 <= 1'b0;

cnt_1 <= 1'b0;

end

else begin

if(clk_out1 == 1'b0) begin

if(cnt_1 == COUNT/2 ) begin

clk_out1 <= ~clk_out1;

cnt_1 <= 1'b0;

end

else

cnt_1 <= cnt_1 + 1;

end

else if(clk_out1 == 1'b1) begin

if(cnt_1 == COUNT/2 - 1) begin

clk_out1 <= ~clk_out1;

cnt_1 <= 1'b0;

end

else

cnt_1 <= cnt_1 + 1;

end

end

always @ (posedge sclk or negedge rst_n)

if(!rst_n) begin

clk_out2 <= 1'b0;

cnt_2 <= 1'b0;

end

else begin

if(clk_out2 == 1'b0) begin

if(cnt_2 == COUNT/2) begin

clk_out2 <= ~clk_out2;

cnt_2 <= 1'b0;

end

else

cnt_2 <= cnt_2 + 1;

end

else if(clk_out2 == 1'b1) begin

if(cnt_2 == COUNT/2 - 1) begin

clk_out2 <= ~clk_out2;

cnt_2 <= 1'b0;

end

else

cnt_2 <= cnt_2 + 1;

end

end

assign clk_out = clk_out1 | clk_out2;

endmodule

实现的是5分频

最后

以上就是等待钢笔最近收集整理的关于Verilog实现奇数分频的全部内容,更多相关Verilog实现奇数分频内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复