本文是小白用于自我总结,如有漏误,请在评论区批评指正。

完成功能仿真后,综合工具根据代码生成逻辑网表、门级网表,后续再进行版图规划、布局布线等。而门级网表进行仿真,需要按考虑fab厂家的产品工艺参数,如mos管的寄生电容等因素、以及版图规划、布局布线情况,由此导致的门延迟、时钟偏移time-skew,等均需满足时钟建立时间、保持时间等约束条件。即静态时序分析sta工作的目标。

相应的,在sta以前的功能设计与验证过程中,vcs工具有下面的特点:

1、敏感事件列表中,clk的有效跳变 与

reset的有效跳变

2、敏感事件列表中,clk的有效跳变 与

always块内 ,非阻塞赋值RHS的表达式结果 与

always块内,条件判定表达式,e.g. " if(!reset) "中的 reset

上述信号同时跳变,如何判定?

reset清零 >> clk跳变 >> 其他信号(包括always块内reset的释放)

即工具认为 reset先到,clk再到,第一层判定信号先到, 其他信号最后到。

新的问题:

1、时钟周期最快应设置多少?

p.s.自问自答,按照spec文档要求。

2、确定时钟周期之后,两个触发器之间,可容纳多大规模的组合逻辑电路?

p.s.自问自答,两个寄存器间的组合电路,其关键路径的门延迟不能过长,要满足时序要求。这就限制了组合逻辑的规模。具体要求应该看spec文档。

3、rtl设计与验证时 ,如何处理时序约束问题,允许同时跳变,交由版图设计、布局布线人员解快?

or控制组合逻辑电路规模,并预留时间确保触发器捕捉?预留时间如何确定?

p.s.自问自答,由spec文档决定。spec文档中对关键路径时延做出的限定,已经考虑到了满足时序约束及预留时长的问题。具体在设计时,如果组合逻辑规模过大,可采用增加寄存器的流水线设计方式,也可减少复杂组合逻辑产生毛刺的可能,但会占用更大的面积。

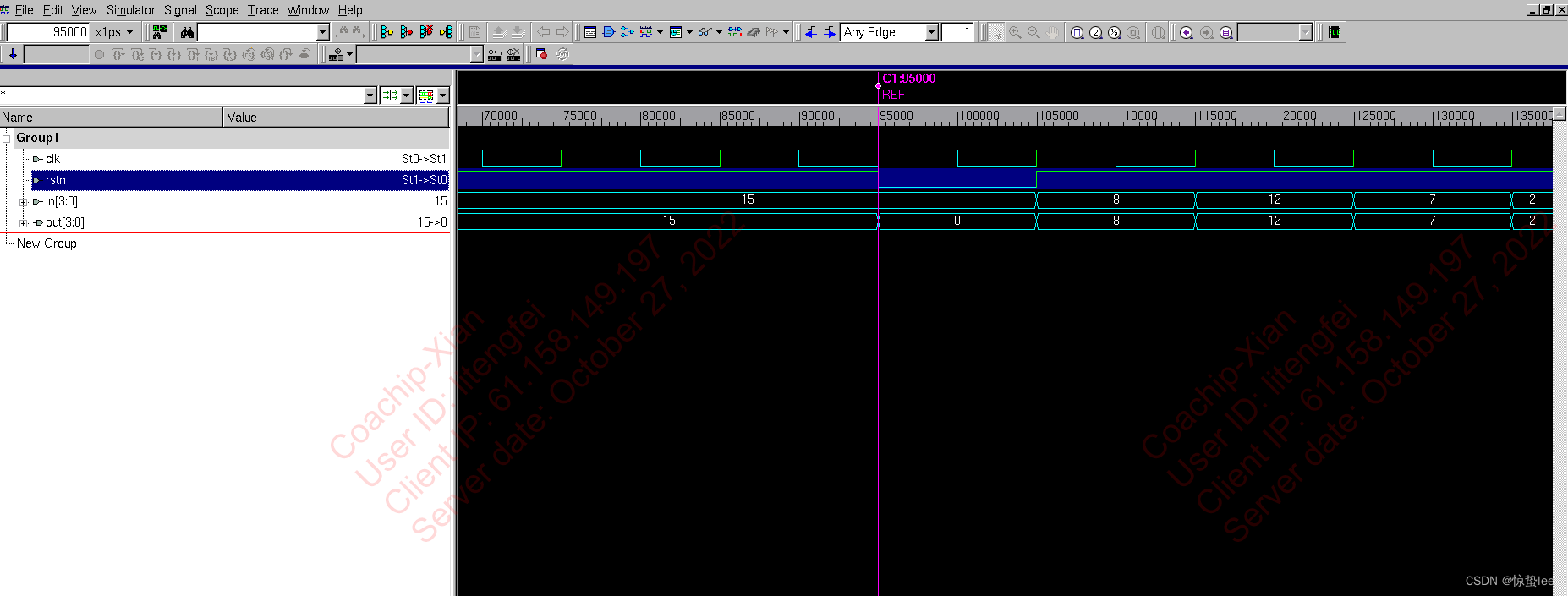

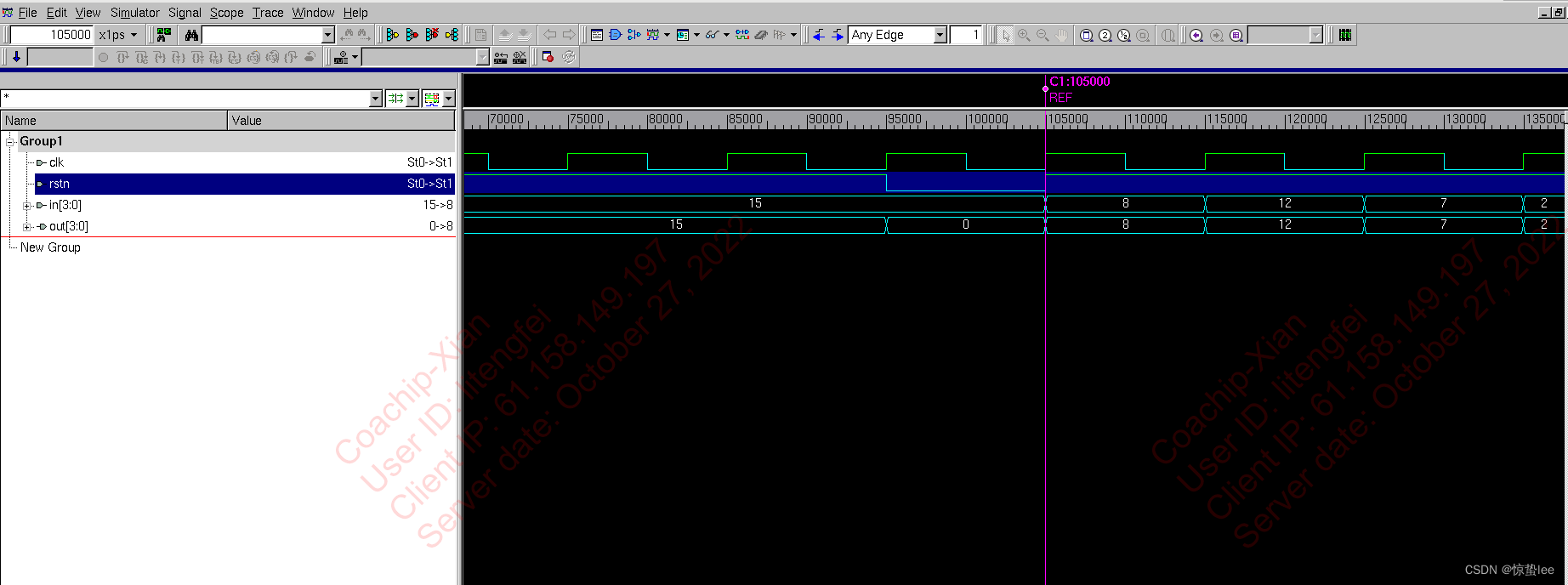

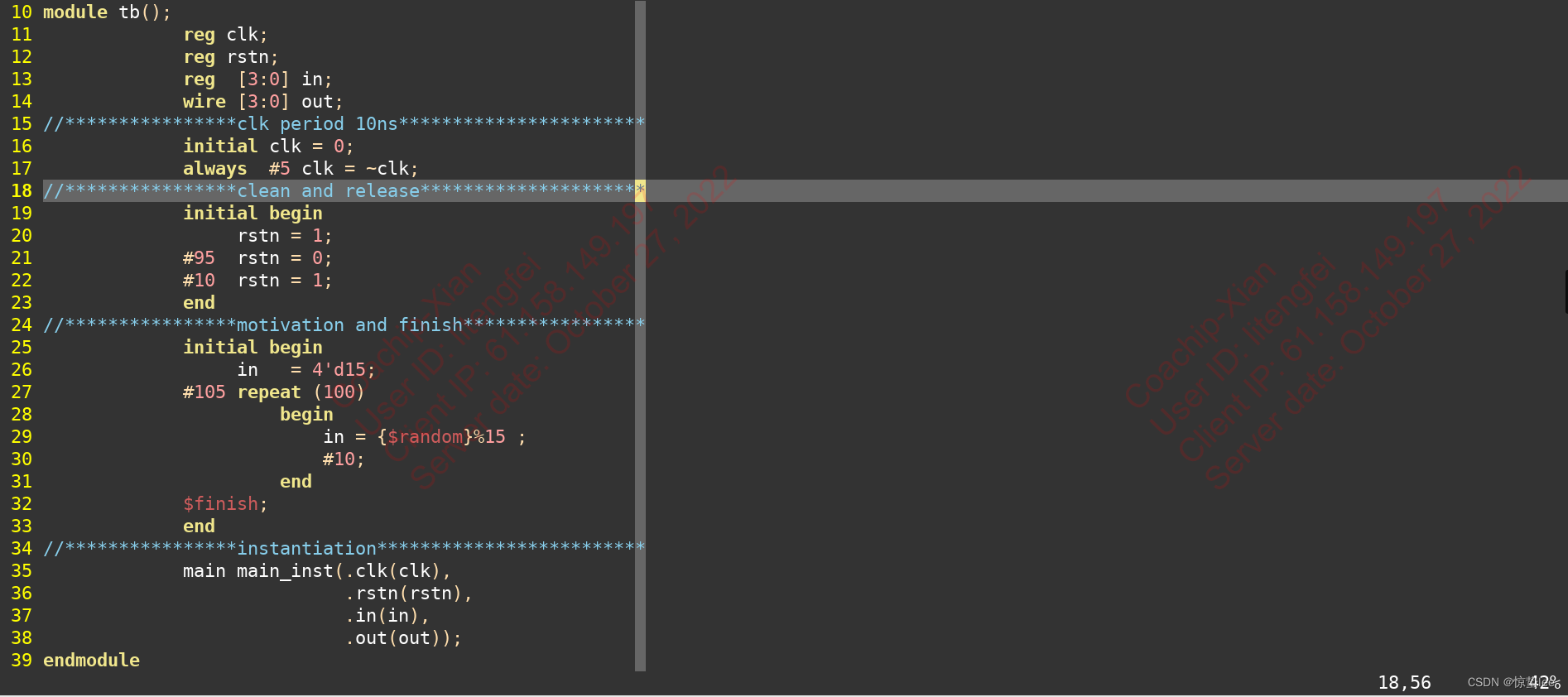

如图

最后

以上就是淡淡毛巾最近收集整理的关于vcs进行功能仿真时,时钟信号与其它信号同时跳变如何处理的全部内容,更多相关vcs进行功能仿真时内容请搜索靠谱客的其他文章。

发表评论 取消回复