写了一段 Verilog代码后进行综合,在debug的过程中,却找不到需要debug的信号了,查看网表发现没有?

这种情况是因为我们的某些中间信号被优化掉了。

被优化掉的原因有可能是你这个信号确实对后面的输出没用,我写的这个项目由于还在中间过程,功能还没有完善,所以不想把大量的中间信号作为输出,所以被优化掉了,以至于在debug过程中找不到这些信号。

如何解决这个问题呢?

方式1

在变量定义的时候添加语句:

(* keep = “true” *)

方式2

信号前面将keep hierarchy选择yes ,或者选择soft(在综合时保持层次),这样有利于你从模块中找到你想抓取的信号和信号名不被更改。

(* keep_hierarchy = “yes” *)module fre( a, b, c, d);

or

(* keep_hierarchy = “yes” *)fre fre_inst( a, b, c, d);

方式3

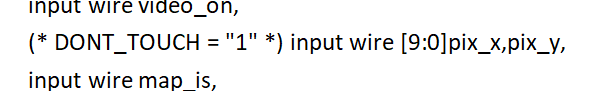

信号前面使用(* DONT_TOUCH= “{TRUE|FALSE}” *),可以防止信号在综合,以及布局布线的时候被优化掉。

(* dont_touch = “true” *) wire a;

例如:

最后

以上就是懵懂毛巾最近收集整理的关于VIvado--verilog--避免工程中信号被优化掉的全部内容,更多相关VIvado--verilog--避免工程中信号被优化掉内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复