回忆以前所学, 正好看到一本讲low power 不错的书, An Asic Low Power Primer (2013), 这本书里讲到Power Modeling (library 是怎样对power建模的), 对ASIC design 怎样做power 分析, Low Power Design技巧, 本文主要关注其中第六章, Architectural Techniques for Low Power. 具体分析其中的Dynamic Voltage and Frequency Scaling

学习中也参考了Low Power Methodology Manual for System-On-Chip Design(2007), 这本书虽然旧了点(还在讨论90nm, 65nm), 但是更细节, 更注重实现.

Variable Frequency

频率可调节, 意思是design时就不要设计过高的clock, 对Power有限制的design来说,可以考虑牺牲一些speed来换取power 降低. 对于idle mode, 主动降低时钟频率可以省很多power. 进入idle mode 时可以通过clock mux选择低频clock,来省power.

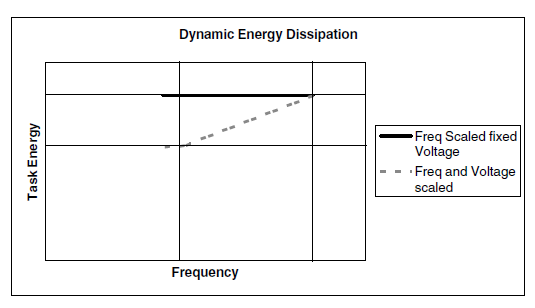

因为频率变低了, 所以对task来说处理变慢了, 所以从task需要消耗的energy来看, 降低频率并没有改变energy(忽略leakage)

Dynamic Voltage Scaling

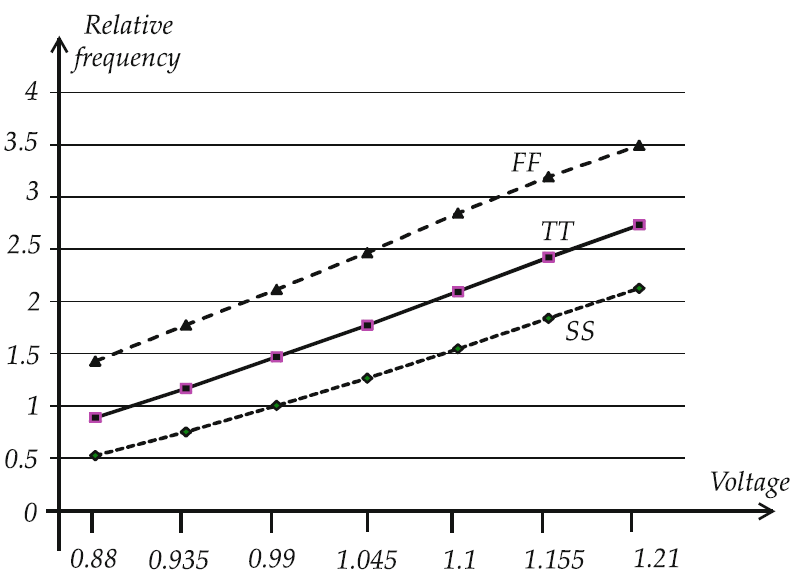

动态调节电压. 因为Process Variation, 同一批Tape Out 的芯片会有fast part, slow part. (也可分成ss, tt, ff). sign off 时需要保证最慢的part的那些芯片也能在最低的Power Supply上达到target frequency. 比如signoff 在ss0p65v0C. 通常如果温度上升,或电压上升, 这些slow part会有更好的performance.

dynamic voltage scaling 使芯片能根据要求动态的调整电压.

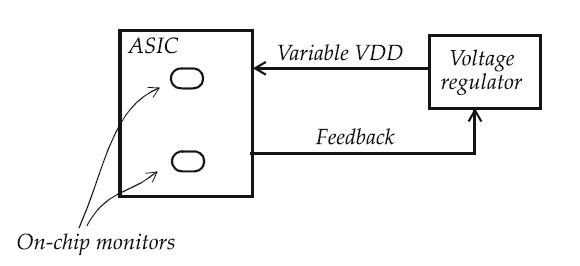

这就需要用到On-Chip monitor 来提供feedback, 提供给on-chip 或off-chip的VR(voltage regulators), VR 根据feedback来动态调节电压. 这些monitor一般放在芯片的各个位置测量speed. 比如ring oscillator, 就可以用来测量不同电压条件下对应的frequency. 每个芯片, 甚至一颗芯片的不同部位对同样的电压都有不同的反应. 因此使用monitor来反馈frequency 就可以动态合理调节power supply, 让芯片工作在target speed下, 避免出现电压太高, 浪费power的情况.

温度是如何影响各个corner的可以参考这篇论文.https://pdfs.semanticscholar.org/6325/986ed304866cc3f0568a865924ab62451315.pdf

另外这个技术也叫做 adaptive voltage scaling (AVS).

注: 其实在 Low Power Methodology Manual For System-On-Chip Design 这本书里, 只有AVS指的是有performance monitor 和feedback 设计的, 其余的DFS 和DVFS都是open loop. 但是个人猜测2007以后, 大部分做DVS, DVFS的芯片都引入了feedback, 所以AVS也没有特别之处了, 就不区分的那么明显了.

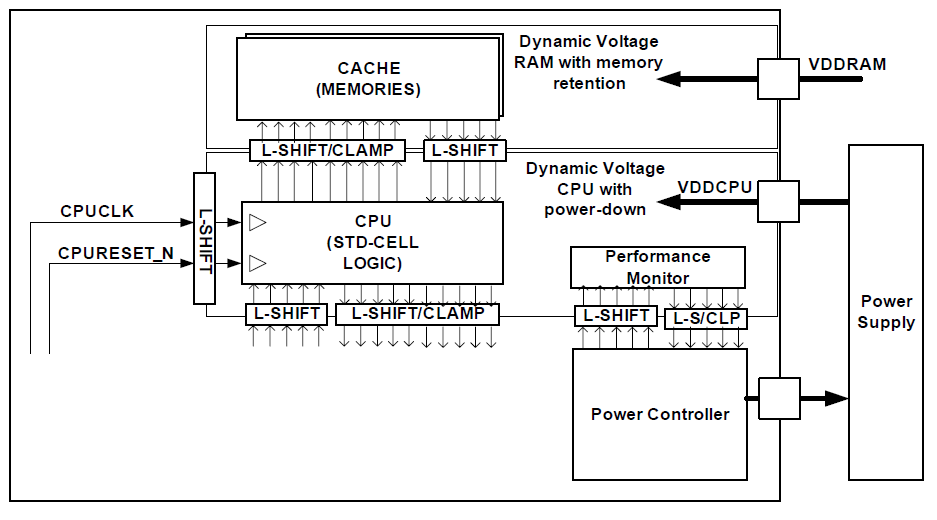

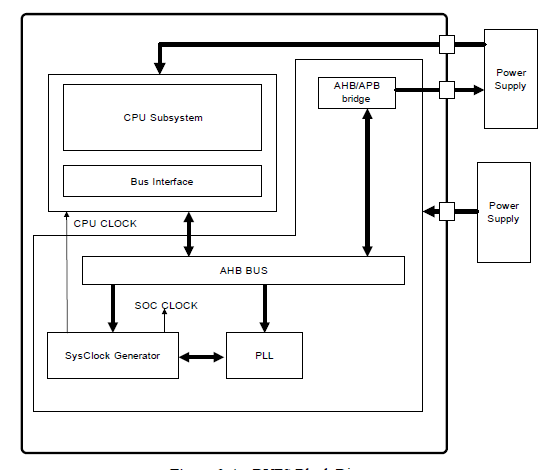

看一眼CPU AVS的设计:

这个performance monitory应该和IP尽可能的放在一起, 这样监控的结果更准, 对一个很复杂的系统, 会有很多performance monitor blocks, 最差的那个sensor就是critical feedback element. 他们与power controller相连, 这个power controller会设定新的电压反馈给Power Supply.

还有的地方提到了SVS(Static Voltage Scaling), MVS(Multi-level Voltage Scaling), 这两种属于静态电压scaling. SVS 是指各个block或subsystem采用不同的supply电压. MVS 是指一个block或subsystem有多个voltage level. 对应不同的mode(比如sleep mode可以切换到低压). 这部分内容不做详细讨论.

Dynamic Voltage and Frequency Scaling

这个技术也是通过on-chip monitor 或look up table来动态调节voltage 和 frequency. 和DVS 不同的是, DVS的目的是针对不同part的芯片, 调节电压, 让其满足能跑target speed 的条件, 别多给voltage浪费power. 而DVFS是为了满足performance要求, 同时调整voltage 和frequency. 比如perf要求不高, 可以降低频率运行, 同时需要的电压就没那么大. 或者突发任务perf要求变高了, 需要提高频率, 同时也需要更高电压来满足.

因为Dynamic Power = C * f * Vdd* Vdd, 所以减少f 和Vdd 对power影响很大. 虽然DVFS在design, verification, implementation上实现有难度, 但是好处在于几乎不影响area和timing.

看个例子

这里有个CPU 的subsystem, 由PLL供应clock. 为了实现DVFS, 首先软件决定了一个最低CPU clock 频率, 足够应付当前workload. 然后VR通过look up table 或者monitor提供的feedback 调节电压, 使得提供一个能支持当前clock的最低电压.

当workload变化之后, 需要更快的target clock, 这时就有以下情况发生:

- CPU 要求power supply提供更高电压.

- 伴随电压上升,CPU依然工作在current clock

- 电压达到要求, CPU要求target clock

- 如果clock frequency的改变只需要改变divider value, 那SysClock Generator 会做出调整, CPU operation不会中断.

- 如果clock frequency的改变需要改变PLL frequency, 那CPU需要向PLL program 来要求新的频率. 这样PLL和SysClock Generator 会暂停所有clock 直到PLL新频率确定. (2007年的书, 不确定现在有什么更新)

如果target clock frequency 比当前frequency低, 那么会按以下顺序:

6. CPU要求新clock frequency

7. 如果clock frequency的改变只需要改变divider value, 那SysClock Generator 会做出调整, CPU operation不会中断.

8. 如果clock frequency的改变需要改变PLL frequency, 那CPU需要向PLL program 来要求新的频率. 这样PLL和SysClock Generator 会暂停所有clock 直到PLL新频率确定.

9. CPU 要求 新的voltage

10.CPU先以新的低频率工作, 电压慢慢降到要求电压.

综上所述, 由于电压不足会导致function fail, 所以但凡要改变频率, 都要保证电压满足要求, 比如先把电压抬起来, 在抬频率, 或者先降频率, 再降电压.

这其中的难点在于:

- 怎样确定应该以多少voltage和多少clock frequency来工作

- Modeling Timing

- 频率变化和电压变化需要时间, 怎么安排

Timing/Voltage 值的确定

- 确定各个workload 需要的合理频率 (可以让软件开发人员在FPGA上跑sample application来确定有几种performance状态)

- 最好是PLL period的倍数, 这样只需要改变clock divider, 不需要改变PLL frequency

- target frequency需要多少voltage

温度反转效应

温度反转是一种现象, 就是delay和voltage的关系随着温度变化会发生改变. 通常delay随着温度升高会升高, 但是在某个电压以下(2Vt), delay随着温度升高会降低. 这种现象的发生与Vt有关, 而design里用到各种Vt(high Vt, low Vt) cell, 这样会造成一个新的现象: 如果电压被减低的太多, 那么原来不是critical path的突然变成critical path. 这时 voltage/timing 不是单调函数关系, 因此voltage scalling 不好实现.

Libraries

想要知道某个clock frequency 需要多少voltage, 需要在各种condition下做timing analysis. 根据本人经验, 对于7nm 芯片可能会在ss0p65v0C, tt0p9v100C, ff1p05v100C 这几个点做signoff STA check. 这样就可以连线成为一条STA curve (F vs Vdevice), 然后转化为F vs Vpin 用来分析芯片在不同频率下的功耗(DVFS工作时).

切换时机和算法

切换performance levels需要时间, 而且我们希望切换时芯片保持工作. 切换电压是非常慢的, 通常需要花10~1000us来稳定, 考虑安全性必须要处理好Overshoot 和Undershoot 问题, 这又增加了切换时间. 一般我们会让voltage regulator装有多个source, 所以切换时间对于每个部分都不一样.

切换频率通常很快, 快几个数量级. 所以参考前文所说, 但凡要改变频率, 都要保证电压满足要求, 比如先把电压抬起来, 在抬频率, 或者先降频率, 再降电压.

能不能在DVFS生效时把时钟停掉, 等电压或频率变动好? 这样会导致严重的interrupt, 让相应时间变长, 或者打断了device driver timing 要求.

所以需要有一个最低操作频率一直工作, 切换F和V时就让这个最慢时钟顶上去用, 直到新的F和V settle

Reducing VDD

Power 与 Vdd的平方成正比, 所以能减少Vdd对降低Power来说很重要. 所以要探索各个block所需电压, 是不是有的block不需要跑的很快, 因此可以用一个低的voltage. 如果能完全shut down, 这也能省很多power.

剩下的内容包括:

- Architectural Clock Gating

- Power Gating

- Multi-voltage

- Optimizing Memory Power

- Operand Isolation

- Operating Modes of Design

- RTL Techniques

在下一篇文章里会被介绍到.

[学习笔记]从架构层面看低功耗(Low Power)Design (二)

最后

以上就是含蓄酒窝最近收集整理的关于[学习笔记]从架构层面看低功耗(Low Power)Design (一)的全部内容,更多相关[学习笔记]从架构层面看低功耗(Low内容请搜索靠谱客的其他文章。

![[学习笔记]从架构层面看低功耗(Low Power)Design (一)](https://www.shuijiaxian.com/files_image/reation/bcimg25.png)

发表评论 取消回复