以下文章来源于微信公众号“IC解惑君”,作者木飞

对于IC中的亚稳态部分,先给出建议和方法:

在目前的IC/SOC设计中,不同时钟域的交互是不可避免的,参考下面的策略,可以减少亚稳态发生的概率。

(1)使用同步器进行不同的时钟域的信号同步。

(2)使用特殊定制的触发器,降低亚稳态窗口的宽度。

(3)使用多个级联的触发器作为同步器,通过对信号进行本时钟域内打拍降低亚稳态发生的概率。

(4)降低电路的工作频率(不建议)

(5)降低电路中的信号变化频率

正文:

[1] 简介同步电路和异步电路

首先简单介绍一下同步电路和异步电路的区别:

同步电路:电路中所有的受时钟控制的单元所使用的时钟都来自一个时钟源,由一个时钟进行控制。

异步电路:把电路中所有的受时钟控制的单元分为不同的部分,每部分使用的时钟是单独产生的,时钟之间是没有任何的关系。

[2] 简介为什么亚稳态发生在异步电路

在同步电路的设计中,我们可以了解到时钟和数据具有一定的时间关系。我们在设计中满足这种关系之后,同步电路的输出端在一定时间的传输延迟下会输出一个稳定的状态(电平),因为同步电路总是满足所需要的时间关系同时输出稳定的状态,所以在同步电路中不会产生亚稳态。

但是在异步电路的设计中,每个受不同时钟控制的电路在进行信号传输或者交互的时候,由于每个不同电路的时钟是没有任何关系的,所以信号在从一个时钟域传输到另一个时钟域的时候,信号和时钟可能就不会满足电路正常工作的时间要求,因为满足不了电路的正常工作要求,电路就可能会出现一些未定义的状态,电路处于的这种状态就被称为亚稳态。同时芯片内部的电路是互相连通的,所以一旦一个电路逻辑出现这种亚稳态的情况,那么这种亚稳态会持续传播到其他的电路,导致整个电路可能无法工作。

[3] 亚稳态发生的具体电路单元

上面所说,异步电路设计的时候,在进行不同的时钟域信号传输的时候会产生亚

稳态。那么具体亚稳态发生的电路单元是什么呢?触发器

触发器是我们在设计电路时主要用到的时序元件,同时亚稳态产生的根本问题也就是数据在不同时钟下进行数据传输的时候,违背了触发器所需要的建立和保持时间的要求,导致触发器进行状态变换或者输出的时候,不能正常进行状态切换和逻辑输出。所以我们在设计电路的时候,需要注意跨不同的时钟域进行数据传输时候,降低这种亚稳态发生的概率,使触发器能够正常工作。

PS:电路中基本所有的时序问题最终归结的部分也就是电路中的触发器,所以满足触发器的时序是电路时序检查的第一要义

[4] 寄存器亚稳态波形

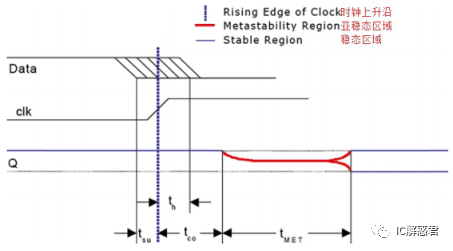

对于一个触发器来说,其时序如上图所示,当触发器在时钟clk上升沿进行数据捕捉时,此时的数据Data处于一个未知的状态或者电平(对触发器来说没有满足其输入的要求),所以触发器内部变化进行输出的状态就未定义。

同时也能从图看出,触发器输出的状态Q这种未定义的状态会持续Tmet时间,然后恢复稳定状态。这也就是说,亚稳态会持续一些时间然后恢复到稳定的状态。持续的时间相对不确定,一般是一到两个时钟周期。

[5] 亚稳态的窗口

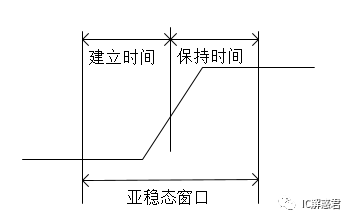

上文有提到,电路中所有的时序部分最终会归结到电路中的触发器。所以对于触发器来说,需要使触发器能够正常工作,则就需要满足触发器对输入信号和时序的要求。对于触发器,时钟和信号需要保持一定的关系,在时钟沿到来之前和时钟沿到来之后,需要保持信号在这段时间内稳定。这样触发器才能正常工作。时钟沿之前的需要保持的时间叫做建立时间,时钟沿之后保持的时间叫做保持时间。亚稳态窗口的宽度也就是:建立时间+保持时间。

如果亚稳态窗口比较大,这样对于信号和时钟要求的就比较严格,就会容易进入亚稳态。

PS:所以一般来说,最新的工艺和器件的亚稳态窗口比较小,采取这些器件,能够在一定程度上降低进入亚稳态的概率。

[6] 亚稳态出现的概率

[7] 避免亚稳态的方法

未完待续

有问题大家可以后台留言,谢谢大家。

未完待续,下文更精彩。。。。。。。。

最后

以上就是独特星月最近收集整理的关于漫谈IC亚稳态的全部内容,更多相关漫谈IC亚稳态内容请搜索靠谱客的其他文章。

发表评论 取消回复