围绕以下问题学习亚稳态:亚稳态是什么?为什么产生亚稳态?亚稳态导致什么后果?亚稳态能否根除?避免亚稳态的措施?

一、亚稳态是什么?

触发器的输出(产生毛刺或)保持不稳定的状态(输出介于有效状态间的中间级电平),无法确定亚稳态什么时候稳定也无法确定亚稳态稳定在什么电平。

二、为什么产生亚稳态?

产生亚稳态是由于输入信号和时钟的关系不符合时序要求,也就是违背建立时间和保持时间,(或者说输入信号或时钟在亚稳态窗口变化)。

是否违背建立时间和保持时间必定会进入亚稳态?

不是,触发器是否进入亚稳态和返回稳态所需的时间取决于生产器件的工艺技术和外界环境。

什么情况下可能违背时序要求?

1、输入信号是异步信号;

2、信号在两个频率不同或频率相同但相位或偏移不同的时钟域下跨时钟域工作;

3、输入信号经过组合逻辑延迟在亚稳态窗口变化;

4、时钟偏移或抖动高于容限值。

亚稳态常发生在什么系统?

亚稳态常发生在异步系统,因为输入信号和时钟的关系不固定,易违反建立时间和保持时间,易产生亚稳态。而同步系统中输入信号和时钟的关系固定,不出现亚稳态。

三、亚稳态导致什么后果?

亚稳态会造成系统故障或过多的传播延迟。亚稳态会传播。

亚稳态窗口是什么?对亚稳态的影响?

亚稳态窗口由建立时间和保持时间决定,亚稳态窗口越小,器件进入亚稳态的概率越小。

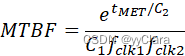

平均故障时间 ?

?

增大MTBF:增加同步寄存器链的长度,提高设计的时序裕量

四、亚稳态能否根除?

不能,只能减小亚稳态发生的概率。

五、避免亚稳态的措施?

1.确保时钟周期足够长/减少采样速率,长于准稳态的解析时间,长于到下一级触发器的路径上的任何组合逻辑延迟;

2.使用同步器(不能阻止亚稳态传播,只能减小亚稳态发生概率)

使用两级以上寄存器采样可以有效地减少亚稳态继续传播的概率。原理是使第一个触发器的输出端存在亚稳态,经过一个Clk周期后,第二个触发器D端的电平仍未稳定的概率非常小,因此第二个触发器Q端基本不会产生亚稳态。理论上如果再添加一级寄存器,使同步采样达到3级,则末级输出为亚稳态的概率几乎为0。

3.采用响应更快的触发器(缩短亚稳态窗口Tw,与工艺有关,受硬件制约)

4.改善时钟质量,用边沿变化快速的时钟信号

5.使用亚稳态硬化触发器(专为高带宽设计并减少为时钟域输入电路而优化的采样时间)

6.避免使用dV/dt低的输入信号

注:

使用两级寄存器采样仅能降低亚稳态的概率,但是并不能保证第二级输出的稳态电平就是正确电平。前面说过经过Resolution time之后寄存器输出的电平是一个不确定的稳态值,也就是说这种处理方法并不能排除采样错误的产生,这时就要求所设计的系统对采样错误有一定的容忍度。

有些应用本身就对采样错误不敏感,如一帧图像编码,一段话音编码等。而有些系统对错误采样比较敏感。这类由于亚稳态造成的采样是一些突发的错误,所以可以采用一些纠错编码手段完成错误的纠正。

最后

以上就是老实纸鹤最近收集整理的关于亚稳态知识点一、亚稳态是什么?二、为什么产生亚稳态?三、亚稳态导致什么后果?四、亚稳态能否根除?五、避免亚稳态的措施?注:的全部内容,更多相关亚稳态知识点一、亚稳态是什么?二、为什么产生亚稳态?三、亚稳态导致什么后果?四、亚稳态能否根除?五、避免亚稳态内容请搜索靠谱客的其他文章。

发表评论 取消回复