1.1 什么是亚稳态?

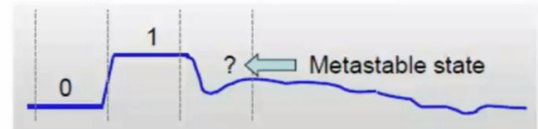

大家熟知的数字逻辑器件是有确定的0和1电平的,而0和1电平在数字逻辑电路中是有一定的界限的,例如根据TTL电平规定:对于输出电路:电压大于等于(≥)2.4V为逻辑1;电压小于等于(≤)0.4V为逻辑0;那么当器件的电平信号处于2.4-0.4之间的电平信号就是数字电路中无法识别的状态。这就是亚稳态。简而言之,亚稳态就是长时间存在的,且电路无法识别的电平状态(无法判断是0还是1)。注意亚稳态和竞争冒险要区分开来。如果一个寄存器输出是亚稳态的话,那么后续的组合逻辑肯定会出现错误。亚稳态的表现可以如下图所示:

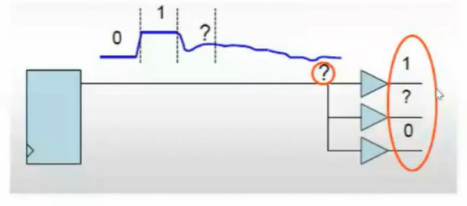

这就会导致亚稳态的信号在后续电路中传播。

1.2 什么会导致亚稳态的出现

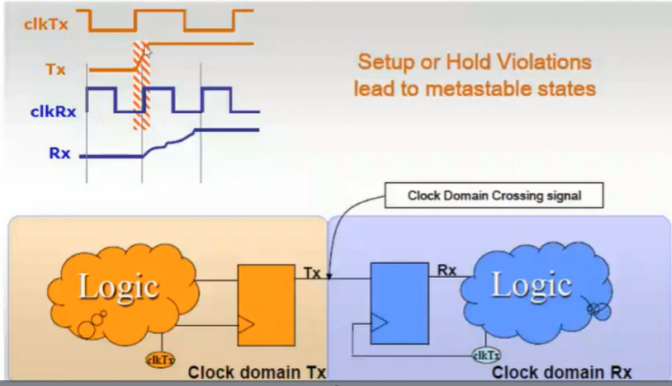

主要原因:寄存器不符合建立保持时间的约束。

建立时间: 时钟采样沿到来之前的一段时间内,数据必须保持不变。

保持时间:时钟采样后的一段时间内数据也要保持不变。

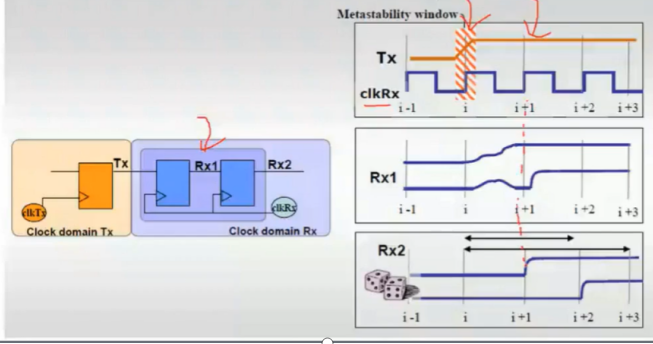

从图中可以看出,在不同的时钟域,clkRX采样时间很有可能落在TX信号过度时间,这就导致读寄存器的输出产生亚稳态。影响后续的电路。TX根具CLKTX时钟发送数据,在跨时钟域的时候通过跨时钟域的时钟信号对TX进行采样,由于采样寄存器不满足建立时间要求,所以会产生亚稳态信号。注意区别竞争冒险(毛刺)。有两种情况:第一种是亚稳态,后面的电路慢慢的死掉。第二逐渐趋向于0或者1.竞争冒险存在于组合逻辑电路中,亚稳态存在于时序逻辑电路中。

从图中可以看出,在不同的时钟域,clkRX采样时间很有可能落在TX信号过度时间,这就导致读寄存器的输出产生亚稳态。影响后续的电路。TX根具CLKTX时钟发送数据,在跨时钟域的时候通过跨时钟域的时钟信号对TX进行采样,由于采样寄存器不满足建立时间要求,所以会产生亚稳态信号。注意区别竞争冒险(毛刺)。有两种情况:第一种是亚稳态,后面的电路慢慢的死掉。第二逐渐趋向于0或者1.竞争冒险存在于组合逻辑电路中,亚稳态存在于时序逻辑电路中。

在同步电路中,很少出现亚稳态,除非是时钟设计出现很大的问题。而在异步逻辑中很容易出现亚稳态。异步逻辑没有统一的时钟,各级触发器的状态变化不是在统一的时钟作用下完成的(触发器的状态变化不是同时发生的)。没有统一的时钟也就意味着控制信号随时可能发生变化,想要满足建立时间和保持时间的约束当然也就变的十分困难。

亚稳态会坚持多久?受哪些因素影响呢?

亚稳态受:温度、工艺、电压、电磁波的影响。

1.3 亚稳态可以自动恢复吗?

亚稳态是可以自己恢复的,但是恢复后的状态不一定是正确的状态,如果是错误的状态,会导致后续的逻辑混乱。但是如果亚稳态持续的时间很长的话,被后一级的寄存器捕获到会照成亚稳态的传播,加长亚稳态的持续时间。这是很严重的问题。

1.4 亚稳态如何解决?

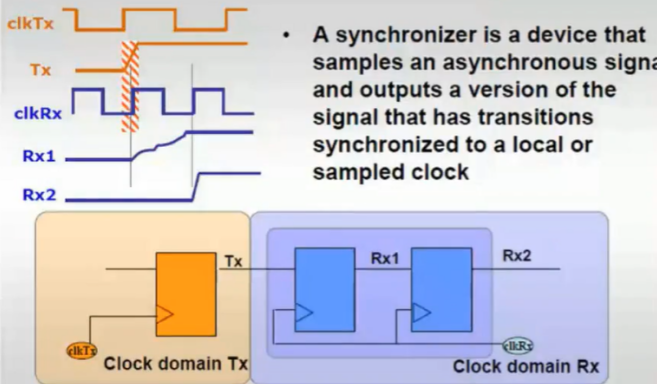

可以利用同步电路消除亚稳态。一般采用两级同步电路。对于单比特信号而言,

单比特信号,只需做一个两级同步,在发送端,用原时钟寄存器打一拍后在发送端发送,在接收端,用接收时钟,控制寄存器打两拍。可见在第一个时钟周期内,是出现亚稳态的,但是在第二个时钟周期后亚稳态结构就恢复了。这样就可以防止亚稳态的发生。

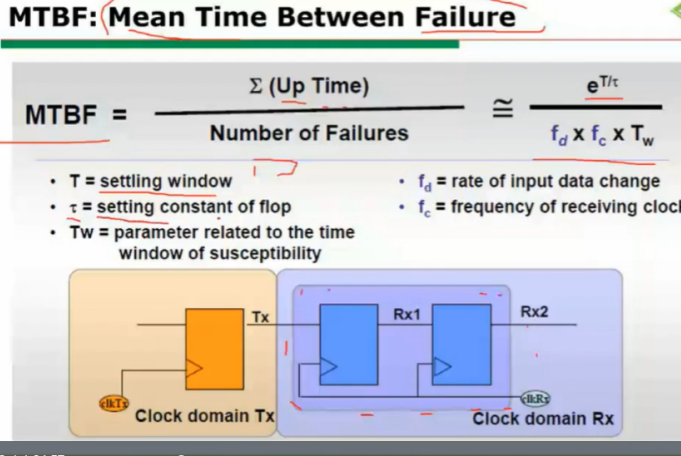

计算信号的亚稳态时间间隔:

其中fd是发送时钟频率,fc是接收时钟频率。其他都是厂家给的一些参数。

两级同步的具体过程:

这里注意,亚稳态的恢复可以是0或者1状态,这是不定的。可从图中看出,当clkRx时钟信号对TX进行采集的时候,在两级同步的第一寄存器的输出信号:RX1会有亚稳态,但是由于RX2信号的采集采的是上一个时钟沿的信号,所以在亚稳态恢复之前RX2是不会变化的,当亚稳态恢复稳定后再采集。就能避免亚稳态。但是这里注意稳定状态是0和1的情况是不一样的。

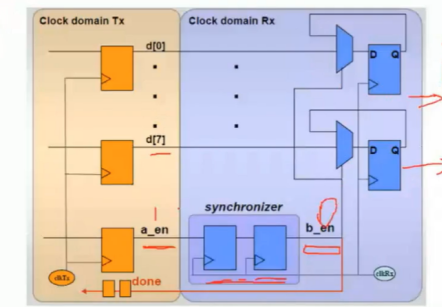

上面所描述的是单比特信号,用的是两级同步信号,但是对于跨时钟域的数据传输系统而言,一般为多比特信息的传输,这又改怎么去避免亚稳态呢?

如果每个比特都用两级的话,消耗资源太大了。为了节约资源可以通过一个交互信号来代替所有的两级同步信号。

最后

以上就是专注小伙最近收集整理的关于IC笔记之亚稳态1.1 什么是亚稳态?1.2 什么会导致亚稳态的出现1.3 亚稳态可以自动恢复吗?1.4 亚稳态如何解决?的全部内容,更多相关IC笔记之亚稳态1.1内容请搜索靠谱客的其他文章。

发表评论 取消回复