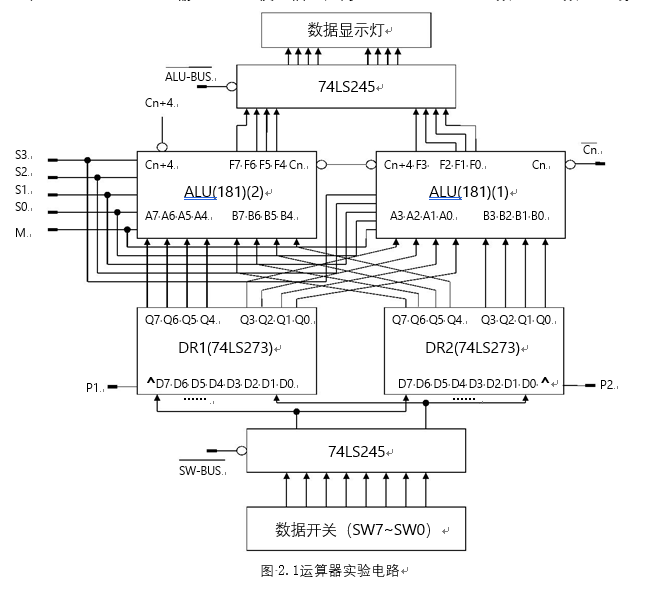

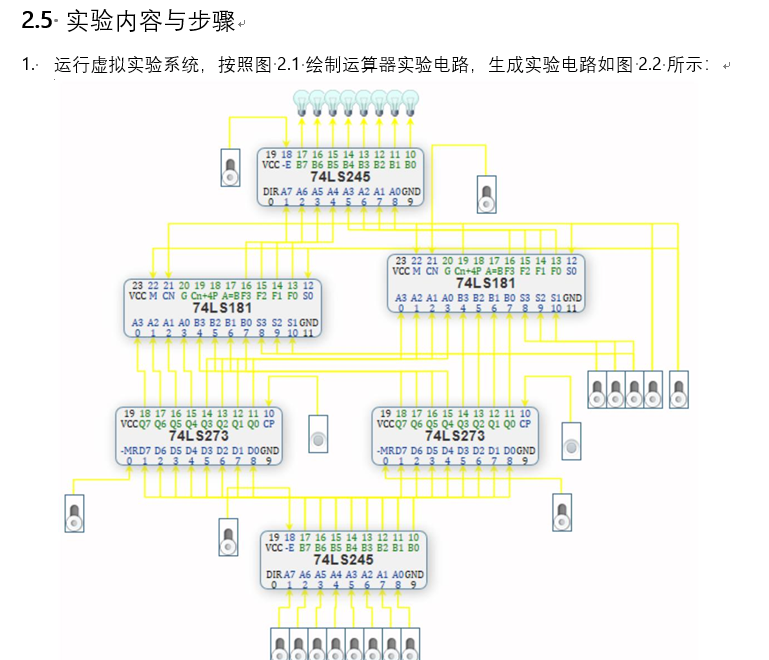

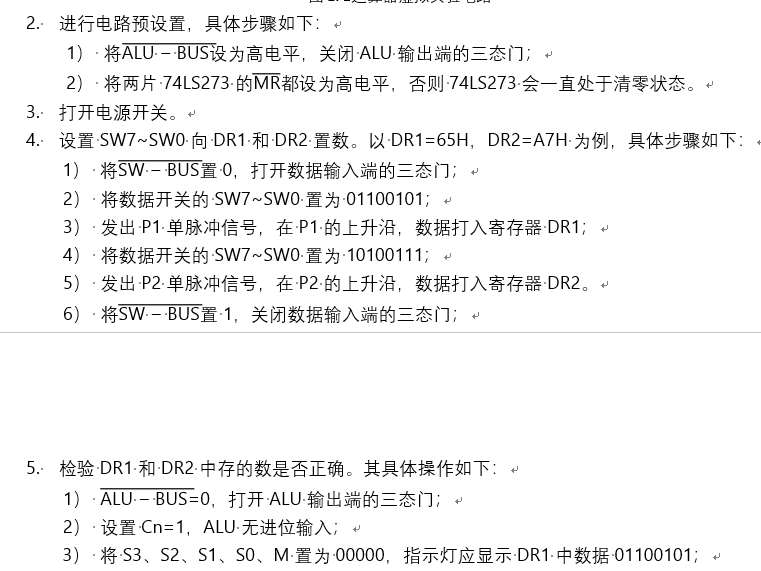

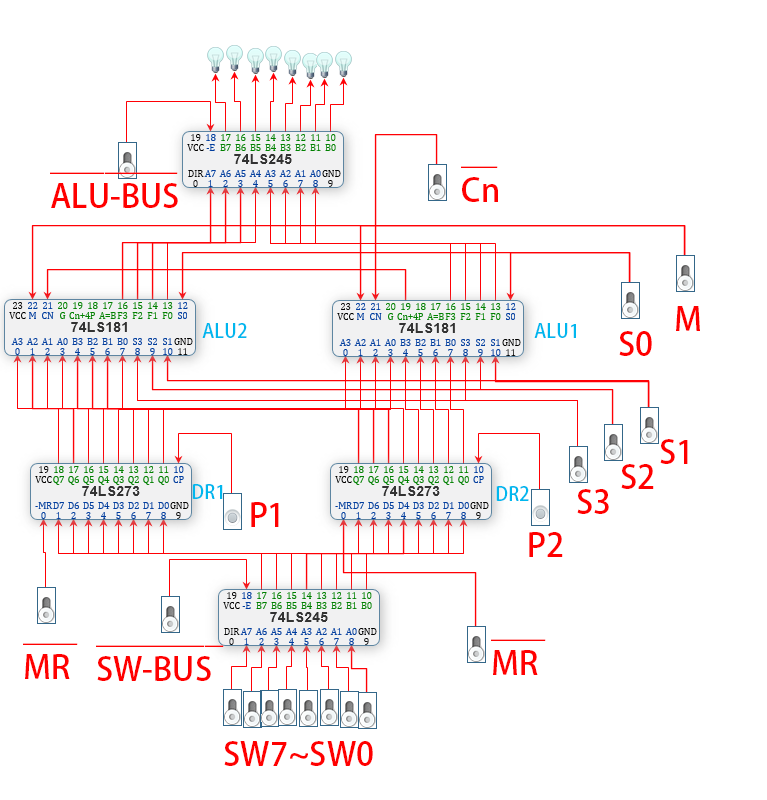

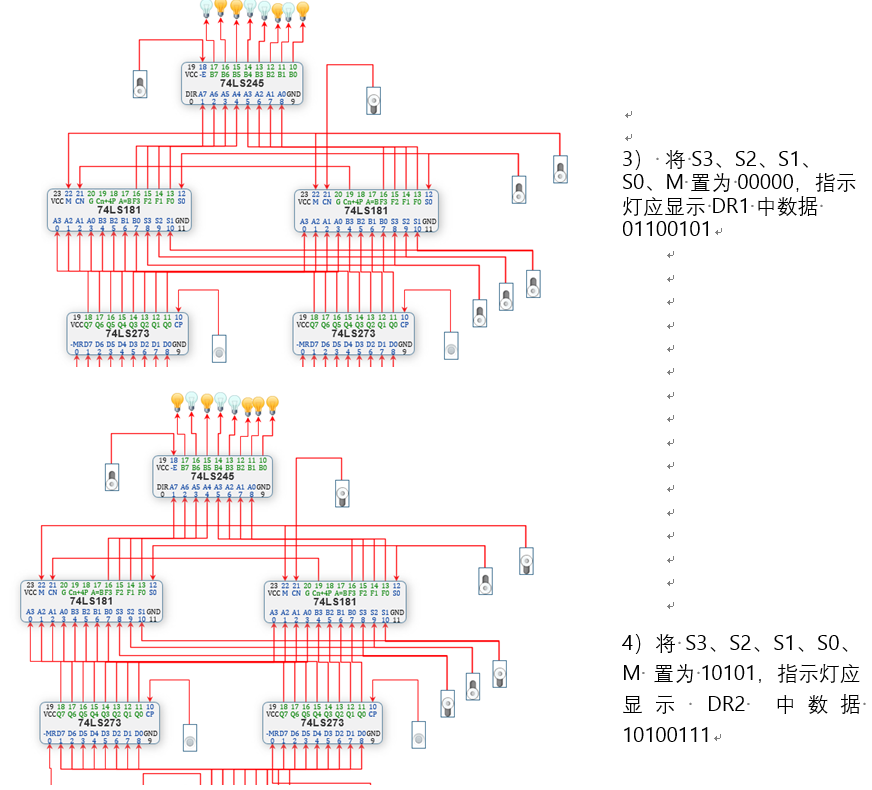

1. 主要由4 位算术逻辑运算单元 74LS181,8 位数据锁存器74LS273,三态输出的 8 组总线收发器 74LS24,开关、数据显示灯组成。

2. 减法取反码运算后用加法器实现,结果输出为A减B减1在最末位产生一个强迫进位(加1),以得到A减B的结果

3. 级联方式:并行、串行。串行:将低4位74LS181的进位输出引脚Cn+4与高4位74LS181的进位输入引脚Cn连接。当M=0时,M对进位信号没有任何影响,Fi值与操作数Ai,Bi以及低位向本位进位Cn+1有关,进行算数运算时,操作数用补码表示;并行:当M=1时进行逻辑运算,封锁了各位的进位输出Cn+i=0,各位的运算结果Fi仅与操作数Ai、Bi有关。与引脚M,Cn,Cn+i,Cn有关。并行运算快,串行需要等待低位产生进位信号。

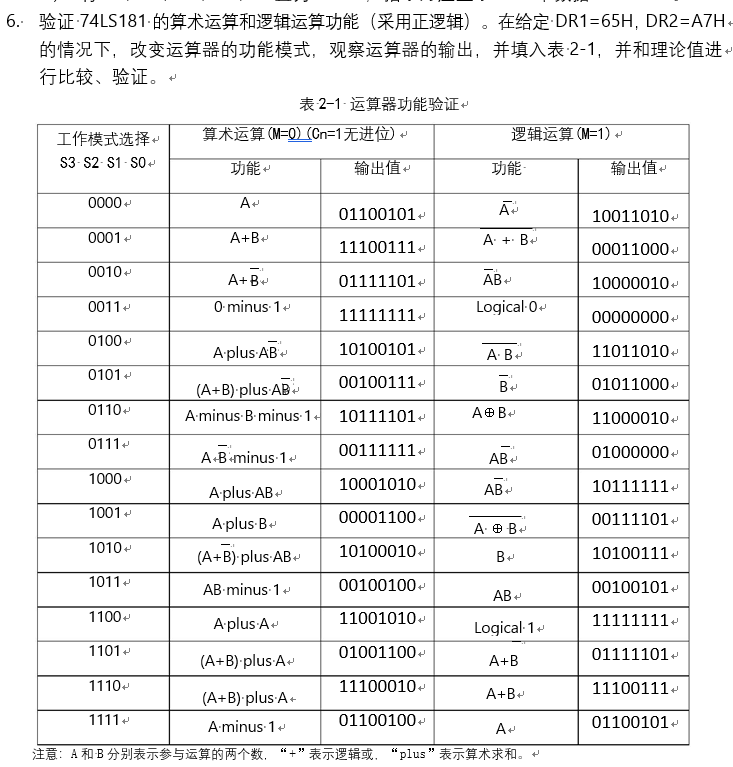

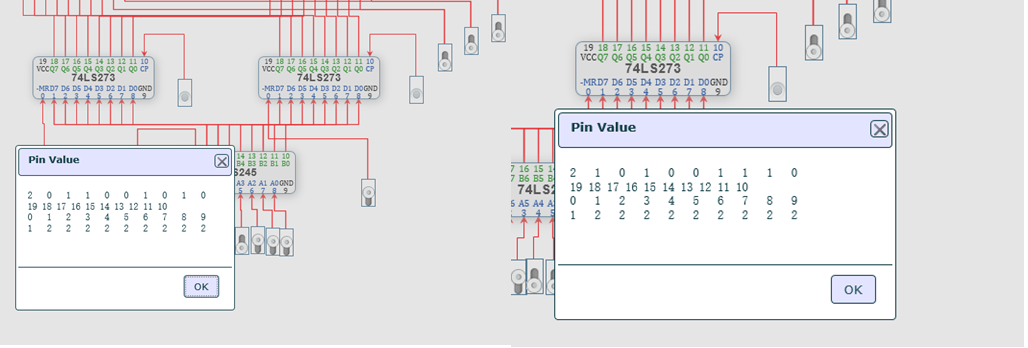

寄存器 DR1 寄存器 DR2

寄存器 DR1 寄存器 DR2

最后

以上就是顺利手套最近收集整理的关于多思计算机组成原理实验二:全加器实验的全部内容,更多相关多思计算机组成原理实验二内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复