FPGA学习篇之半加器与全加器

半加器与全加器的区别与联系

文章目录

- FPGA学习篇之半加器与全加器

- 前言

- 一、半加器

- 1.逻辑分析

- 2.代码编写

- 二、全加器

- 1.逻辑分析

- 2.代码编写

- 三、总结

前言

加法器作为数字电路中基本的器件,主要作用是实现两个数的加法运算。加法器有半加器和全加器之分,区别是半加器不接受低位的进位信号,全加器接受来自低位的进位信号并参与运算。

一、半加器

1.逻辑分析

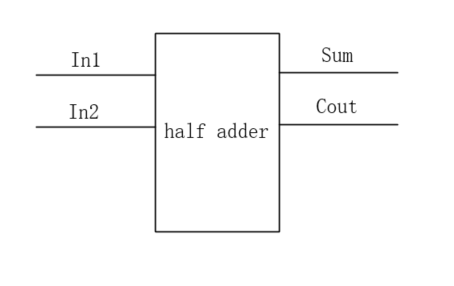

如下图所示,半加器只有两个输入和两个输出

半加器的真值表如下

| In1 | In2 | Sum | Cout |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

通过真值表可以得出: S u m = I n 1 ⊕ I n 2 Sum = In1 oplus In2 Sum=In1⊕In2, C o u t = I n 1 & I n 2 Cout = In1 & In2 Cout=In1&In2

2.代码编写

module adderN#(parameter N = 4)(

input [N-1 : 0] in1,

input [N-1 : 0] in2,

output [N-1 : 0] sum,

output cout

);

assign {cout,sum} = in1 + in2;

//always@(*)

// {cout,sum} = in1 + in2;

endmodule

二、全加器

1.逻辑分析

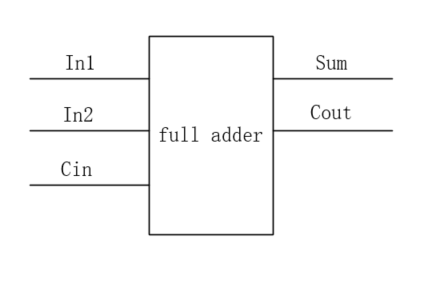

如下图所示,全加器的输入有来自低位的仅为信号

全加器的真值表如下:

| In1 | In2 | Cin | Sum | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

通过卡诺图化简可以得出

S

u

m

=

C

i

n

′

(

I

n

1

⊕

I

n

2

)

+

C

i

n

(

I

n

1

⊙

I

n

2

)

=

C

i

n

⊕

I

n

1

⊕

I

n

2

Sum =Cin'( In1 oplus In2) + Cin( In1 odot In2) = Cin oplus In1 oplus In2

Sum=Cin′(In1⊕In2)+Cin(In1⊙In2)=Cin⊕In1⊕In2 ,

C

o

u

t

=

C

i

n

(

I

n

1

∥

I

n

2

)

+

(

I

n

1

&

I

n

2

)

Cout = Cin( In1 parallel In2) +(In1 & In2)

Cout=Cin(In1∥In2)+(In1&In2)

2.代码编写

module adderN#(parameter N = 4)(

input [N-1 : 0] in1,

input [N-1 : 0] in2,

input cin,

output [N-1 : 0] sum,

output cout

);

assign {cout,sum} = in1 + in2 + cin;

//assign {cout,sum[N-1 : 0]} = {in1[N-1],in1[N-1 : 0]} + {in2[N-1],in2[N-1 : 0]} + cin;

endmodule

三、总结

文中通过真值表和逻辑表达式推导了半加器和全加器的原理,同时编写了verilog代码。全加器可以用两个半加器和一个或门实现,所以全加器的代码也可以调用两个半加器,再将两个半加器输出的进位信号相或得到。

最后

以上就是羞涩嚓茶最近收集整理的关于半加器与全加器FPGA学习篇之半加器与全加器前言一、半加器二、全加器三、总结的全部内容,更多相关半加器与全加器FPGA学习篇之半加器与全加器前言一、半加器二、全加器三、总结内容请搜索靠谱客的其他文章。

发表评论 取消回复