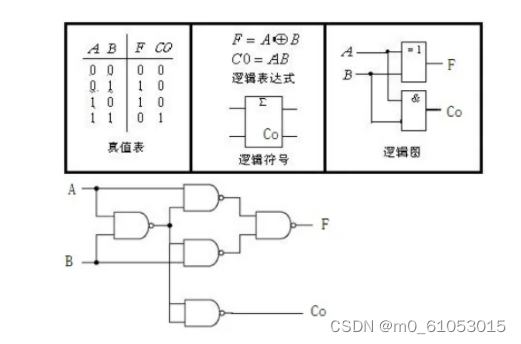

1、用与非门设计半加器

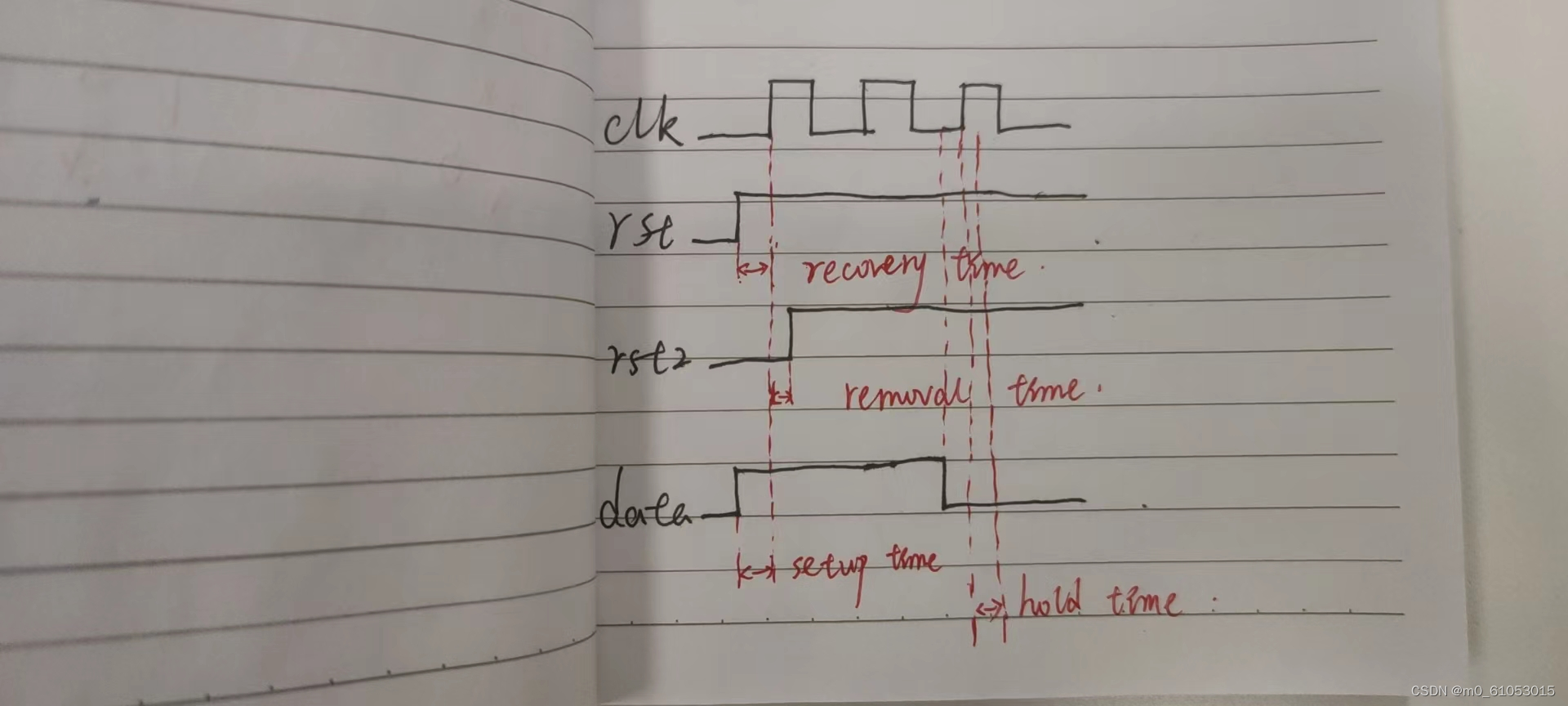

2、setup/hold/recovery/removal time 名词解释 并画图实例。

setup time 是建立时间,在时钟采样沿到来之前,数据输入保持稳定不变的最小时间。

hold time 是保持时间,在时钟采样沿到来之后,数据输入保持稳定不变的最小时间。

STA时,如果DFF的异步rst和该DFF的时钟有相位关系,则需要进行removal和recovery的检查。removal和recovery检查的目的是让DFF的异步rst信号在时钟沿附近满足建立/保持时间。当然,如果异步复位信号与时钟没有任何相位关系,则没有必要做removal time /recovery time 检查。

恢复时间(Recovery Time)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。 这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步控制信号的解除与“下个时钟沿”离得太近(但在这个时钟沿之前),没有给寄存器留有足够时间来恢复至正常状态,那么就不能保证“下个时钟沿”能正常作用,也就是说这个“时钟沿”可能会失效。

去除时间(Removal)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。 这个时间的意义是,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近(但在这个时钟沿之后),那么就不能保证这个“有效时钟沿”能正常作用,也就是说这个“有效时钟沿”可能会失效。

3、亚稳态解释及解决方案

亚稳态:如果数据传输中不满足触发器的Tsu和Th,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

有亚稳态产生,我们就要对亚稳态进行消除,常用对亚稳态降低有三种方式:

(1) 对异步信号进行同步处理;

(2) 采用FIFO对跨时钟域数据通信进行缓冲设计;

(3) 对复位电路采用异步复位、同步释放方式处理。

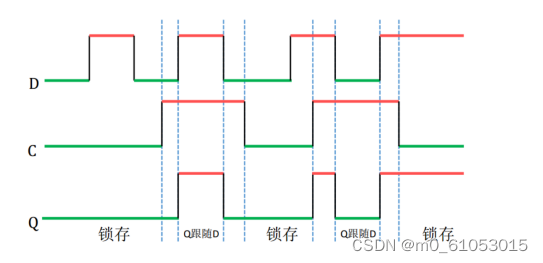

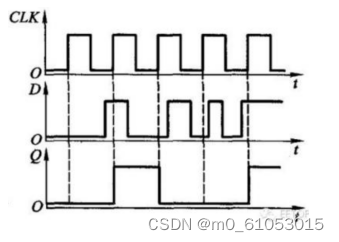

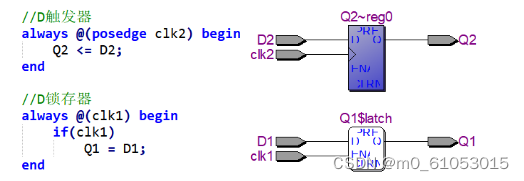

4、锁存器/触发器不同点,画出时序图、写出Verilog代码。

锁存器是一种对脉冲电平(也就是0或者1)敏感的存储单元电路,而触发器是一种对脉冲边沿(即上升沿或者下降沿)敏感的存储电路。

D锁存器

D触发器

代码实现

5、格雷码的特点,3位二进制的格雷码

在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码;

000/001/011/010/110/111/101/100

6、低功耗设计方法

1、静态低功耗技术

(1)多阈值工艺(Multi-Vt Design)方法

(2)电源门控(Power Gating)方法

(3)体偏置(Body Bias)

2、动态低功耗技术

(1)多电压域(Multi-Voltage Domain)

(2)预计算

(3)门控时钟(Clock Gating)

3、门级优化技术

(1)毛刺的消除

(2)逻辑级优化

(3)物理级优化

(4)控制输入向量

4、补充:RTL级的一些低功耗设计方法

7、三分频电路的Verilog实现,尽量50%占空比。

module div3_half(

input Sys_clk,

input Sys_reset,

output div3 ,

output clk1,

output clk2

);

reg clk1;//2/3 is high posedge

reg clk2;//2/3 is high negedge

//counter

reg [1:0]count;

always @ (posedge Sys_clk )

if(!Sys_reset)

count <= 2'b0;

else if(count ==2'd2)

count <= 2'b0;

else

count <= count +1'b1;

always @(posedge Sys_clk )

if(!Sys_reset)

begin

clk1 <=1'b1;

end

else if(count == 2'd1 | count == 2'd2)

clk1 <= ~clk1;

always @(negedge Sys_clk )

if(!Sys_reset)

begin

clk2 <=1'b1;

end

else if(count == 2'd2 | count ==2'd1)

clk2 <= ~clk2;

//------------------------------------------------

assign div3 =clk1 & clk2;

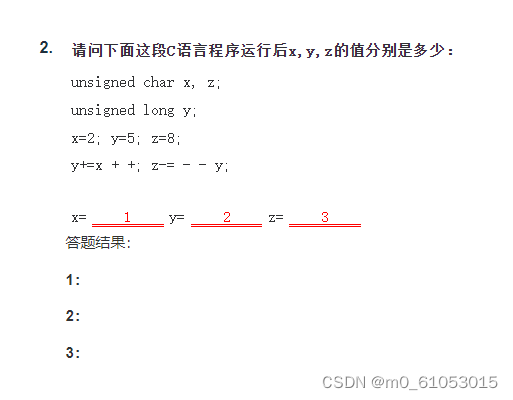

endmodule8、c语言答题

x = 3,y =6, z =2.

最后

以上就是传统大叔最近收集整理的关于南京沁恒微电子笔试题-数字IC设计的全部内容,更多相关南京沁恒微电子笔试题-数字IC设计内容请搜索靠谱客的其他文章。

发表评论 取消回复