我是靠谱客的博主 伶俐便当,这篇文章主要介绍verilog 大小端转换 38译码器 边沿检测 ROM 格雷码计数器大小端转换:38译码器边沿检测:ROM:格雷码计数器,现在分享给大家,希望可以做个参考。

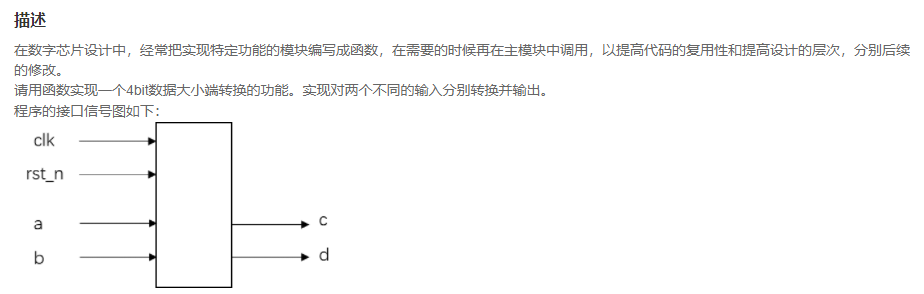

大小端转换:

`timescale 1ns/1ns

module function_mod(

input clk,

input rst_n,

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);

function [3:0] data_rev; // 函数名和返回变量名相同 data_rev

input [3:0] din; // 声明输入端口

begin

data_rev[0] = din[3];

data_rev[1] = din[2];

data_rev[2] = din[1];

data_rev[3] = din[0];

end

endfunction

assign c = data_rev(a); // 调用函数

assign d = data_rev(b);

endmodule

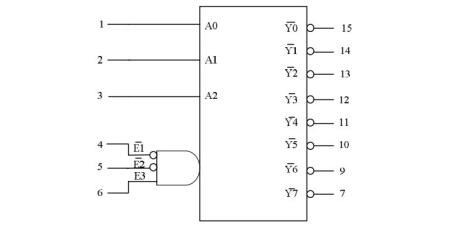

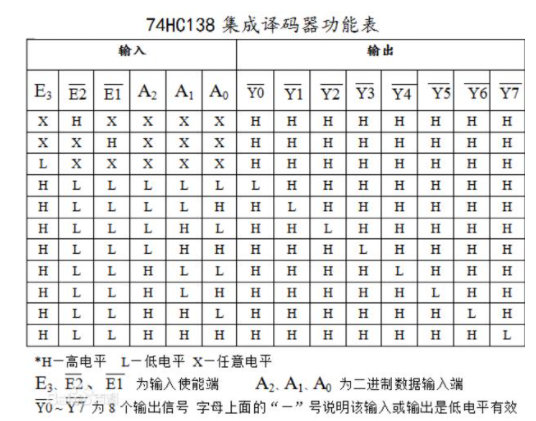

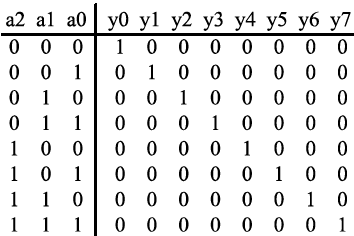

38译码器

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E;

assign E = E3 & ~E1_n & ~E2_n; // 1&0&0 = 0

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0); //000

assign Y1_n = ~(E & ~A2 & ~A1 & A0); //001

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

module Decoder38(data_in,data_out,enable);

input [2:0] data_in;

input enable;

output [7:0] data_out;

reg [7:0] data_out;

always @(data_in)

begin

if (enable == 1)

case(data_in)

3'b000: data_out = 8'b00000001;

3'b001: data_out = 8'b00000010;

3'b010: data_out = 8'b00000100;

3'b011: data_out = 8'b00001000;

3'b100: data_out = 8'b00010000;

3'b101: data_out = 8'b00100000;

3'b110: data_out = 8'b01000000;

3'b111: data_out = 8'b10000000;

default: data_out = 8'bxxxxxxxx;

endcase

else

data_out = 8'b11111111;

end

endmodule

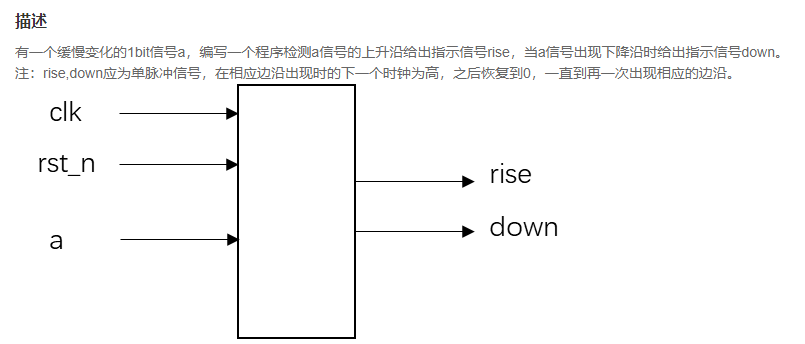

边沿检测:

`timescale 1ns/1ns

module edge_detect(

input clk,

input rst_n,

input a,

output reg rise,

output reg down

);

reg d;

always @(posedge clk or negedge rst_n)

if (!rst_n)

d <= 1'b0;

else

d <= a;

always@(posedge clk or negedge rst_n)begin

if(~rst_n)begin

rise<=1'b0; down<=1'b0;

end

else if(a==1 && d==0) begin

rise <=1'b1;

down <=1'b0;

end

else if(a==0 && d==1) begin

rise <=1'b0;

down <=1'b1;

end

else begin

rise<=1'b0;

down<=1'b0;

end

end

endmodule

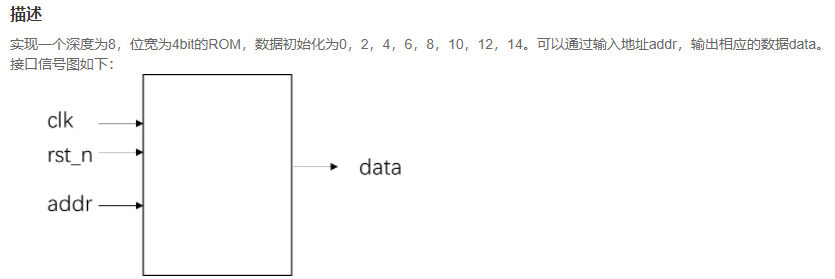

ROM:

`timescale 1ns/1ns

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg[3:0] rom_data[7:0]; // 8个rom_data寄存器,每个4bit

always @(posedge clk or negedge rst_n)begin

if(~rst_n)begin // 初始化

rom_data[0] <= 4'd0;

rom_data[1] <= 4'd2;

rom_data[2] <= 4'd4;

rom_data[3] <= 4'd6;

rom_data[4] <= 4'd8;

rom_data[5] <= 4'd10;

rom_data[6] <= 4'd12;

rom_data[7] <= 4'd14;

end

else begin // 每个时钟周期维持数据

rom_data[0] <= rom_data[0];

rom_data[1] <= rom_data[1];

rom_data[2] <= rom_data[2];

rom_data[3] <= rom_data[3];

rom_data[4] <= rom_data[4];

rom_data[5] <= rom_data[5];

rom_data[6] <= rom_data[6];

rom_data[7] <= rom_data[7];

end

end

assign data = rom_data[addr]; // 按地址输出

endmodule

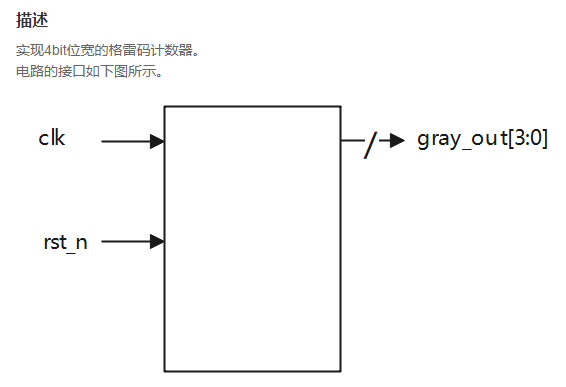

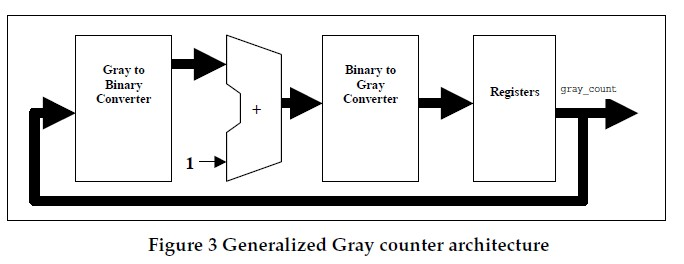

格雷码计数器

module gray_counter(

input clk,

input rst_n,

output reg [3:0] gray_out

);

//格雷码转二进制

wire [3:0] gray_wire; // 格雷码 wire进 一根线送进

reg [3:0] bin_out; // 二进制 reg出

always @(posedge clk or negedge rst_n)begin

if(~rst_n) begin

bin_out <= 4'b0;

end

else begin

bin_out[3] = gray_wire[3];

bin_out[2] = gray_wire[2]^bin_out[3];

bin_out[1] = gray_wire[1]^bin_out[2];

bin_out[0] = gray_wire[0]^bin_out[1];

end

end

//二进制加一

reg [3:0] bin_add_wire; // 二进制+1结果 reg出

always @(posedge clk or negedge rst_n)begin

if(~rst_n) begin

bin_add_wire <= 4'b0;

end

else begin

bin_add_wire <= bin_out + 1'b1; // bin_out:格雷码转二进制结果

end

end

//二进制转格雷码

assign gray_wire = (bin_add_wire >> 1) ^ bin_add_wire; // 同一根线送出

// 时钟上升沿到来,送进输出

always @(posedge clk or negedge rst_n)begin

if(~rst_n) begin

gray_out <= 4'b0;

end

else begin

gray_out <= gray_wire;

end

end

endmodule

最后

以上就是伶俐便当最近收集整理的关于verilog 大小端转换 38译码器 边沿检测 ROM 格雷码计数器大小端转换:38译码器边沿检测:ROM:格雷码计数器的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复