计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能, 同时兼有分频功能。

计数器在数字系统中应用广泛,如电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

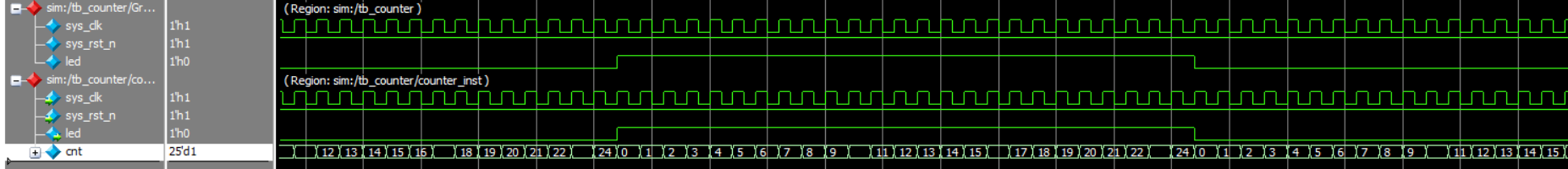

通过设计实现计数间隔为1s的计数器,通过使FPGA开发板上的LED灯在前0.5s处于点亮状态,后0.5s处于熄灭状态来验证。 输入有时钟,复位信号,一路输出信号到LED灯。

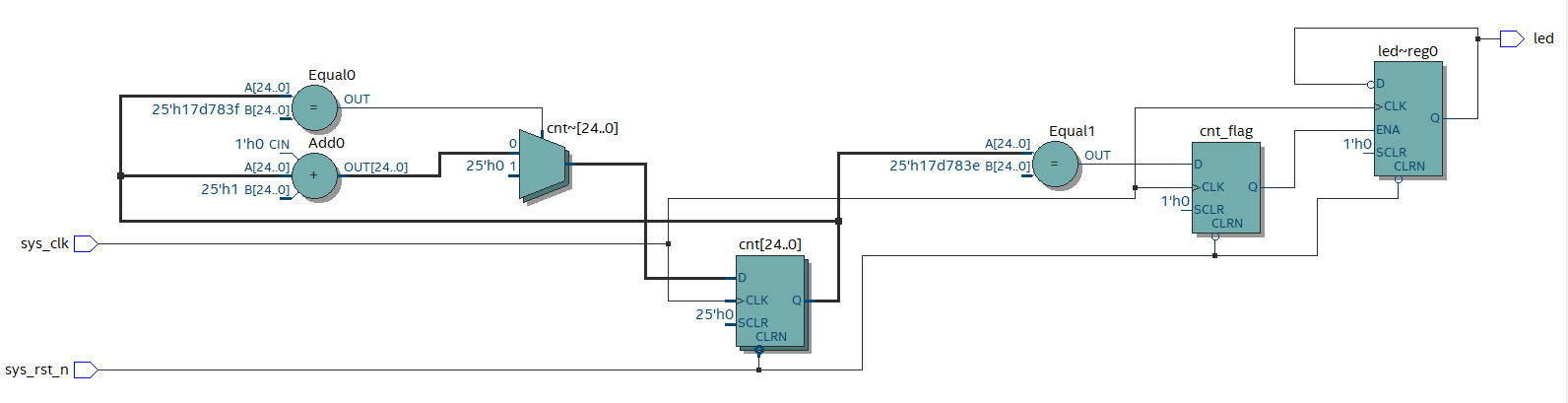

计数器有两点重要问题,一是控制好什么时候开始计数,另一个就是控制好什么时候清零。在该模块中只需要当复位信号撤销,时钟沿到来就可以计数,计数器清零有两种情况,一是计数器计满后自动清零,二是计数器计数到我们需要的计数值进行清零。由于计数间隔是1s,系统时钟是50MHz,那么其频率f=5*10^7Hz,则计数器在1s之内要完成5*10^7次计数。由于从0开始计数,所以最终计数是5*10^7-1,选择将计数到f/2 -1 时,对led输出信号取反来实现。

这里为了便于观察,将计数最大值定为24,即计数到最大值24 时,输出信号led波形取反,符合。

最后

以上就是鲤鱼冰棍最近收集整理的关于Verilog 语言 ——计数器的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复