文章目录

- 4.1 存储系统层次结构

- 1.基本存储体系

- 2.主存速度慢的原因

- 3.主存容量不足的原因

- 4.存储体系的层次化结构

- 5.存储体系层次化结构的理论基础

- 4.2 主存中的数据组织

- 1.存储字长

- 2.数据存储和边界的关系

- 3.大端与小端存储方式

- 4.3 静态存储器工作原理

- 1.SRAM存储单元结构

- 2.SRAM存储单元工作原理

- 3.静态存储器的结构

- 4.4 动态存储器工作原理

- 1.SRAM存储单元的不足

- 2.DRAM存储单元的基本结构

- 3.DRAM存储单元的工作原理

- 4.DRAM存储单元的刷新

- 5.DRAM与SRAM的对比

- 6.其他结构的DRAM存储单元

- 4.5 存储扩展

- 1.存储扩展的基本概念及类型

- 2.位扩展举例

- 3.字扩展举例

- 4.字位同时扩展

4.1 存储系统层次结构

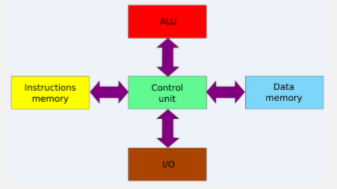

1.基本存储体系

- 输入设备将程序与数据写入主存;

- CPU取指令;

- CPU执行指令期间读数据;

- CPU写回运算结果;

- 输出设备输出结果;

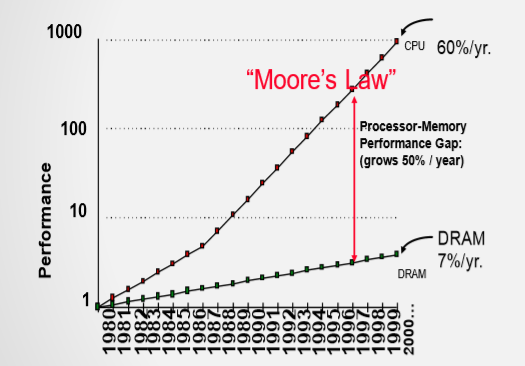

2.主存速度慢的原因

- 主存增速与CPU不同步;

- 指令执行期间多次访问存储器;

3.主存容量不足的原因

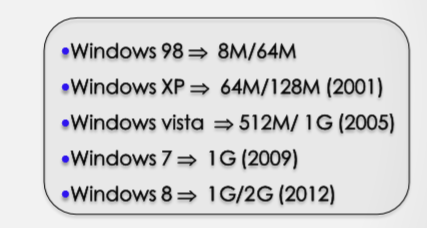

- 存在制约主板容量的技术因素 由CPU、主板等相关技术指标确定

- 应用对主存的需求不断扩大

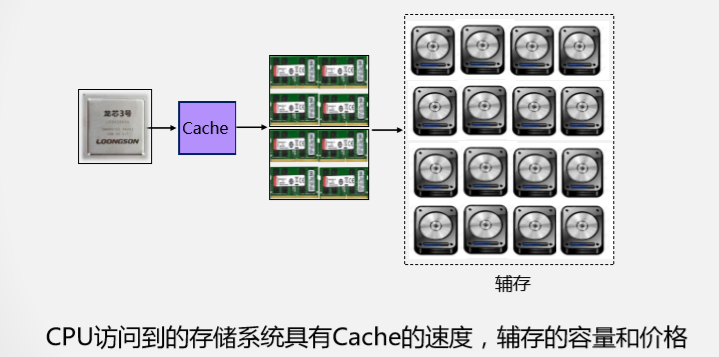

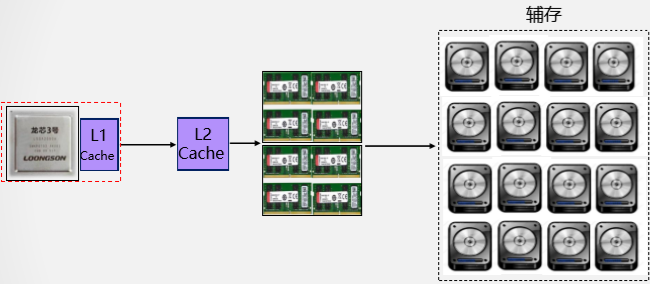

4.存储体系的层次化结构

- L1 Cache集成在CPU中,分数据Cache(D-Cache)和指令Cache(I-Cache)

- 早期L2 Cache在主板上或与CPU集成在同一电路板上。随着工艺的提高L2 Cache被集成在CPU内核中,不分D-Cache和I-Cache

哈佛结构(Harvard architecture)

- 是一种将指令储存和数据储存分开的存储器结构,可支持:数据和指令并行储存、指令预期,提高处理器的执行效率;另外,指令和数据可有不同的数据宽度,如Microchip公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度。

- 目前使用哈佛结构的:PIC系列、摩托罗拉公司的MC68系列、Zilog公司的Z8系列、ATMEL公司的AVR系列和ARM公司的ARM9、ARM10和ARM11。

5.存储体系层次化结构的理论基础

局部性原理

时间局部性

- 现在被访问的信息2在不久的将来还将再次被访问

- 时间局部性的程序结构体现:循环结构

空间局部性

- 现访问信息2,下一次访问2附近的信息

- 空间局部性的程序结构体现:顺序结构

4.2 主存中的数据组织

1.存储字长

- 主存的一个存储单元所包含的二进制位数;

- 目前大多数计算机的主存按字节编址,存储字长也不断加大,如16位字长、32位字长和64位字长;

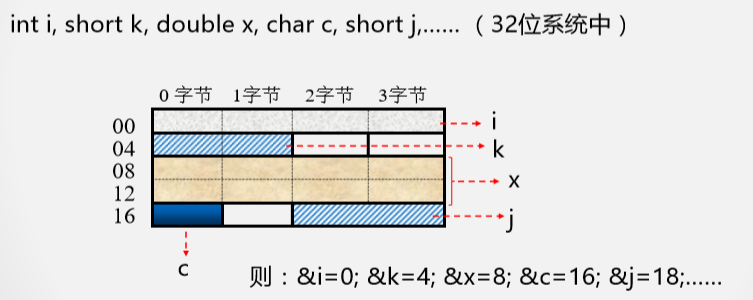

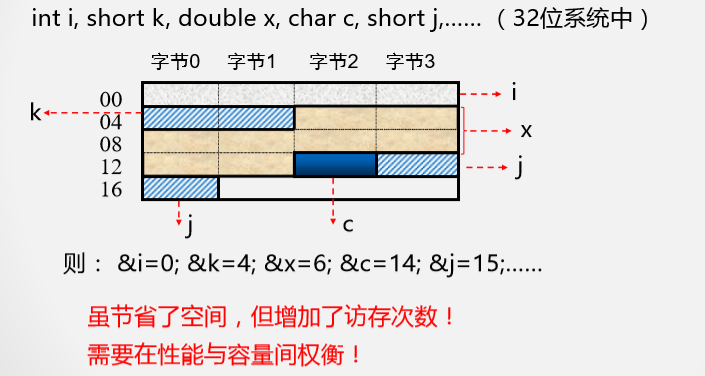

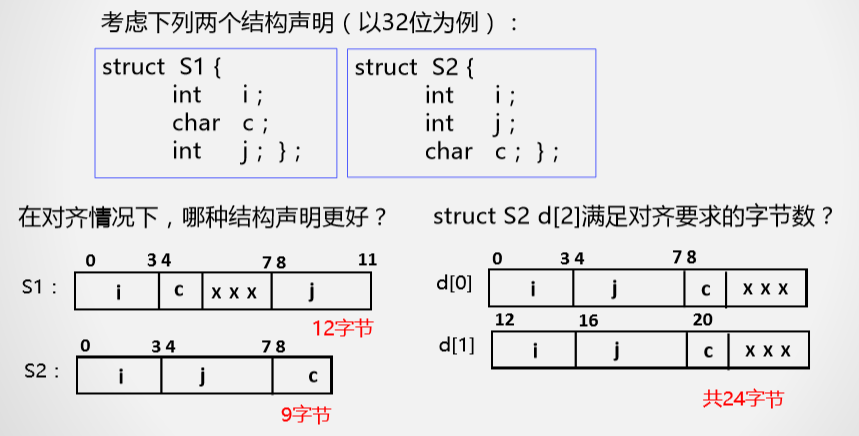

2.数据存储和边界的关系

- 按边界对齐的数据存储

- 未按边界对齐的数据存储

- 边界对齐与存储地址的关系(以32位为例)

- 双字长数据边界对齐的起始地址的最末三位为000(8字节整数倍);

- 单子长边界对齐的起始地址的末二位为00(4字节整数倍);

- 半字长边界对齐的起始地址的最末一位为0(2字节整数倍)

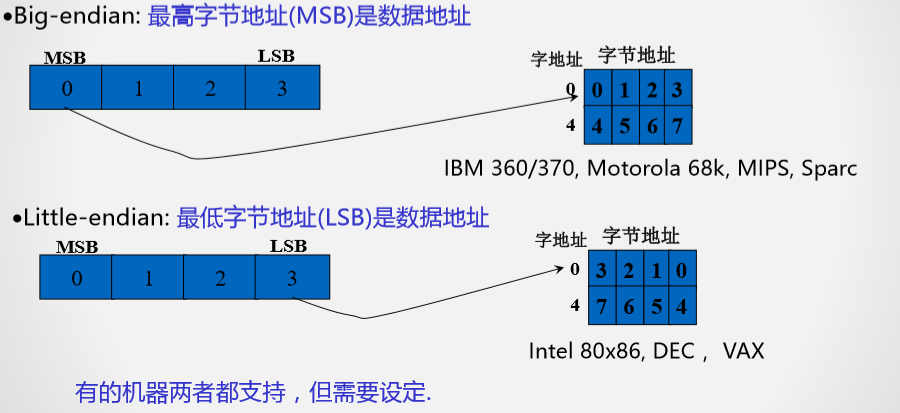

3.大端与小端存储方式

大端与小端模式详解

- Big-endian:最高字节地址(MSB)是数据地址

即高字节对应低地址,低字节对应高地址 - Little-endian:最低字节地址(LSB)是数据地址

即低字节对应低地址,高字节对应高地址

举例而言:数字0x12 34 56 78在内存中储存

大端模式下:

低地址----------->高地址

0x12 | 0x34 | 0x56 | 0x78

小端模式下:

低地址----------->高地址

0x78 | 0x56 | 0x34 | 0x12

4.3 静态存储器工作原理

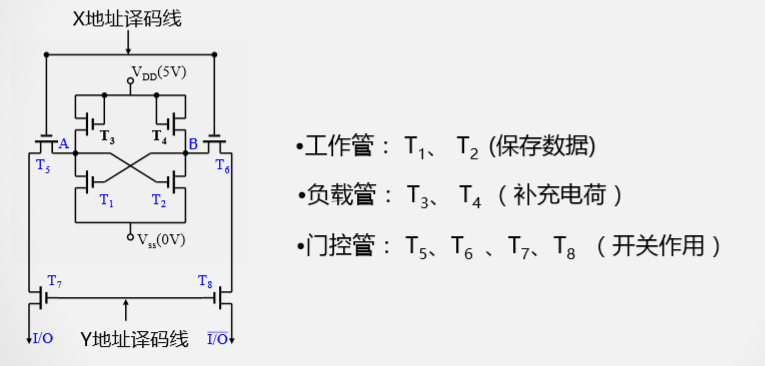

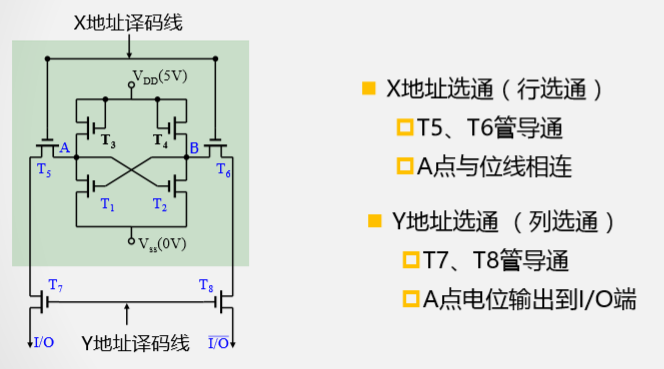

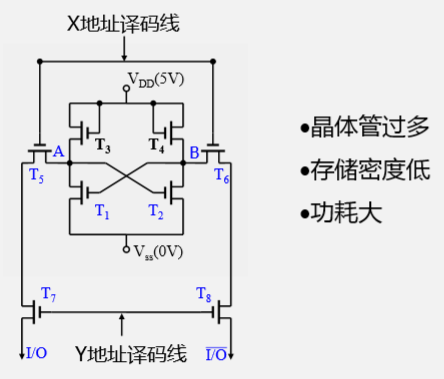

1.SRAM存储单元结构

2.SRAM存储单元工作原理

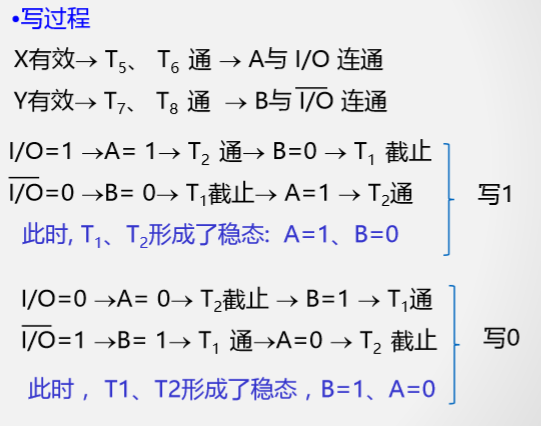

写过程

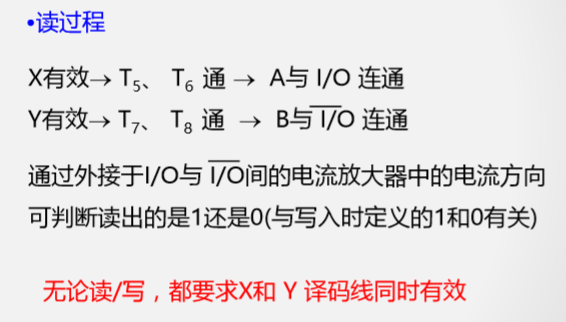

读过程

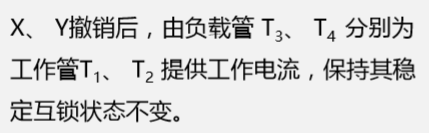

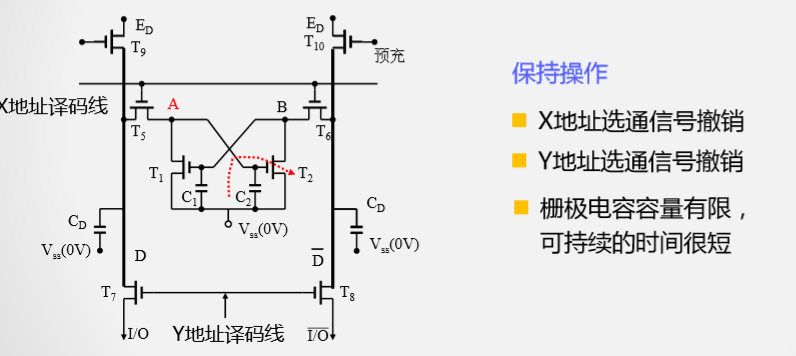

保持

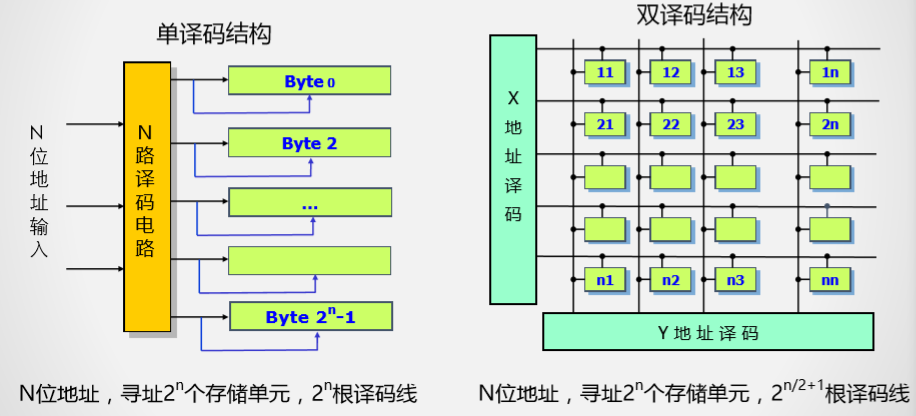

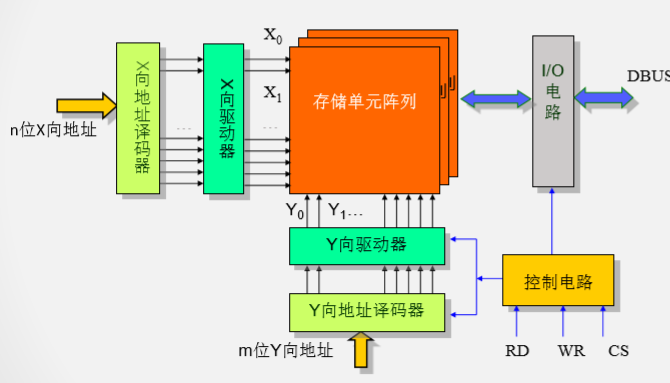

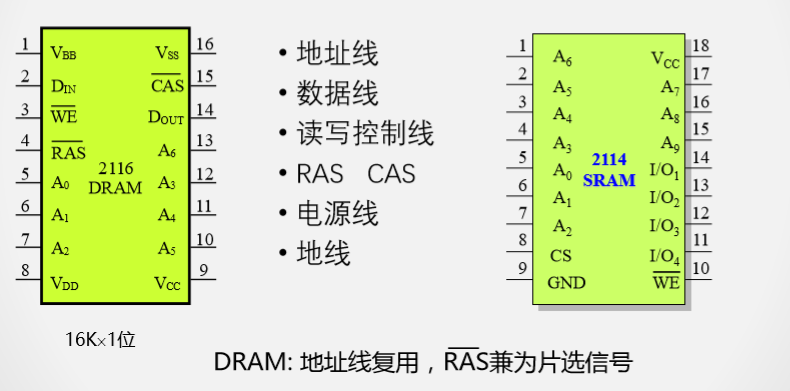

3.静态存储器的结构

静态存储器分为单译码结构和双译码结构

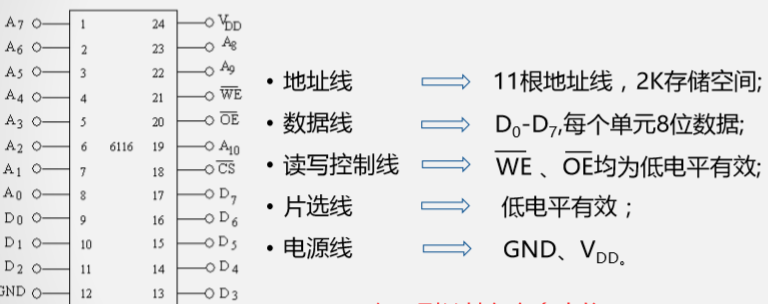

6116静态存储器结构

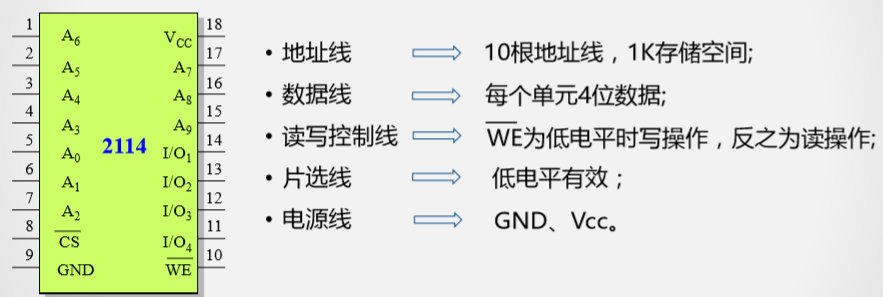

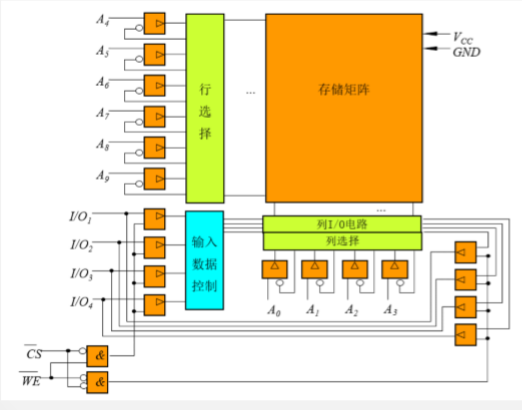

2114静态存储器结构

4.4 动态存储器工作原理

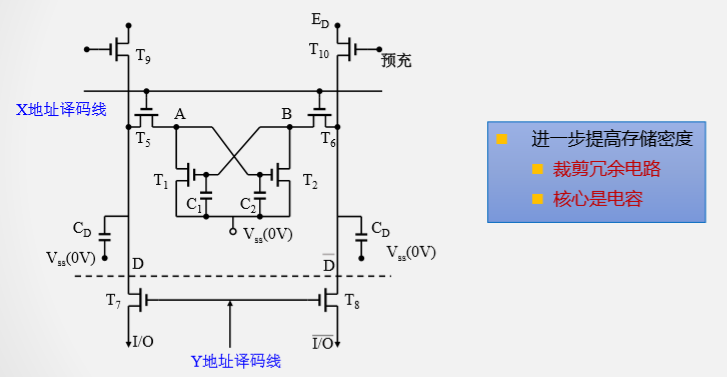

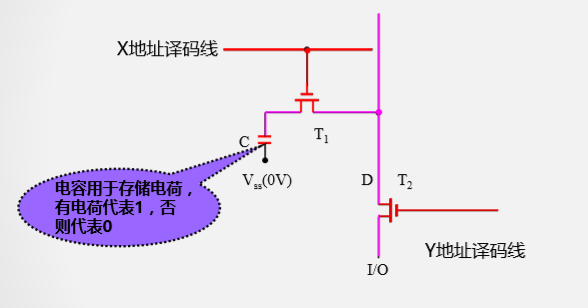

1.SRAM存储单元的不足

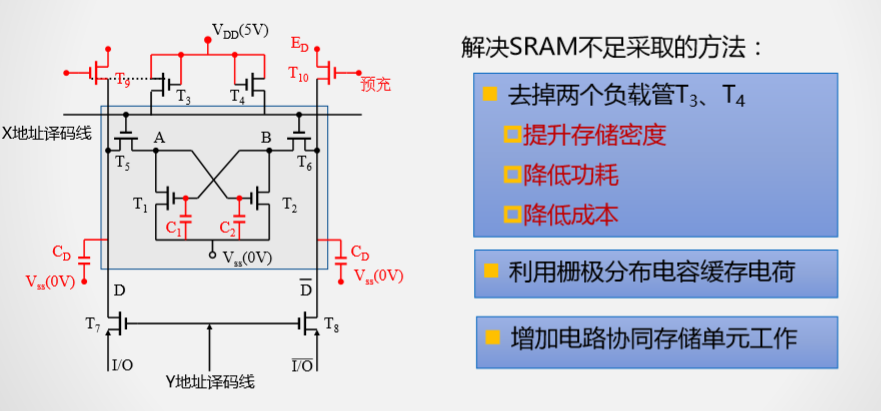

2.DRAM存储单元的基本结构

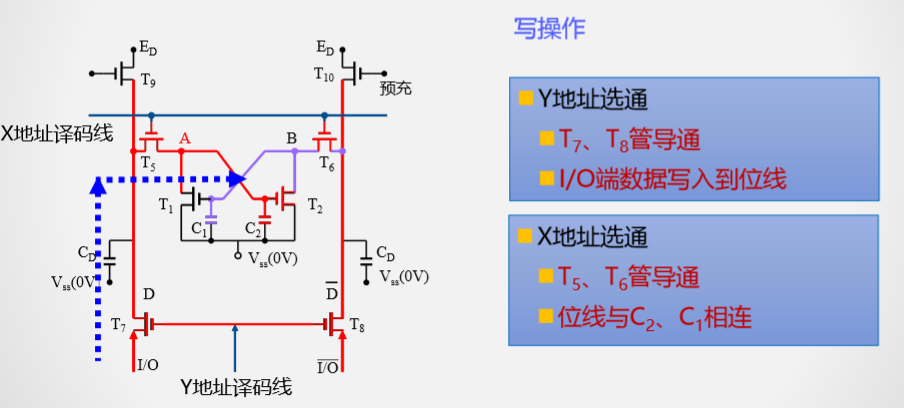

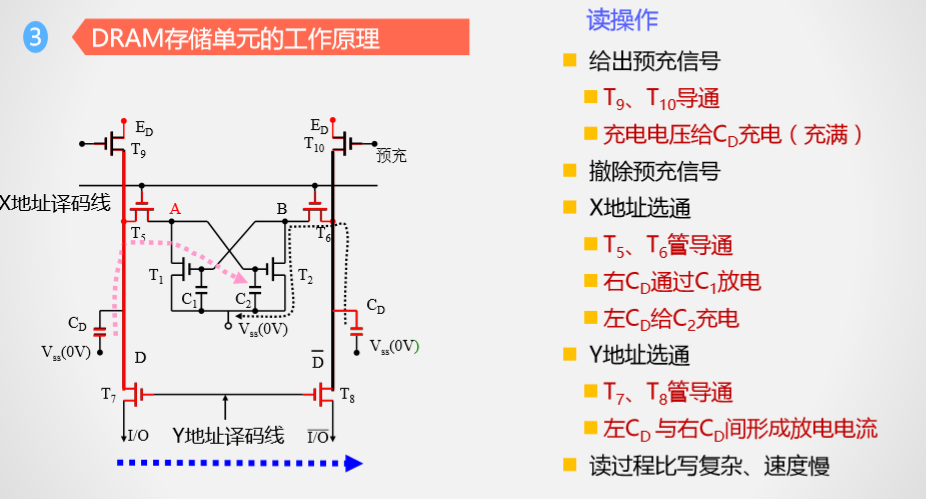

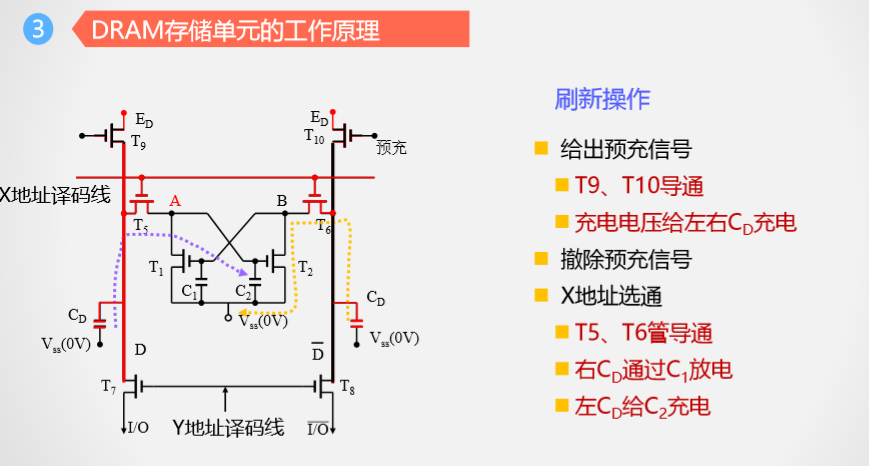

3.DRAM存储单元的工作原理

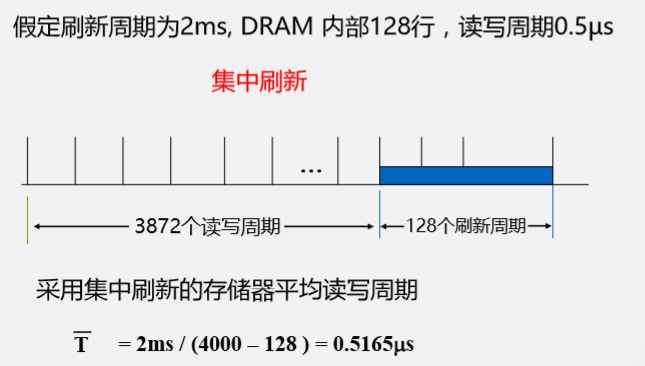

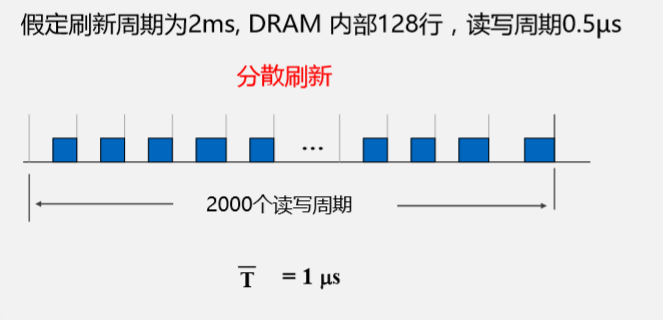

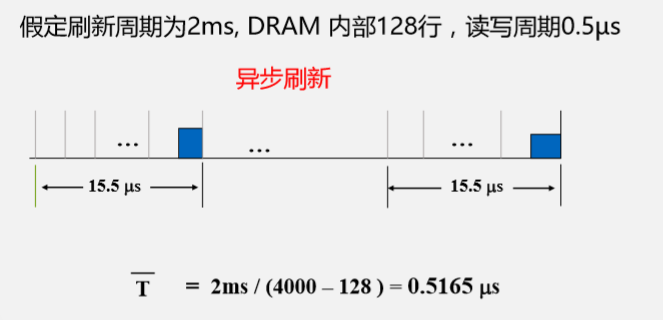

4.DRAM存储单元的刷新

- 刷新周期:两次刷新之间的时间间隔;

- 双译码结构的DRAM刷新按行进行,需要知道RDAM芯片存储矩阵的行数;

- 刷新地址由刷新地址计数器给出

5.DRAM与SRAM的对比

6.其他结构的DRAM存储单元

4.5 存储扩展

1.存储扩展的基本概念及类型

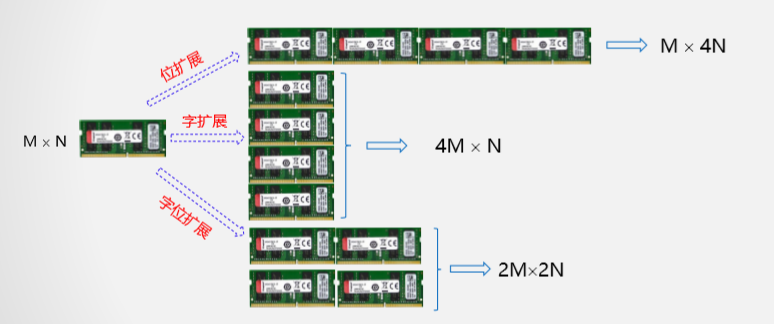

存储扩展包括 位扩展、字扩展、字位扩展,无论哪种类型的存储扩展都要完成CPU与主存间地址线、数据线、控制线的连接

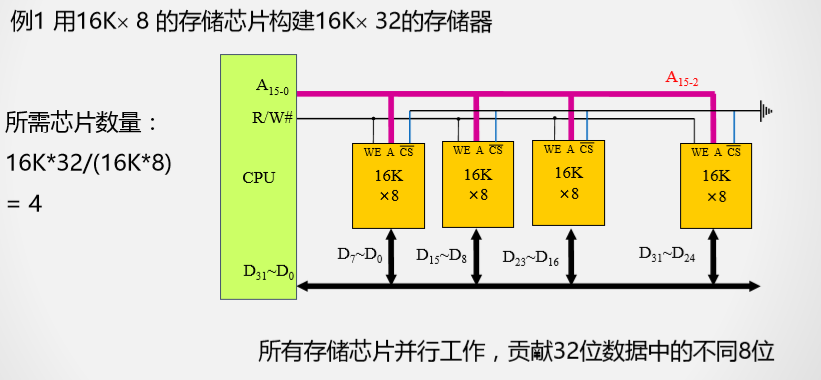

2.位扩展举例

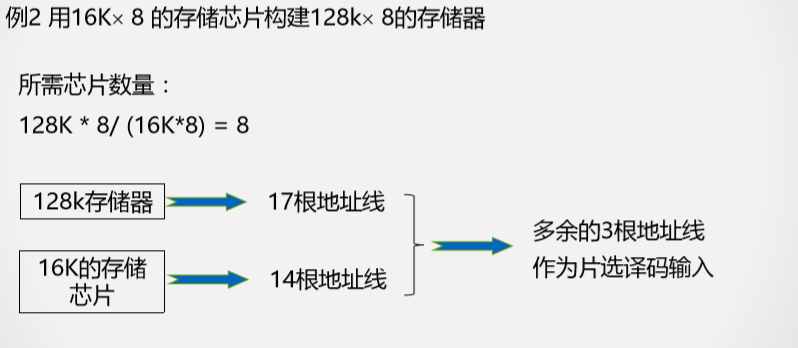

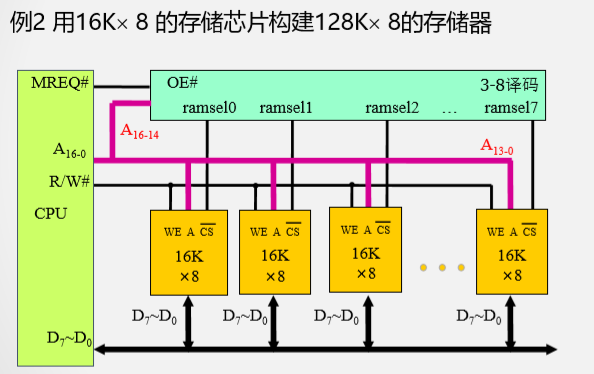

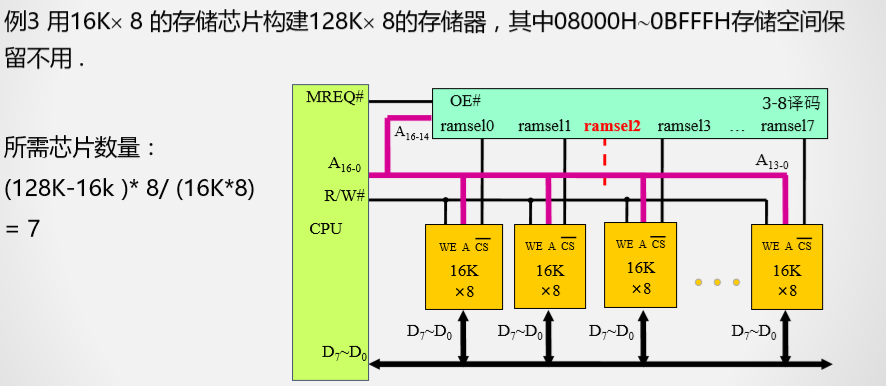

3.字扩展举例

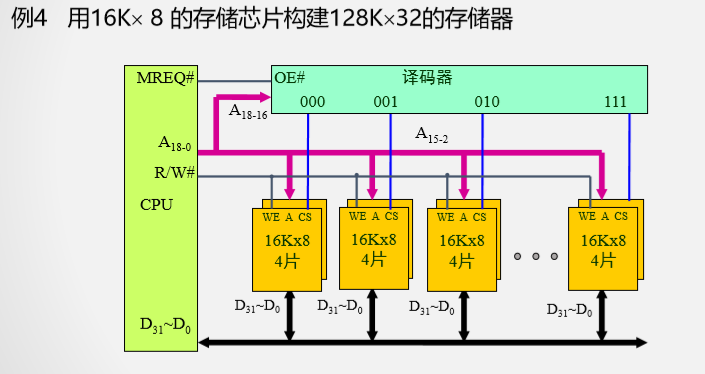

4.字位同时扩展

最后

以上就是迷你自行车最近收集整理的关于计算机组成原理 第四章 存储系统(1)的全部内容,更多相关计算机组成原理内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复