计算机系统基础之主存储器组织

- 基本术语

- 存储字长

- 数据存储与边界的关系

- 存储器分类

- 依据不同的特性有多种分类方法

- (1)按工作性质/存取方式分类

- (2)按存储介质分类

- (3)按信息的可更改性分类

- (4)按断电后信息的可保存性分类

- (5)按功能/容量/速度/所在位置分类

- 计算机结构中存储器作用

- 高速缓存(Cache)的组成

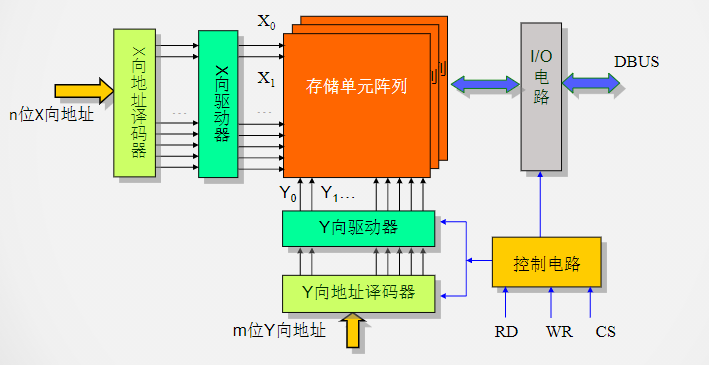

- 静态存储器工作原理

- SRAM存储单元结构

- 静态存储器分为单译码结构和双译码结构

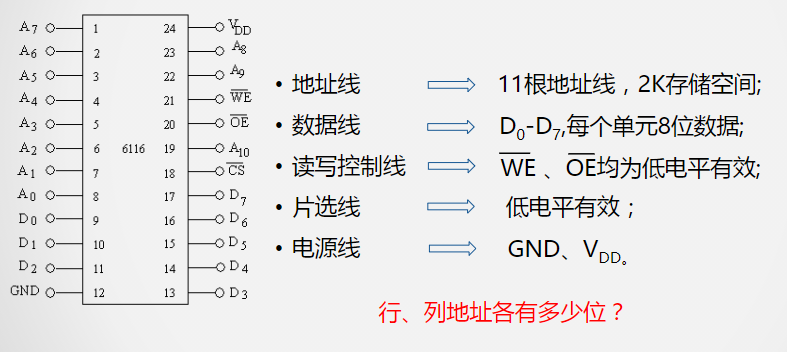

- 6116静态存储器结构

- 主存与Cache的地址映射

- 全相联 (fully-associated)

- 组相联 (set-associated)

- 主存的结构

- DRAM存储单元的刷新

- PC机主存储器的物理结构

基本术语

- 记忆单元 (存储基元 / 存储元 / 位元) (Cell)

- 具有两种稳态的能够表示二进制数码0和1的物理器件

- 存储单元 / 编址单位(Addressing Unit)

- 具有相同地址的位构成一个存储单元,也称为一个编址单位

- 存储体/ 存储矩阵 / 存储阵列(Bank)

- 所有存储单元构成一个存储阵列

- 编址方式(Addressing Mode)

- 字节编址、按字编址

- 存储器地址寄存器(Memory Address Register - MAR)

- 用于存放主存单元地址的寄存器

- 存储器数据寄存器( Memory Data Register-MDR (或MBR) )

- 用于存放主存单元中的数据的寄存器

存储字长

主存的一个存储单元所包含的二进制位数;

目前大多数计算机的主存按字节编址,存储字长也不断加大,如16位字长、32位字长和64位字长;

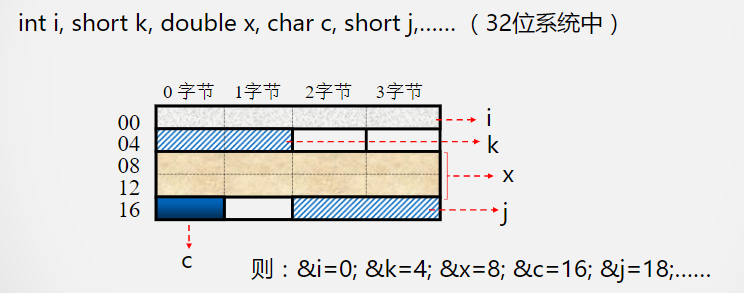

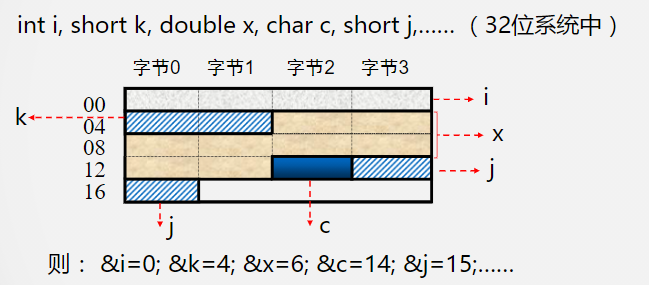

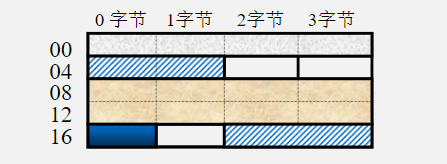

数据存储与边界的关系

- 按边界对齐的数据存储

- 按边界对齐的数据存储

注:虽节省了空间,但增加了访存次数! 需要在性能与容量间权衡! - 边界对齐与存储地址的关系(以32位为例)

- 双字长数据边界对齐的起始地址的最末三位为000(8字节整数倍;

- 单字长边界对齐的起始地址的末二位为00(4字节整数倍) ;

- 半字长边界对齐的起始地址的最末一位为0( 2字节整数倍)。

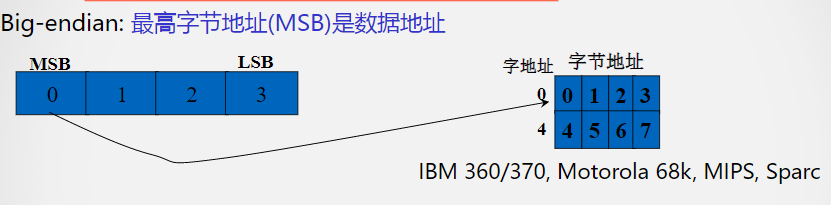

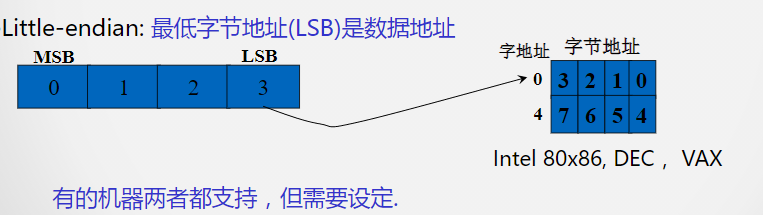

- 大端与小端存储方式

- Big-endian:最高字节地址(MSB)是数据地址。即高字节对应低地址,低字节对应高地址

- Little-endian:最低字节地址(LSB)是数据地址。即低字节对应低地址,高字节对应高地址

存储器分类

依据不同的特性有多种分类方法

(1)按工作性质/存取方式分类

- 随机存取存储器 Random Access Memory (RAM)

- 每个单元读写时间一样,且与各单元所在位置无关。如:内存

- 顺序存取存储器 Sequential Access Memory (SAM)

- 数据按顺序从存储载体的始端读出或写入,因而存取时间的长短与

信息所在位置有关。例如:磁带。

- 数据按顺序从存储载体的始端读出或写入,因而存取时间的长短与

- 直接存取存储器 Direct Access Memory(DAM)

- 直接定位到读写数据块,在读写数据块时按顺序进行。如磁盘。

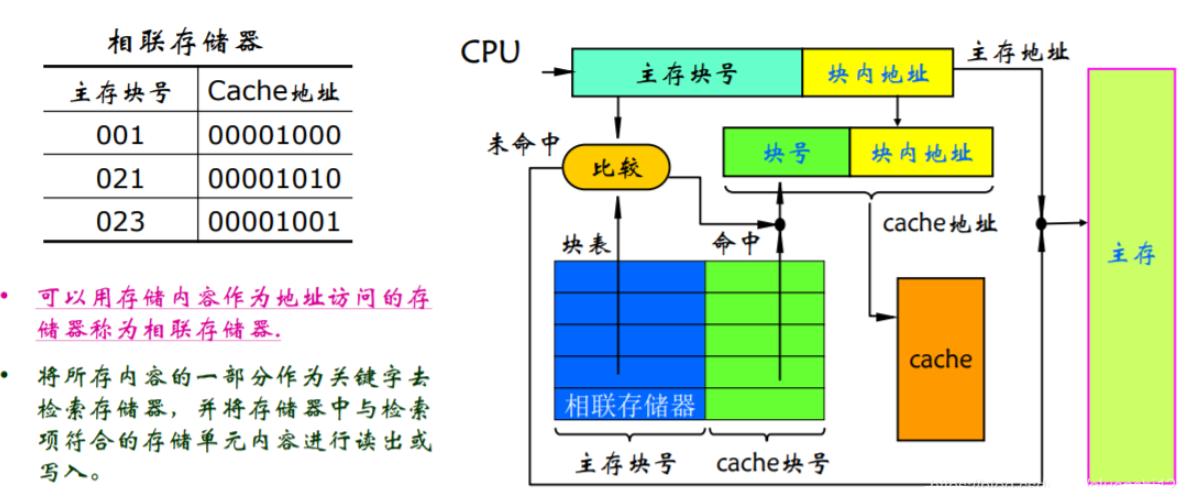

- 相联存储器 Associate Memory(AM)Content Addressed Memory (CAM)

- 按内容检索到存储位置进行读写。例如:快表。

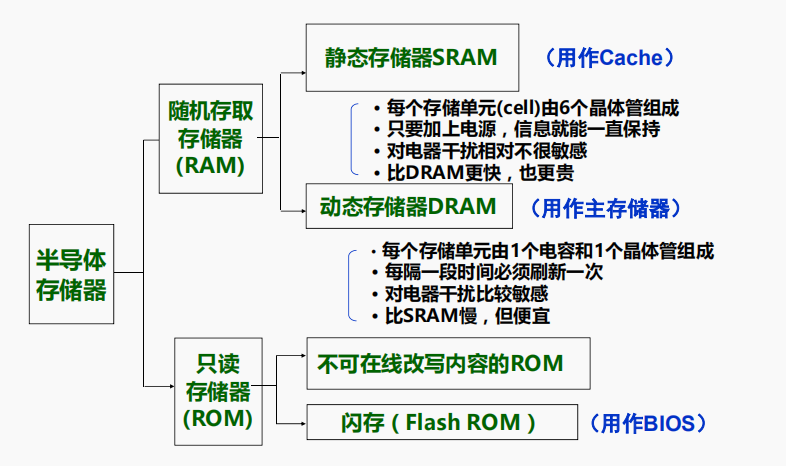

(2)按存储介质分类

- 半导体存储器:双极型,静态MOS型,动态MOS型

- 磁表面存储器:磁盘(Disk)、磁带 (Tape)

- 光存储器:CD,CD-ROM,DVD

(3)按信息的可更改性分类

- 读写存储器(Read / Write Memory):可读可写

- 只读存储器(Read Only Memory):只能读不能写

(4)按断电后信息的可保存性分类

- 非易失(不挥发)性存储器(Nonvolatile Memory) .信息可一直保留, 不需电源维持。

(如 :ROM、磁表面存储器、光存储器等) - 易失(挥发)性存储器(Volatile Memory).电源关闭时信息自动丢失。(如:RAM、Cache等)

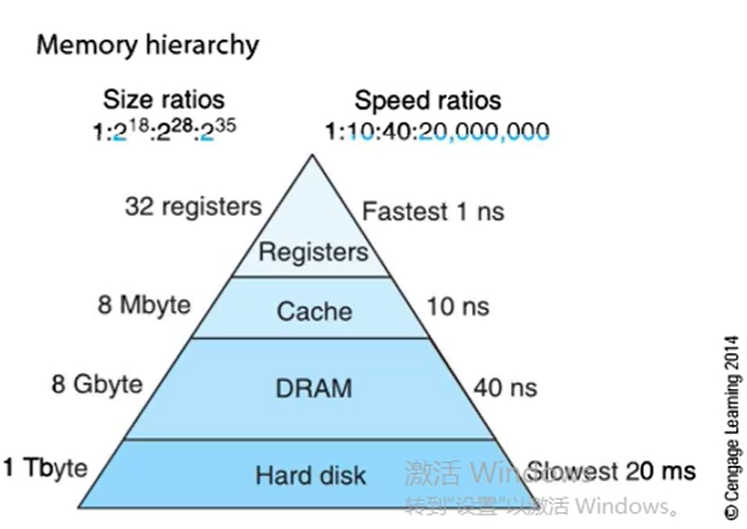

(5)按功能/容量/速度/所在位置分类

- 寄存器(Register)

- 封装在CPU内,用于存放当前正在执行的指令和使用的数据

- 用触发器实现,速度快,容量小(几~几十个)

- 高速缓存(Cache)

- 位于CPU内部或附近,用来存放当前要执行的局部程序段和数据

- 用SRAM实现,速度可与CPU匹配,容量小(几MB)

- 内存储器MM(主存储器Main (Primary) Memory)

- 位于CPU之外,用来存放已被启动的程序及所用的数据

- 用DRAM实现,速度较快,容量较大(几GB)

- 外存储器AM (辅助存储器Auxiliary / Secondary Storage)

- 位于主机之外,用来存放暂不运行的程序、数据或存档文件

- 用磁盘、SSD等实现,容量大而速度慢

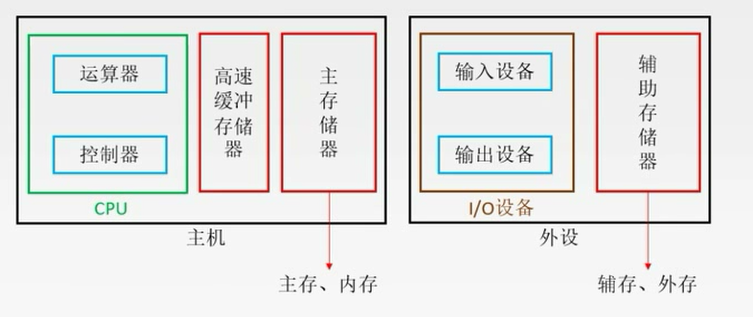

计算机结构中存储器作用

如图可知,在CPU中存储器主要是寄存器;在CPU和主存储器之间有高速缓存(Cache);而主存储是内存是用DRAM实现,速度较快,容量较大。由于内存速度跟不上CPU的高速而使其等待,从而浪费了CPU的宝贵时间。在CPU与内存之间增加高速缓冲存储器后,CPU能直接对其存取数据,从而减少了时间,提高了系统的运行速度。在外设装置中外存储器,用磁盘、SSD等实现,容量大可以达到1T及以上而速度相对就越慢。

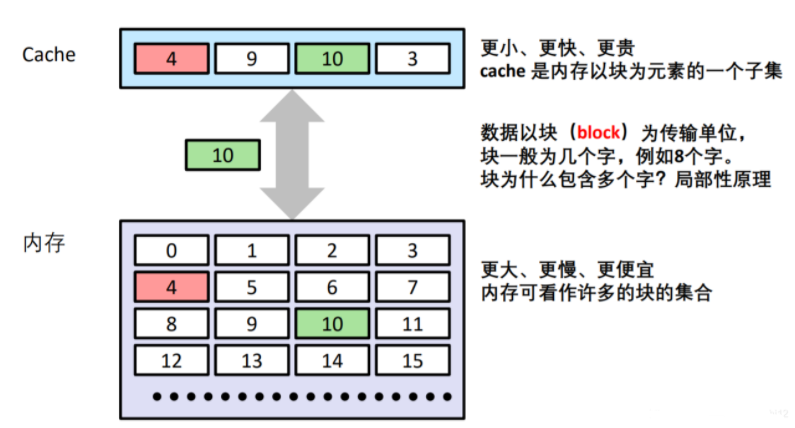

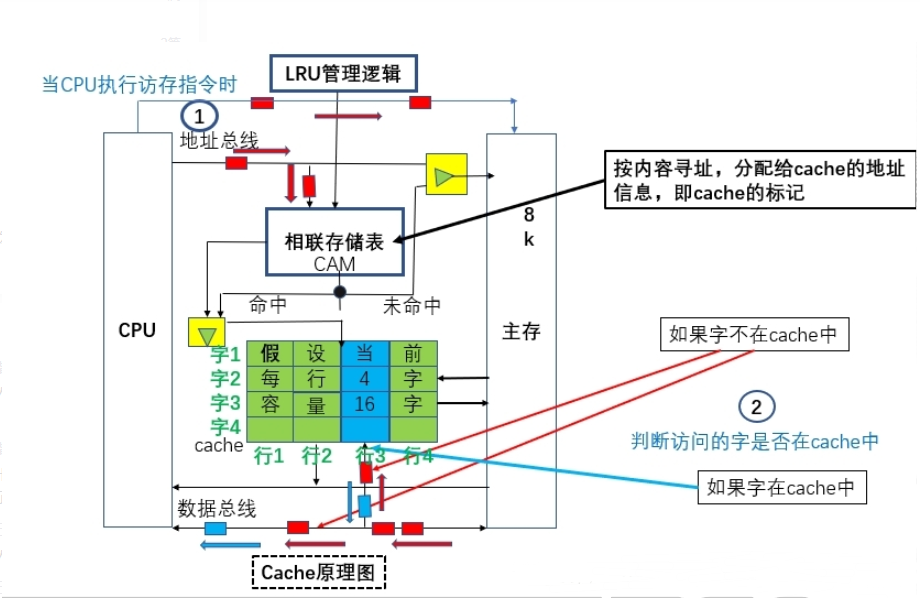

高速缓存(Cache)的组成

cache的组成:SRAM和控制逻辑。如果cache在CPU芯片外,它的控制逻辑一般和主存控制逻辑合成在一起,称主存/cache控制器。若cache在CPU内,则由CPU提供它的控制逻辑。

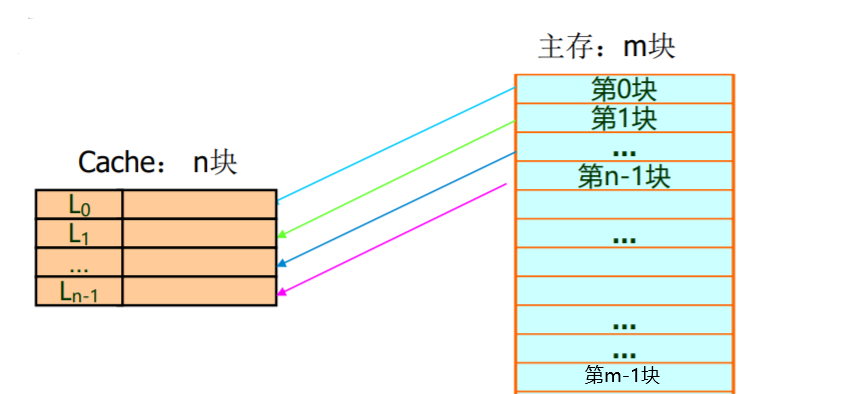

CPU与cache之间的数据交换是以字为单位,而cache与主存之间的数据交换是以块为单位。一个块由若干字组成,是定长的。这一块一块的数据被称为 CPU Line(缓存行),所以 CPU Line 是 CPU 从内存读取数据到 Cache 的单位。

静态存储器工作原理

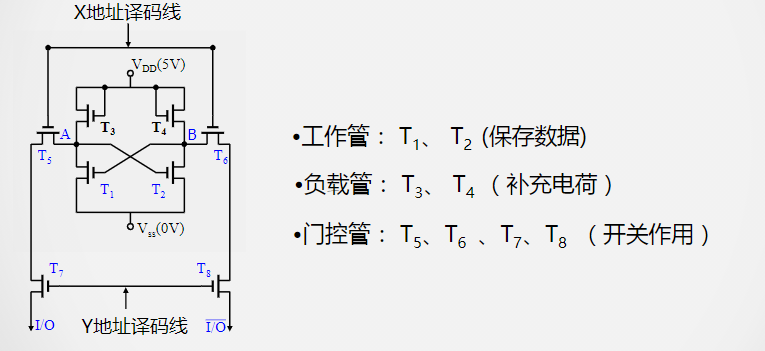

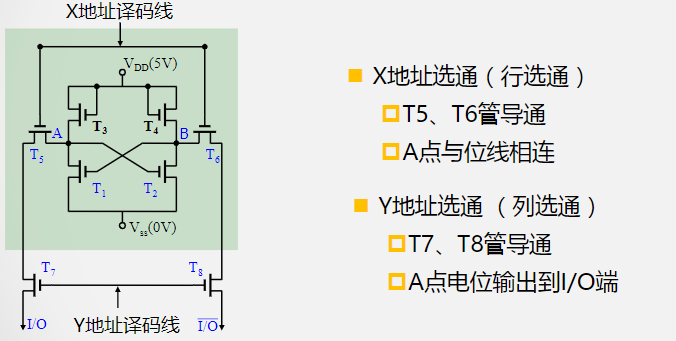

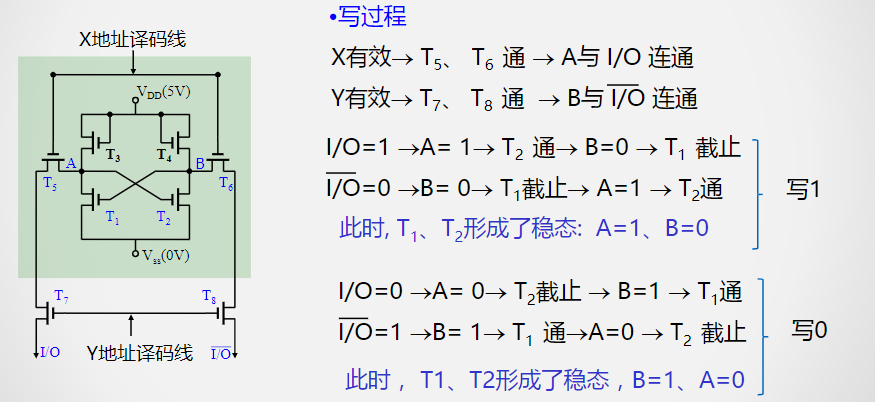

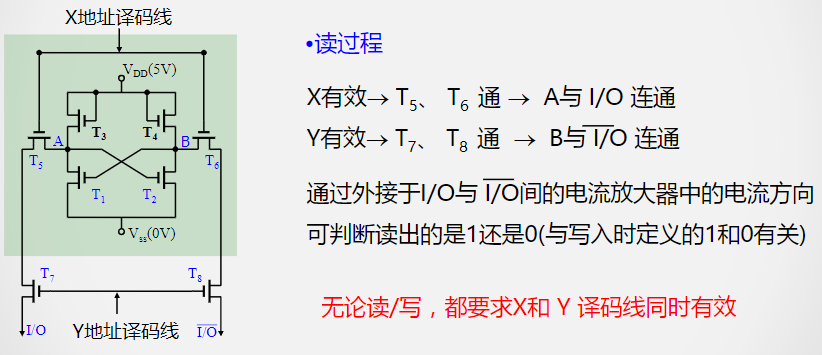

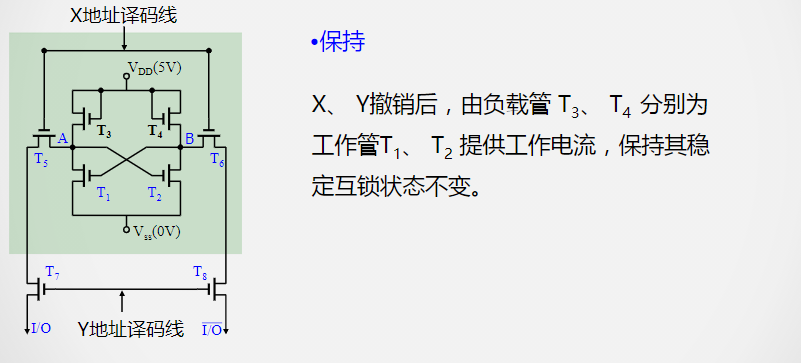

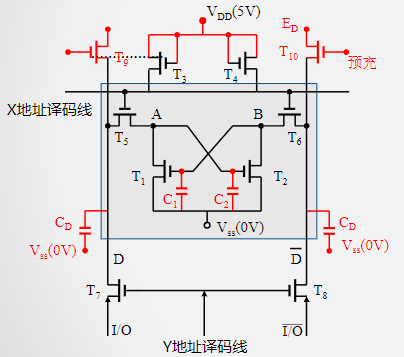

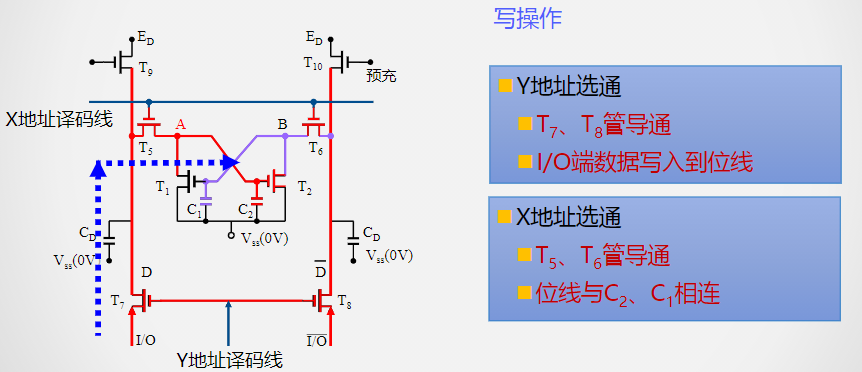

SRAM存储单元结构

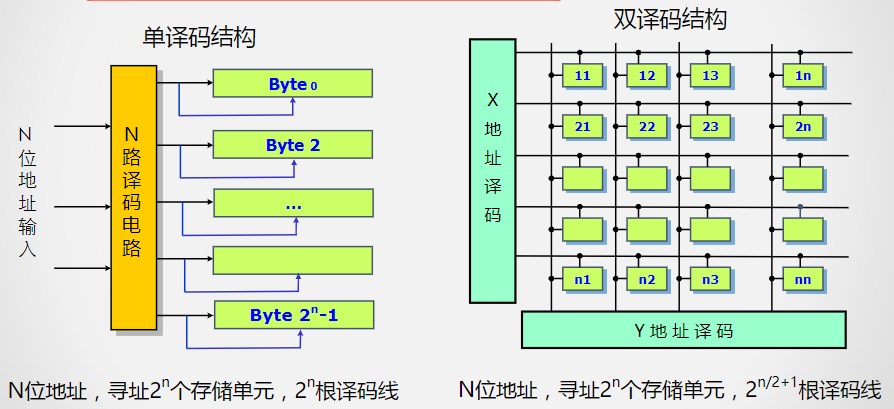

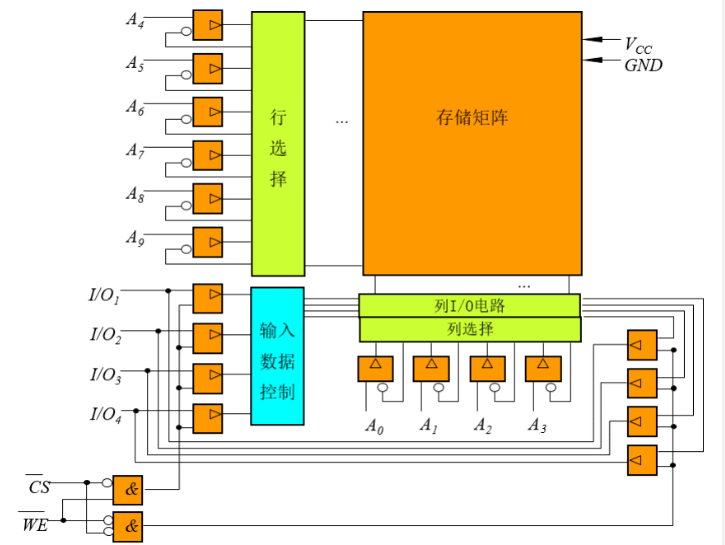

静态存储器分为单译码结构和双译码结构

6116静态存储器结构

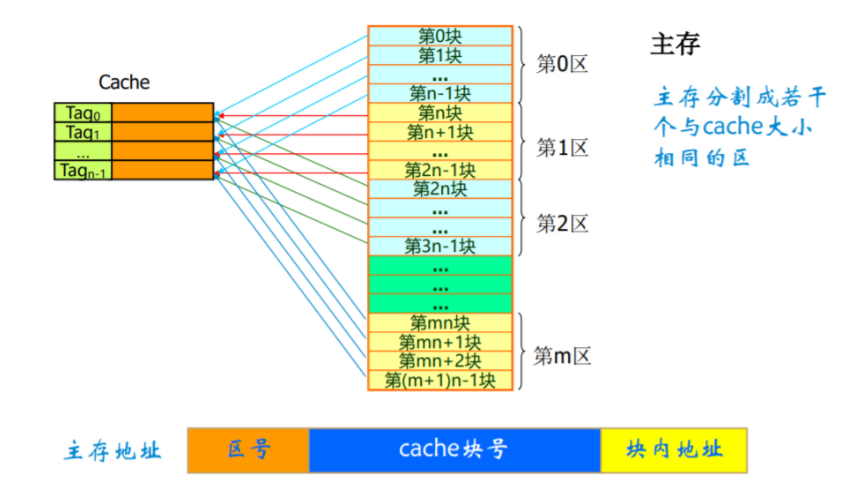

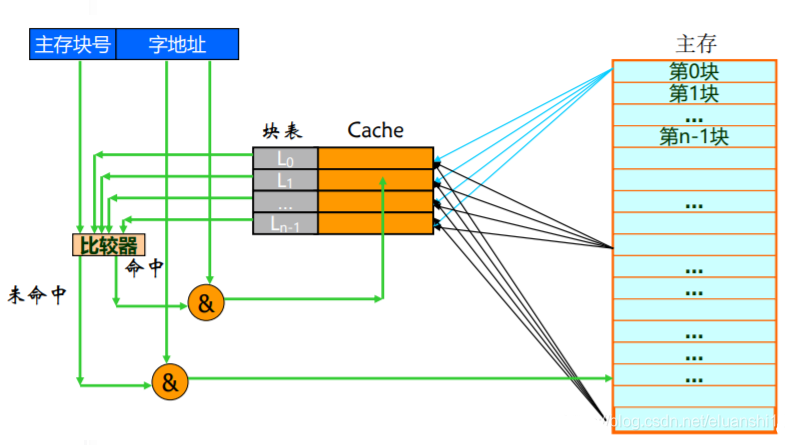

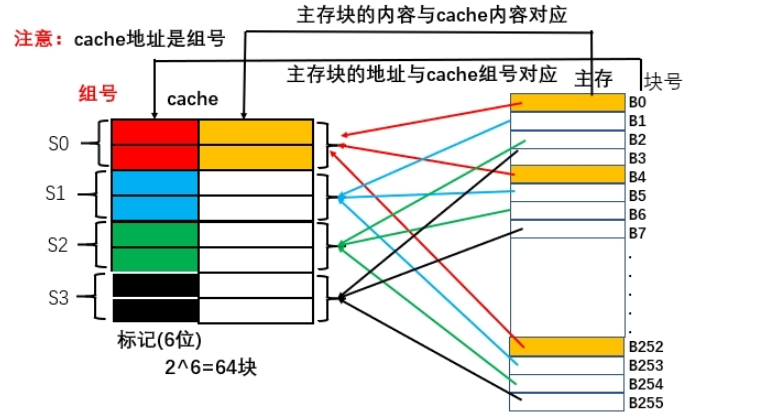

主存与Cache的地址映射

地址映射:利用某种方法或者规则将主存块定位到cache

优点

▪ 地址变换速度快,一对一映射

▪ 替换算法简单、容易实现

缺点

▪ 容易冲突,cache利用率低

▪ 命中率低

全相联 (fully-associated)

主存中任何一块均可定位于Cache中的任意一块,可提高命中率,但是硬件开销增加

优点

▪ 一对多映射

▪ cache全部装满后才会出现块冲突

▪ 块冲突的概率低,cache利用率高

缺点

▪ 相应的替换算法复杂

组相联 (set-associated)

略

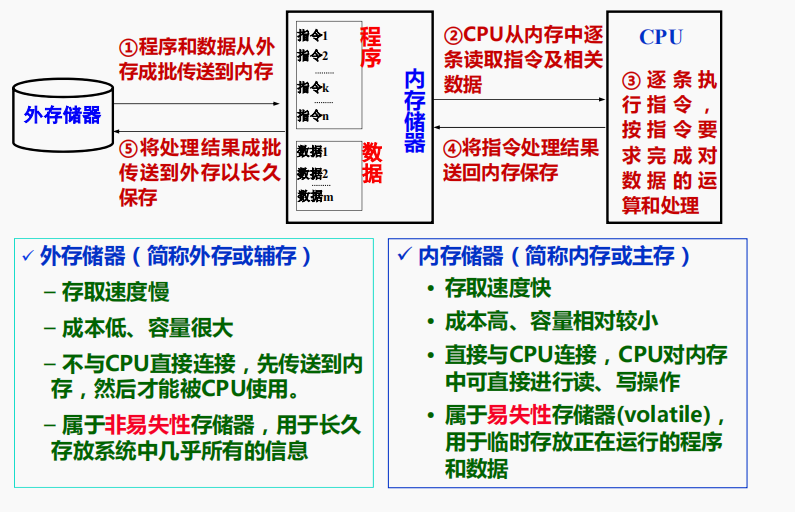

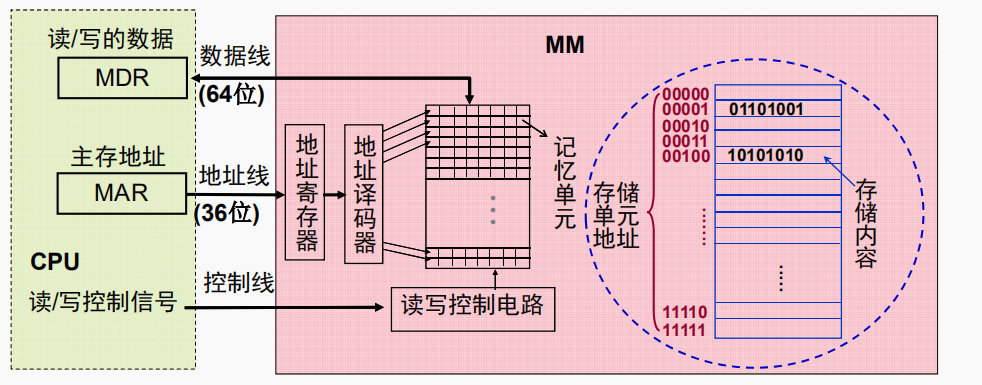

主存的结构

主存中存放的是指令及其数据的信息。而CPU执行指令时需要取指令、取数据、存数据,这些都需要访问主存。如下图:

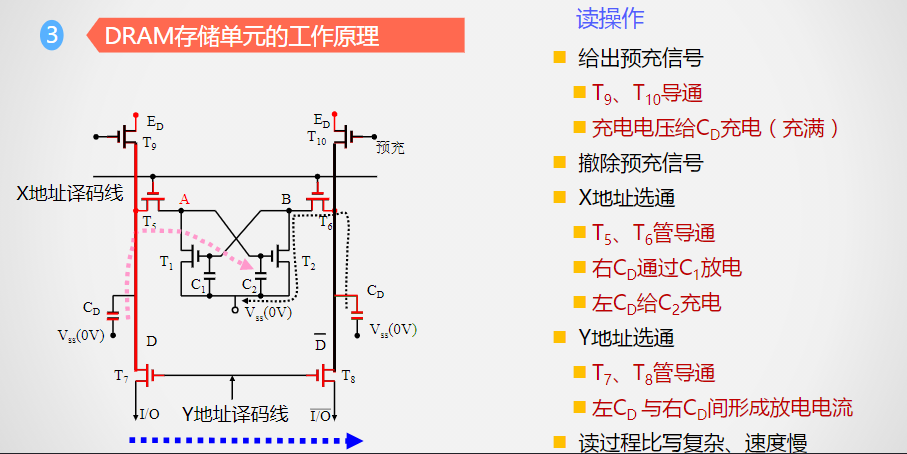

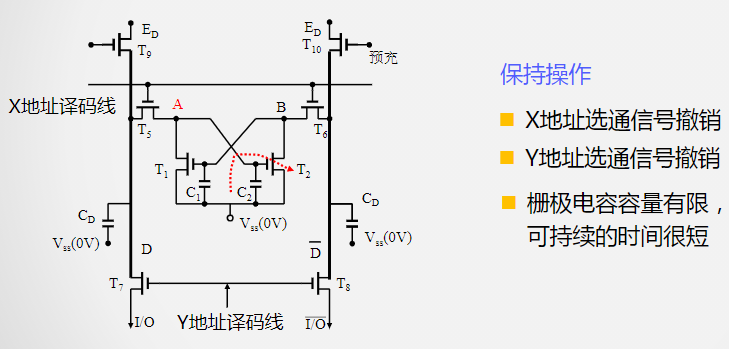

解决SRAM不足采取的方法:

- 去掉两个负载管T3、T4

1.提升存储密度

2.降低功耗

3.降低成本 - 利用栅极分布电容缓存电荷

- 增加电路协同存储单元工作

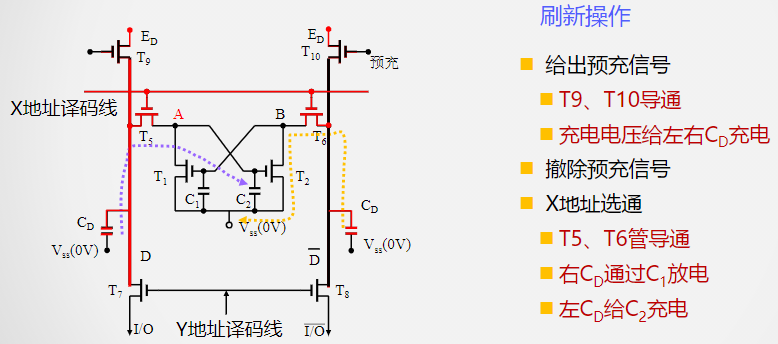

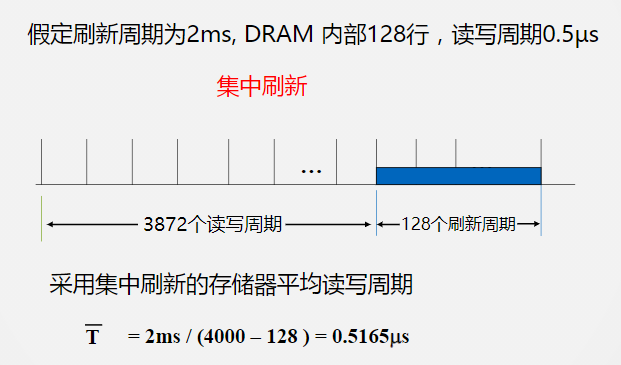

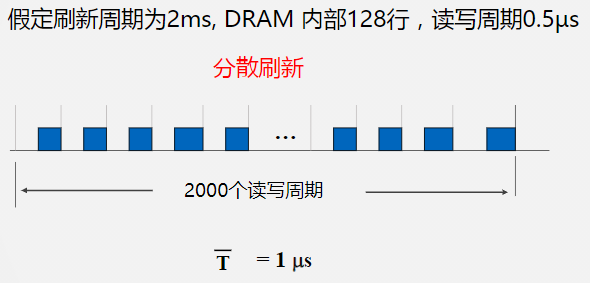

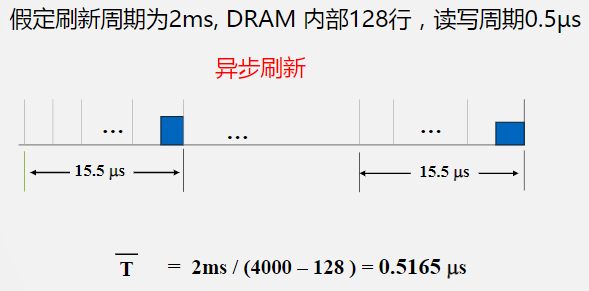

DRAM存储单元的刷新

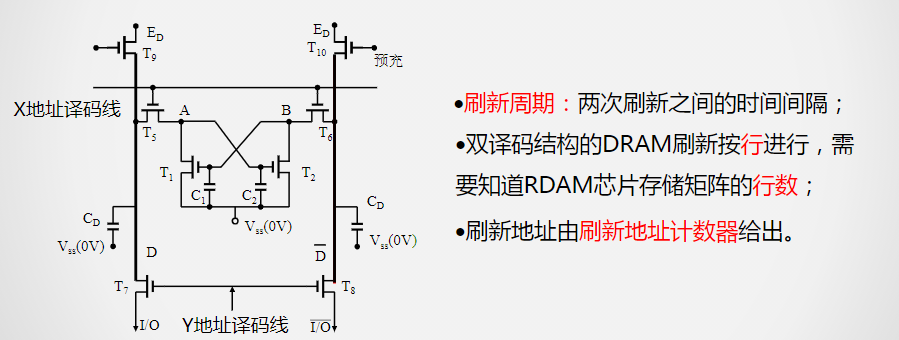

DRAM的一个重要特点是,数据以电荷的形式保存在电容中,电容的放电使得电荷通常只能维持几十个毫秒左右,相当于1M个时钟周期左右,因此要定期进行刷新(读出后重新写回),按行进行(所有芯片中的同一行一起进行),刷新操作所需时间通常只占1%~2%左右。双译码结构的DRAM刷新按行进行,需要知道RDAM芯片存储矩阵的行数;刷新地址由刷新地址计数器给出.

举例:典型的16M位DRAM(4Mx4)

16M位 = 4Mbx4 = 2048x2048x4 = 211x211x4

(1) 地址线:11根线分时复用,由RAS和CAS提供控制时序

(2) 需4个位平面,对相同行、列交叉点的4位一起读/写

行地址和列地址分时复用, 每出现新一代DRAM芯片,至少要增加一根地址线。每加一根地址线,则行地址和列地址各增加一位,所以行数和列数各增加一倍。因而容量至少提高到4倍。

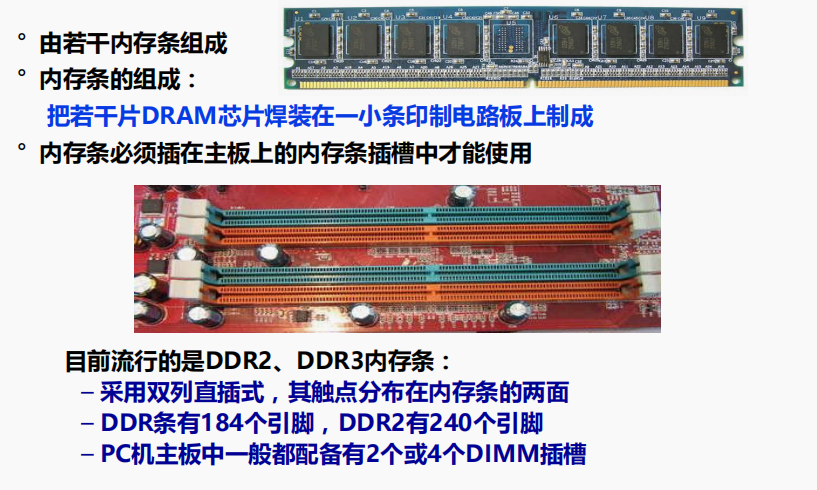

PC机主存储器的物理结构

最后

以上就是大胆花瓣最近收集整理的关于计算机系统基础(四)之存储器基本术语存储字长存储器分类计算机结构中存储器作用高速缓存(Cache)的组成主存的结构的全部内容,更多相关计算机系统基础(四)之存储器基本术语存储字长存储器分类计算机结构中存储器作用高速缓存(Cache)内容请搜索靠谱客的其他文章。

发表评论 取消回复