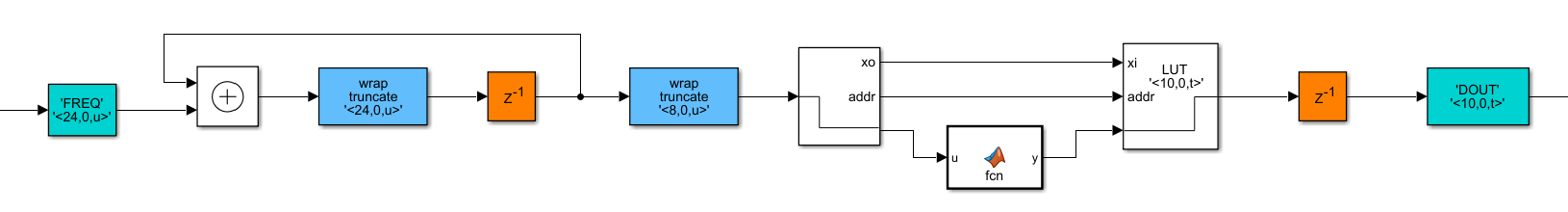

模型设计

先看一下DDS的模型设计。

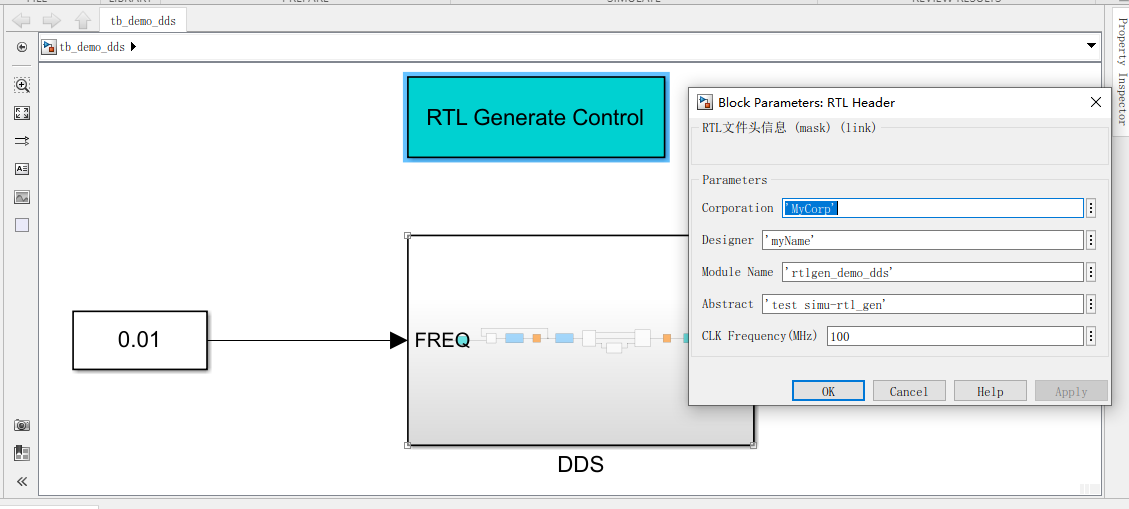

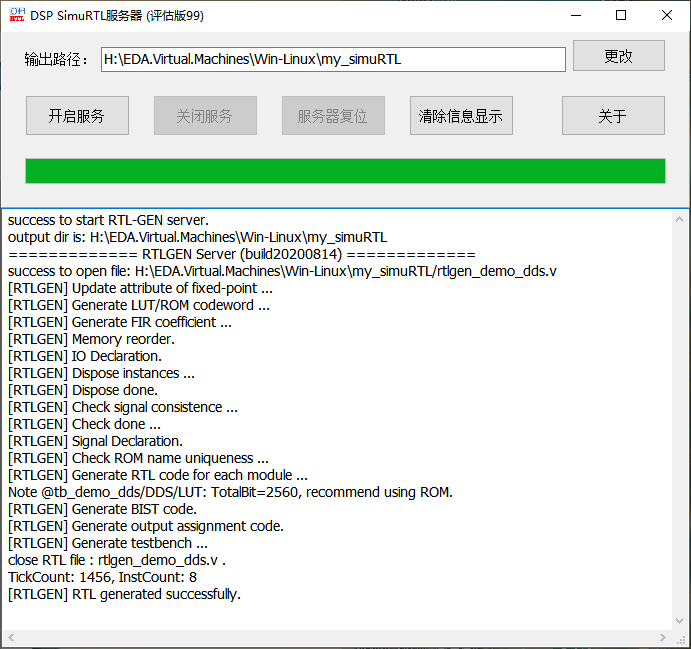

生成RTL代码

简单3个步骤就可以自动生成RTL代码。

1)模型设计的顶层放置一个代码生成控制器,设置RTL代码的模块名称和一些文件头信息,时钟频率将用于自动生成的DC综合脚本。

2)开启RTL代码生成服务器

3)运行一次Simulink仿真

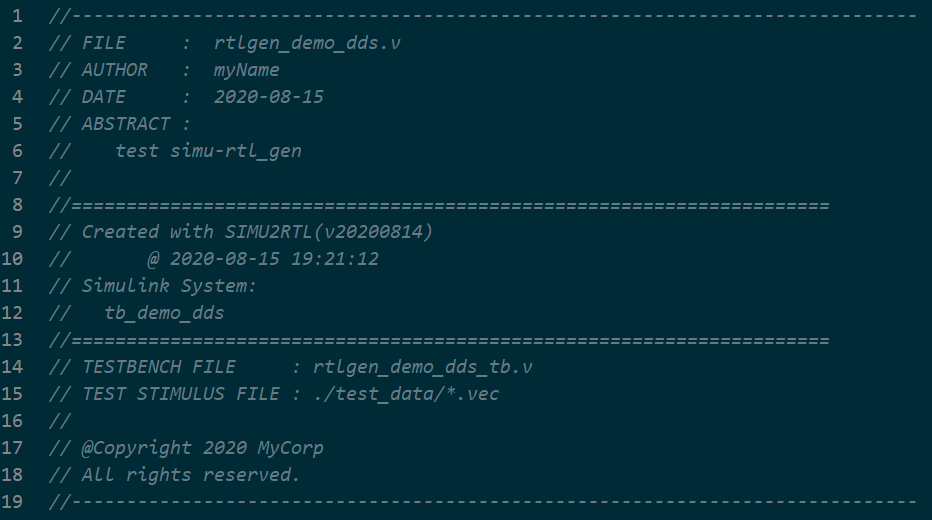

RTL代码解析

1)文件头

与模型设计中的RTL Generate Control的参数设置对应。

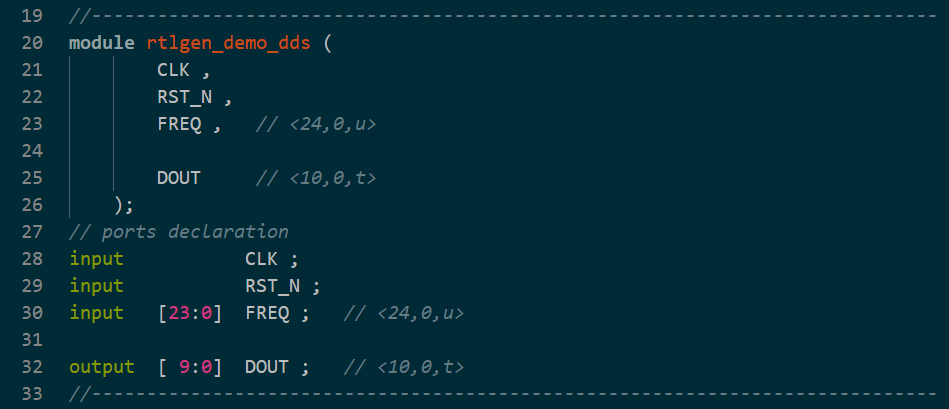

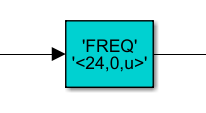

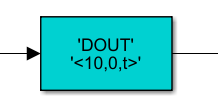

2)模块声明和端口声明

与输入端口模型和输出端口模型对应:

CLK和RST_N是数字电路两个必要的信号,隐含在模型设计的基于节拍的仿真方式中。

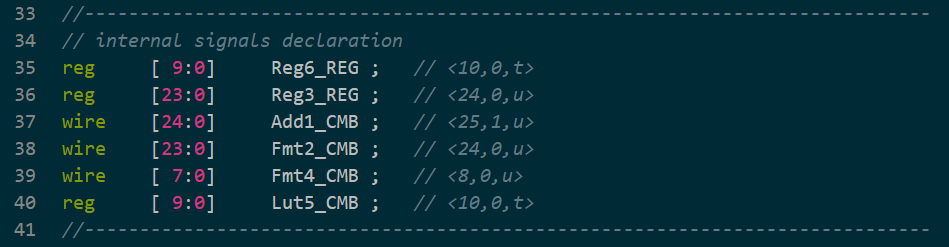

3)每个模型对应的输出信号的声明

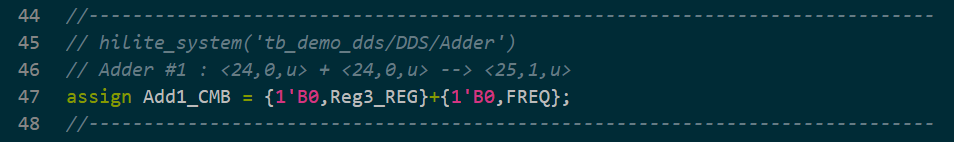

4)加法器

对应模型:

加法器的两个输入,一个来自输入端口FREQ,一个来自寄存器Reg3_REG。

加法器遵循“无精度损失”原则,输出位宽相对输入位宽会有所增加。

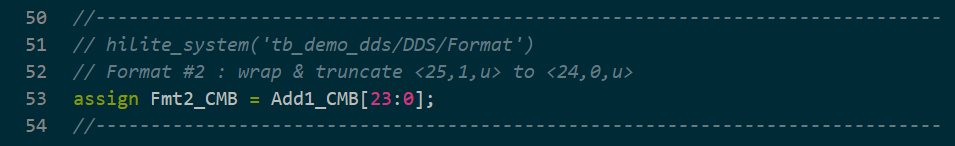

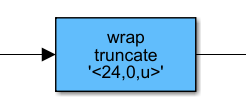

5)定点化处理器

对应模型:

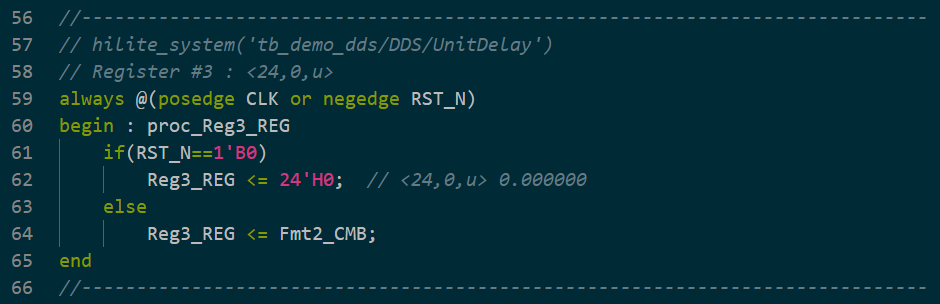

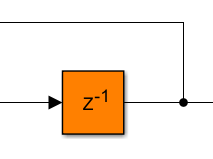

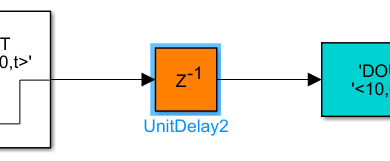

6) 单元延时器(寄存器)

对应模型:

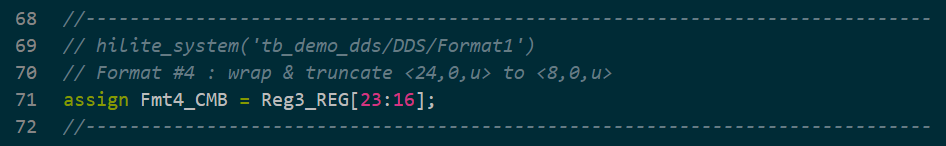

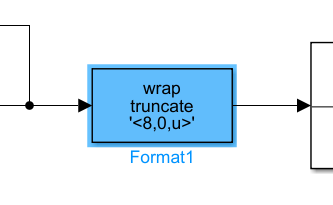

7)LUT前的定点化处理器

对应模型:

LUT的地址空间大小由输入信号的位宽决定,需要用定点化处理模型限制位宽,降低LUT的电路规模。

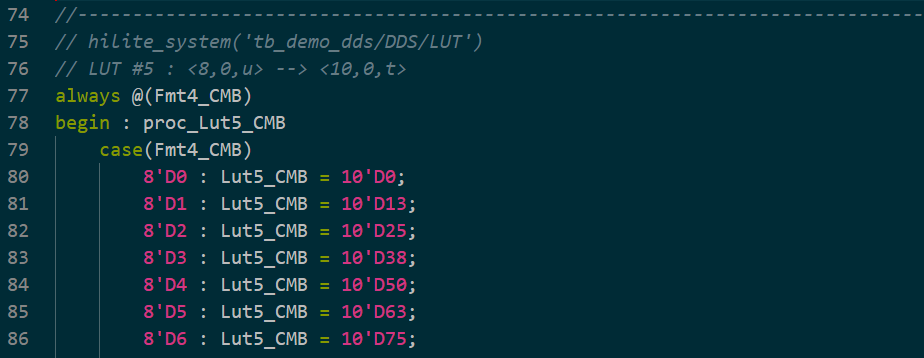

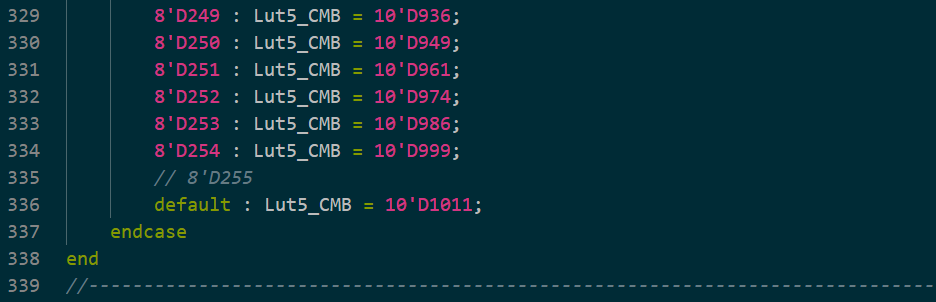

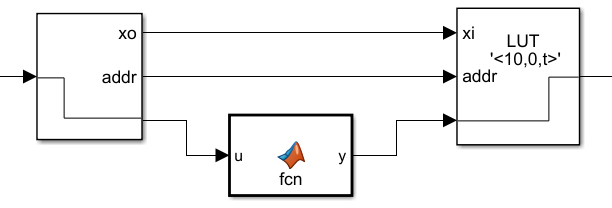

8)LUT,存储正弦波数据

对应模型:

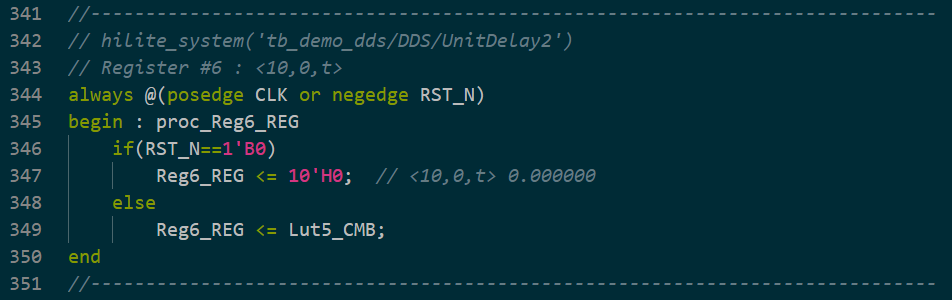

9)输出级寄存器

对应模型:

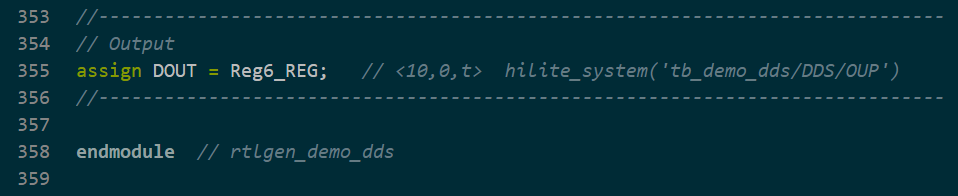

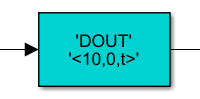

10)输出赋值与模块结束

对应模型:

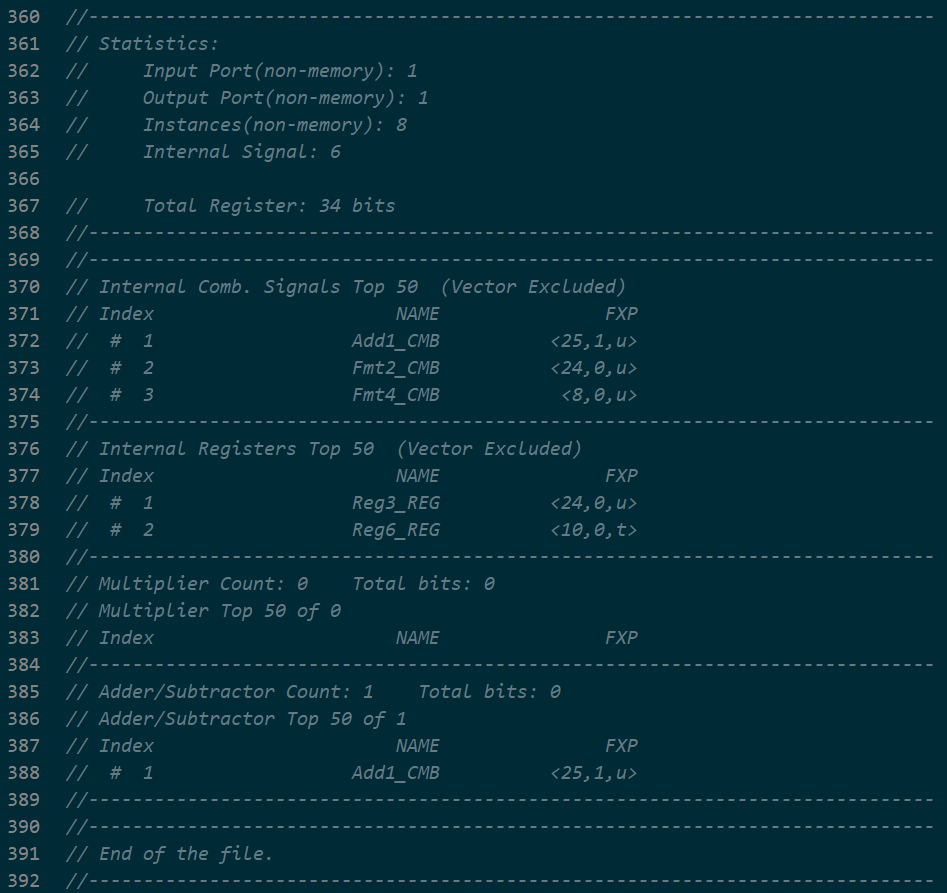

11)资源使用统计

对于位宽异常大的信号,需要检查确认是否符合设计预期。

完整verilog代码

//-----------------------------------------------------------------------------

// FILE : rtlgen_demo_dds.v

// AUTHOR : myName

// DATE : 2020-08-15

// ABSTRACT :

// test simu-rtl_gen

//

//=====================================================================

// Created with SIMU2RTL(v20200814)

// @ 2020-08-15 19:21:12

// Simulink System:

// tb_demo_dds

//=====================================================================

// TESTBENCH FILE : rtlgen_demo_dds_tb.v

// TEST STIMULUS FILE : ./test_data/*.vec

//

// @Copyright 2020 MyCorp

// All rights reserved.

//-----------------------------------------------------------------------------

module rtlgen_demo_dds (

CLK ,

RST_N ,

FREQ , // <24,0,u>

DOUT // <10,0,t>

);

// ports declaration

input CLK ;

input RST_N ;

input [23:0] FREQ ; // <24,0,u>

output [ 9:0] DOUT ; // <10,0,t>

//-----------------------------------------------------------------------------

// internal signals declaration

reg [ 9:0] Reg6_REG ; // <10,0,t>

reg [23:0] Reg3_REG ; // <24,0,u>

wire [24:0] Add1_CMB ; // <25,1,u>

wire [23:0] Fmt2_CMB ; // <24,0,u>

wire [ 7:0] Fmt4_CMB ; // <8,0,u>

reg [ 9:0] Lut5_CMB ; // <10,0,t>

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// hilite_system('tb_demo_dds/DDS/Adder')

// Adder #1 : <24,0,u> + <24,0,u> --> <25,1,u>

assign Add1_CMB = {1'B0,Reg3_REG}+{1'B0,FREQ};

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// hilite_system('tb_demo_dds/DDS/Format')

// Format #2 : wrap & truncate <25,1,u> to <24,0,u>

assign Fmt2_CMB = Add1_CMB[23:0];

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// hilite_system('tb_demo_dds/DDS/UnitDelay')

// Register #3 : <24,0,u>

always @(posedge CLK or negedge RST_N)

begin : proc_Reg3_REG

if(RST_N==1'B0)

Reg3_REG <= 24'H0; // <24,0,u> 0.000000

else

Reg3_REG <= Fmt2_CMB;

end

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// hilite_system('tb_demo_dds/DDS/Format1')

// Format #4 : wrap & truncate <24,0,u> to <8,0,u>

assign Fmt4_CMB = Reg3_REG[23:16];

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// hilite_system('tb_demo_dds/DDS/LUT')

// LUT #5 : <8,0,u> --> <10,0,t>

always @(Fmt4_CMB)

begin : proc_Lut5_CMB

case(Fmt4_CMB)

8'D0 : Lut5_CMB = 10'D0;

8'D1 : Lut5_CMB = 10'D13;

8'D2 : Lut5_CMB = 10'D25;

8'D3 : Lut5_CMB = 10'D38;

8'D4 : Lut5_CMB = 10'D50;

8'D5 : Lut5_CMB = 10'D63;

8'D6 : Lut5_CMB = 10'D75;

8'D7 : Lut5_CMB = 10'D88;

8'D8 : Lut5_CMB = 10'D100;

8'D9 : Lut5_CMB = 10'D112;

8'D10 : Lut5_CMB = 10'D124;

8'D11 : Lut5_CMB = 10'D137;

8'D12 : Lut5_CMB = 10'D149;

8'D13 : Lut5_CMB = 10'D161;

8'D14 : Lut5_CMB = 10'D172;

8'D15 : Lut5_CMB = 10'D184;

8'D16 : Lut5_CMB = 10'D196;

8'D17 : Lut5_CMB = 10'D207;

8'D18 : Lut5_CMB = 10'D219;

8'D19 : Lut5_CMB = 10'D230;

8'D20 : Lut5_CMB = 10'D241;

8'D21 : Lut5_CMB = 10'D252;

8'D22 : Lut5_CMB = 10'D263;

8'D23 : Lut5_CMB = 10'D274;

8'D24 : Lut5_CMB = 10'D284;

8'D25 : Lut5_CMB = 10'D295;

8'D26 : Lut5_CMB = 10'D305;

8'D27 : Lut5_CMB = 10'D315;

8'D28 : Lut5_CMB = 10'D325;

8'D29 : Lut5_CMB = 10'D334;

8'D30 : Lut5_CMB = 10'D344;

8'D31 : Lut5_CMB = 10'D353;

8'D32 : Lut5_CMB = 10'D362;

8'D33 : Lut5_CMB = 10'D371;

8'D34 : Lut5_CMB = 10'D379;

8'D35 : Lut5_CMB = 10'D388;

8'D36 : Lut5_CMB = 10'D396;

8'D37 : Lut5_CMB = 10'D404;

8'D38 : Lut5_CMB = 10'D411;

8'D39 : Lut5_CMB = 10'D419;

8'D40 : Lut5_CMB = 10'D426;

8'D41 : Lut5_CMB = 10'D433;

8'D42 : Lut5_CMB = 10'D439;

8'D43 : Lut5_CMB = 10'D445;

8'D44 : Lut5_CMB = 10'D452;

8'D45 : Lut5_CMB = 10'D457;

8'D46 : Lut5_CMB = 10'D463;

8'D47 : Lut5_CMB = 10'D468;

8'D48 : Lut5_CMB = 10'D473;

8'D49 : Lut5_CMB = 10'D478;

8'D50 : Lut5_CMB = 10'D482;

8'D51 : Lut5_CMB = 10'D486;

8'D52 : Lut5_CMB = 10'D490;

8'D53 : Lut5_CMB = 10'D493;

8'D54 : Lut5_CMB = 10'D497;

8'D55 : Lut5_CMB = 10'D500;

8'D56 : Lut5_CMB = 10'D502;

8'D57 : Lut5_CMB = 10'D504;

8'D58 : Lut5_CMB = 10'D506;

8'D59 : Lut5_CMB = 10'D508;

8'D60 : Lut5_CMB = 10'D510;

8'D61 : Lut5_CMB = 10'D511;

8'D62 : Lut5_CMB = 10'D511;

8'D63 : Lut5_CMB = 10'D511;

8'D64 : Lut5_CMB = 10'D511;

8'D65 : Lut5_CMB = 10'D511;

8'D66 : Lut5_CMB = 10'D511;

8'D67 : Lut5_CMB = 10'D511;

8'D68 : Lut5_CMB = 10'D510;

8'D69 : Lut5_CMB = 10'D508;

8'D70 : Lut5_CMB = 10'D506;

8'D71 : Lut5_CMB = 10'D504;

8'D72 : Lut5_CMB = 10'D502;

8'D73 : Lut5_CMB = 10'D500;

8'D74 : Lut5_CMB = 10'D497;

8'D75 : Lut5_CMB = 10'D493;

8'D76 : Lut5_CMB = 10'D490;

8'D77 : Lut5_CMB = 10'D486;

8'D78 : Lut5_CMB = 10'D482;

8'D79 : Lut5_CMB = 10'D478;

8'D80 : Lut5_CMB = 10'D473;

8'D81 : Lut5_CMB = 10'D468;

8'D82 : Lut5_CMB = 10'D463;

8'D83 : Lut5_CMB = 10'D457;

8'D84 : Lut5_CMB = 10'D452;

8'D85 : Lut5_CMB = 10'D445;

8'D86 : Lut5_CMB = 10'D439;

8'D87 : Lut5_CMB = 10'D433;

8'D88 : Lut5_CMB = 10'D426;

8'D89 : Lut5_CMB = 10'D419;

8'D90 : Lut5_CMB = 10'D411;

8'D91 : Lut5_CMB = 10'D404;

8'D92 : Lut5_CMB = 10'D396;

8'D93 : Lut5_CMB = 10'D388;

8'D94 : Lut5_CMB = 10'D379;

8'D95 : Lut5_CMB = 10'D371;

8'D96 : Lut5_CMB = 10'D362;

8'D97 : Lut5_CMB = 10'D353;

8'D98 : Lut5_CMB = 10'D344;

8'D99 : Lut5_CMB = 10'D334;

8'D100 : Lut5_CMB = 10'D325;

8'D101 : Lut5_CMB = 10'D315;

8'D102 : Lut5_CMB = 10'D305;

8'D103 : Lut5_CMB = 10'D295;

8'D104 : Lut5_CMB = 10'D284;

8'D105 : Lut5_CMB = 10'D274;

8'D106 : Lut5_CMB = 10'D263;

8'D107 : Lut5_CMB = 10'D252;

8'D108 : Lut5_CMB = 10'D241;

8'D109 : Lut5_CMB = 10'D230;

8'D110 : Lut5_CMB = 10'D219;

8'D111 : Lut5_CMB = 10'D207;

8'D112 : Lut5_CMB = 10'D196;

8'D113 : Lut5_CMB = 10'D184;

8'D114 : Lut5_CMB = 10'D172;

8'D115 : Lut5_CMB = 10'D161;

8'D116 : Lut5_CMB = 10'D149;

8'D117 : Lut5_CMB = 10'D137;

8'D118 : Lut5_CMB = 10'D124;

8'D119 : Lut5_CMB = 10'D112;

8'D120 : Lut5_CMB = 10'D100;

8'D121 : Lut5_CMB = 10'D88;

8'D122 : Lut5_CMB = 10'D75;

8'D123 : Lut5_CMB = 10'D63;

8'D124 : Lut5_CMB = 10'D50;

8'D125 : Lut5_CMB = 10'D38;

8'D126 : Lut5_CMB = 10'D25;

8'D127 : Lut5_CMB = 10'D13;

8'D128 : Lut5_CMB = 10'D0;

8'D129 : Lut5_CMB = 10'D1011;

8'D130 : Lut5_CMB = 10'D999;

8'D131 : Lut5_CMB = 10'D986;

8'D132 : Lut5_CMB = 10'D974;

8'D133 : Lut5_CMB = 10'D961;

8'D134 : Lut5_CMB = 10'D949;

8'D135 : Lut5_CMB = 10'D936;

8'D136 : Lut5_CMB = 10'D924;

8'D137 : Lut5_CMB = 10'D912;

8'D138 : Lut5_CMB = 10'D900;

8'D139 : Lut5_CMB = 10'D887;

8'D140 : Lut5_CMB = 10'D875;

8'D141 : Lut5_CMB = 10'D863;

8'D142 : Lut5_CMB = 10'D852;

8'D143 : Lut5_CMB = 10'D840;

8'D144 : Lut5_CMB = 10'D828;

8'D145 : Lut5_CMB = 10'D817;

8'D146 : Lut5_CMB = 10'D805;

8'D147 : Lut5_CMB = 10'D794;

8'D148 : Lut5_CMB = 10'D783;

8'D149 : Lut5_CMB = 10'D772;

8'D150 : Lut5_CMB = 10'D761;

8'D151 : Lut5_CMB = 10'D750;

8'D152 : Lut5_CMB = 10'D740;

8'D153 : Lut5_CMB = 10'D729;

8'D154 : Lut5_CMB = 10'D719;

8'D155 : Lut5_CMB = 10'D709;

8'D156 : Lut5_CMB = 10'D699;

8'D157 : Lut5_CMB = 10'D690;

8'D158 : Lut5_CMB = 10'D680;

8'D159 : Lut5_CMB = 10'D671;

8'D160 : Lut5_CMB = 10'D662;

8'D161 : Lut5_CMB = 10'D653;

8'D162 : Lut5_CMB = 10'D645;

8'D163 : Lut5_CMB = 10'D636;

8'D164 : Lut5_CMB = 10'D628;

8'D165 : Lut5_CMB = 10'D620;

8'D166 : Lut5_CMB = 10'D613;

8'D167 : Lut5_CMB = 10'D605;

8'D168 : Lut5_CMB = 10'D598;

8'D169 : Lut5_CMB = 10'D591;

8'D170 : Lut5_CMB = 10'D585;

8'D171 : Lut5_CMB = 10'D579;

8'D172 : Lut5_CMB = 10'D572;

8'D173 : Lut5_CMB = 10'D567;

8'D174 : Lut5_CMB = 10'D561;

8'D175 : Lut5_CMB = 10'D556;

8'D176 : Lut5_CMB = 10'D551;

8'D177 : Lut5_CMB = 10'D546;

8'D178 : Lut5_CMB = 10'D542;

8'D179 : Lut5_CMB = 10'D538;

8'D180 : Lut5_CMB = 10'D534;

8'D181 : Lut5_CMB = 10'D531;

8'D182 : Lut5_CMB = 10'D527;

8'D183 : Lut5_CMB = 10'D524;

8'D184 : Lut5_CMB = 10'D522;

8'D185 : Lut5_CMB = 10'D520;

8'D186 : Lut5_CMB = 10'D518;

8'D187 : Lut5_CMB = 10'D516;

8'D188 : Lut5_CMB = 10'D514;

8'D189 : Lut5_CMB = 10'D513;

8'D190 : Lut5_CMB = 10'D513;

8'D191 : Lut5_CMB = 10'D512;

8'D192 : Lut5_CMB = 10'D512;

8'D193 : Lut5_CMB = 10'D512;

8'D194 : Lut5_CMB = 10'D513;

8'D195 : Lut5_CMB = 10'D513;

8'D196 : Lut5_CMB = 10'D514;

8'D197 : Lut5_CMB = 10'D516;

8'D198 : Lut5_CMB = 10'D518;

8'D199 : Lut5_CMB = 10'D520;

8'D200 : Lut5_CMB = 10'D522;

8'D201 : Lut5_CMB = 10'D524;

8'D202 : Lut5_CMB = 10'D527;

8'D203 : Lut5_CMB = 10'D531;

8'D204 : Lut5_CMB = 10'D534;

8'D205 : Lut5_CMB = 10'D538;

8'D206 : Lut5_CMB = 10'D542;

8'D207 : Lut5_CMB = 10'D546;

8'D208 : Lut5_CMB = 10'D551;

8'D209 : Lut5_CMB = 10'D556;

8'D210 : Lut5_CMB = 10'D561;

8'D211 : Lut5_CMB = 10'D567;

8'D212 : Lut5_CMB = 10'D572;

8'D213 : Lut5_CMB = 10'D579;

8'D214 : Lut5_CMB = 10'D585;

8'D215 : Lut5_CMB = 10'D591;

8'D216 : Lut5_CMB = 10'D598;

8'D217 : Lut5_CMB = 10'D605;

8'D218 : Lut5_CMB = 10'D613;

8'D219 : Lut5_CMB = 10'D620;

8'D220 : Lut5_CMB = 10'D628;

8'D221 : Lut5_CMB = 10'D636;

8'D222 : Lut5_CMB = 10'D645;

8'D223 : Lut5_CMB = 10'D653;

8'D224 : Lut5_CMB = 10'D662;

8'D225 : Lut5_CMB = 10'D671;

8'D226 : Lut5_CMB = 10'D680;

8'D227 : Lut5_CMB = 10'D690;

8'D228 : Lut5_CMB = 10'D699;

8'D229 : Lut5_CMB = 10'D709;

8'D230 : Lut5_CMB = 10'D719;

8'D231 : Lut5_CMB = 10'D729;

8'D232 : Lut5_CMB = 10'D740;

8'D233 : Lut5_CMB = 10'D750;

8'D234 : Lut5_CMB = 10'D761;

8'D235 : Lut5_CMB = 10'D772;

8'D236 : Lut5_CMB = 10'D783;

8'D237 : Lut5_CMB = 10'D794;

8'D238 : Lut5_CMB = 10'D805;

8'D239 : Lut5_CMB = 10'D817;

8'D240 : Lut5_CMB = 10'D828;

8'D241 : Lut5_CMB = 10'D840;

8'D242 : Lut5_CMB = 10'D852;

8'D243 : Lut5_CMB = 10'D863;

8'D244 : Lut5_CMB = 10'D875;

8'D245 : Lut5_CMB = 10'D887;

8'D246 : Lut5_CMB = 10'D900;

8'D247 : Lut5_CMB = 10'D912;

8'D248 : Lut5_CMB = 10'D924;

8'D249 : Lut5_CMB = 10'D936;

8'D250 : Lut5_CMB = 10'D949;

8'D251 : Lut5_CMB = 10'D961;

8'D252 : Lut5_CMB = 10'D974;

8'D253 : Lut5_CMB = 10'D986;

8'D254 : Lut5_CMB = 10'D999;

// 8'D255

default : Lut5_CMB = 10'D1011;

endcase

end

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// hilite_system('tb_demo_dds/DDS/UnitDelay2')

// Register #6 : <10,0,t>

always @(posedge CLK or negedge RST_N)

begin : proc_Reg6_REG

if(RST_N==1'B0)

Reg6_REG <= 10'H0; // <10,0,t> 0.000000

else

Reg6_REG <= Lut5_CMB;

end

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// Output

assign DOUT = Reg6_REG; // <10,0,t> hilite_system('tb_demo_dds/DDS/OUP')

//-----------------------------------------------------------------------------

endmodule // rtlgen_demo_dds

//-----------------------------------------------------------------------------

// Statistics:

// Input Port(non-memory): 1

// Output Port(non-memory): 1

// Instances(non-memory): 8

// Internal Signal: 6

// Total Register: 34 bits

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// Internal Comb. Signals Top 50 (Vector Excluded)

// Index NAME FXP

// # 1 Add1_CMB <25,1,u>

// # 2 Fmt2_CMB <24,0,u>

// # 3 Fmt4_CMB <8,0,u>

//-----------------------------------------------------------------------------

// Internal Registers Top 50 (Vector Excluded)

// Index NAME FXP

// # 1 Reg3_REG <24,0,u>

// # 2 Reg6_REG <10,0,t>

//-----------------------------------------------------------------------------

// Multiplier Count: 0 Total bits: 0

// Multiplier Top 50 of 0

// Index NAME FXP

//-----------------------------------------------------------------------------

// Adder/Subtractor Count: 1 Total bits: 0

// Adder/Subtractor Top 50 of 1

// Index NAME FXP

// # 1 Add1_CMB <25,1,u>

//-----------------------------------------------------------------------------

//-----------------------------------------------------------------------------

// End of the file.

//-----------------------------------------------------------------------------

最后

以上就是朴素店员最近收集整理的关于硬件设计的MBD实践:自动生成RTL代码的全部内容,更多相关硬件设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复