一、实验目的

1.掌握 Quartus II 进行 FPGA 开发的流程,熟练利用 verilog 进行逻辑电路设计,并熟悉 modelsim 仿真方法。

2.熟悉触发器、计数器和分频器在时序逻辑电路设计中的应用。

3.学会流水显示设计方法

二、实验步骤

在老师的指导下,打开 Quartus II,利用 verilog 文本输入方法,完成上述描述的逻辑电路的输入、 编译、仿真和下载。并观察其在 DE2 平台上的实现情况。步骤如下:

(1).在文本文档中写出 verilog 代码,在另外一个文本文档中写出 testbench 测试代码。

(2).建立工程,选择硬件,选择仿真工具为 modelsim-altera,创建 Verilog 文件,进行文本输入。

(3).编译和分配引脚。(从 DE2_pin_assignments 文件中正确选择要使用的引脚,并输入)

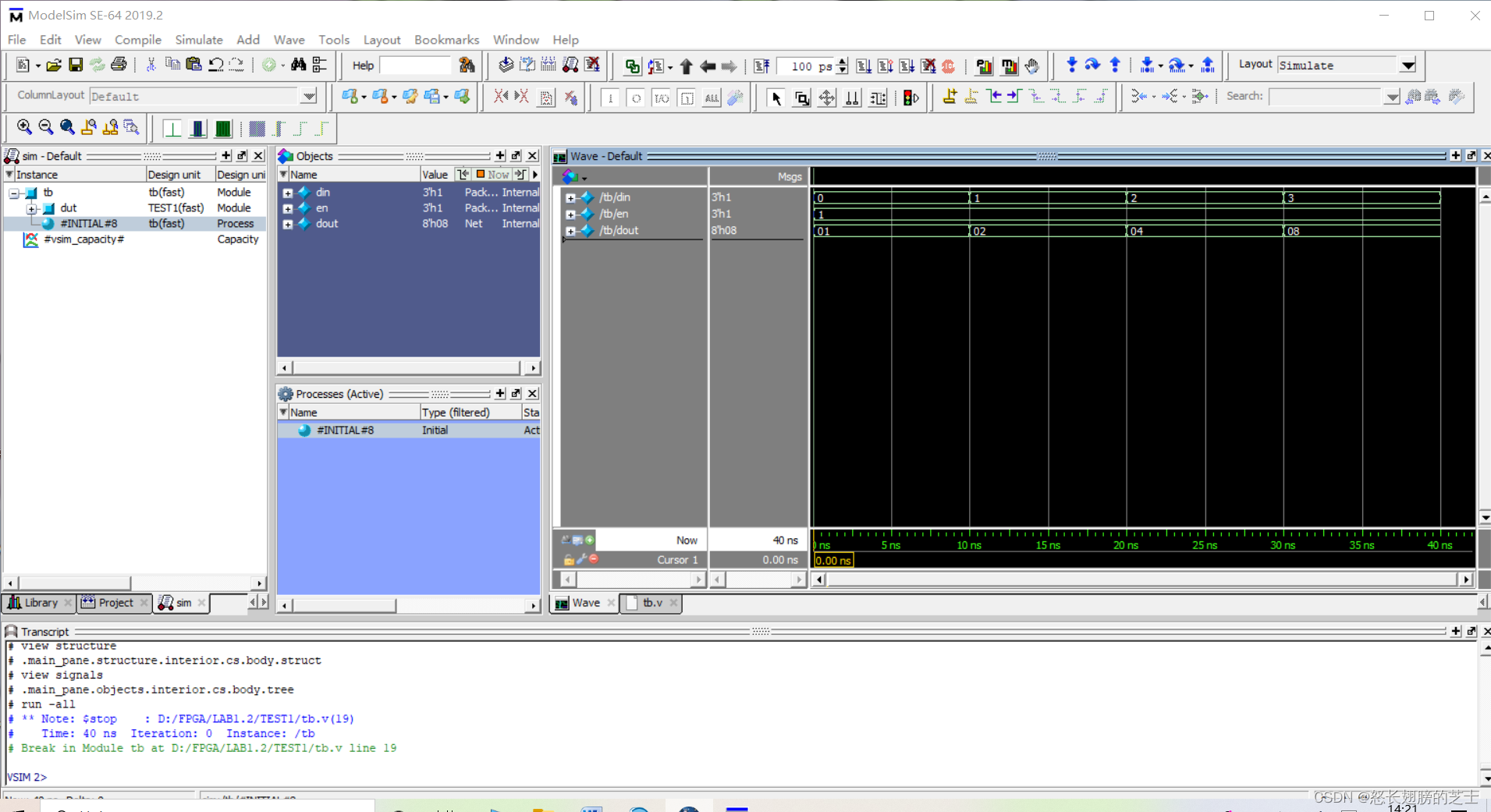

(4).新建 testbench 用于 modelsim 仿真。testbench 完成后,调用 modelsim 进行功能和时序仿真。

(5).配置 FPGA,在 DE2 上实现要完成的功能。并测试。

三、实验结果

1. 硬件电路主要功能部分代码

module TEST1(en,din,dout);

input[2:0] din;

input en;

output[7:0]dout;

reg [7:0]dout;

always@(en or din)

begin

if (!en) dout=8'h00;

else

case(din)

3'b000: dout=8'h01;

3'b001: dout=8'h02;

3'b010: dout=8'h04;

3'b011: dout=8'h08;

3'b100: dout=8'h10;

3'b101: dout=8'h20;

3'b110: dout=8'h40;

3'b111: dout=8'h80;

default dout=8'bx;

endcase

end

endmodule

2、testbench激励文件主要功能部分代码

timescale 1ns/1ps

module tb;

reg[2:0] din,en;

wire [7:0]dout;

initial begin

din=00;

en = 1;

#10 din=1;

din=01;

#10 din=0;

din=10;

#10 din=0;

din=11;

#10 din=1;

$stop;

end

TEST1 dut(

.din(din),.en(en),

.dout(dout)

);

endmodule

3、引脚分配及下载后的结果

当开发板连接电脑下载好程序后,通过开关引导led灯工作,开关打开后,则led灯点亮。

4、仿真或运行结果

最后

以上就是现代人生最近收集整理的关于VHDL实验二:流水灯一、实验目的二、实验步骤三、实验结果的全部内容,更多相关VHDL实验二:流水灯一、实验目内容请搜索靠谱客的其他文章。

![吉大20年3月计算机作业考核,[吉林大学]吉大20年4月《数字逻辑电路》作业考核试题(100分)...](https://www.shuijiaxian.com/files_image/reation/bcimg13.png)

发表评论 取消回复