目录

题目1:Exams/m2014 q4a

题目2:Exams/m2014 q4b

题目3:Exams/m2014 q4c

题目4:Exams/m2014 q4d

题目5:组合触发器电路,包括一个触发器和多路复用器。Mt2015 muxdff

题目6:n位移位寄存器:Exams/2014 q4a

题目1:Exams/m2014 q4a

实现以下电路:

请注意,这是一个闩锁,因此预计 Quartus 会发出有关推断出闩锁的警告。

模块声明

module top_module (

input d,

input ena,

output q);

分析:

- 锁存器是电平敏感(非边沿敏感)电路,因此在始终块中,它们使用电平敏感度列表。

- 但是,它们仍然是顺序元素,因此应使用非阻塞赋值。

- D型锁存器在使能时就像导线(或非反相缓冲器),并在禁用时保留当前值。

代码如下:

module top_module (

input d,

input ena,

output q);

always@(ena)

begin

if(ena)

q <= d;

end

endmodule题目2:Exams/m2014 q4b

实现以下电路:

模块声明

module top_module (

input clk,

input d,

input ar, // asynchronous reset,异步复位

output q);

分析:这是一个含有异步复位端的D触发器

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output q);

always@(posedge clk or posedge ar)

begin

if(ar)

q <= 0;

else

q <= d;

end

endmodule题目3:Exams/m2014 q4c

实现以下电路:

模块声明

module top_module (

input clk,

input d,

input r, // synchronous reset,同步复位

output q);

分析:这是一个同步复位的D触发器

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

always@(posedge clk)

begin

if(r)

q <= 0;

else

q <= d;

end

endmodule题目4:Exams/m2014 q4d

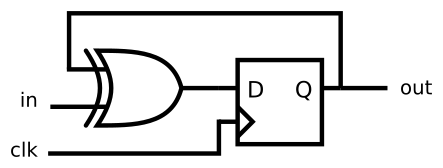

实现以下电路:

模块声明

module top_module (

input clk,

input in,

output out);

分析:这是一个带有异或门的D触发器。其逻辑功能为:当上升沿到来时,输入端D=

in^out。

module top_module (

input clk,

input in,

output out);

always@(posedge clk)

begin

out = in^out;

end

endmodule

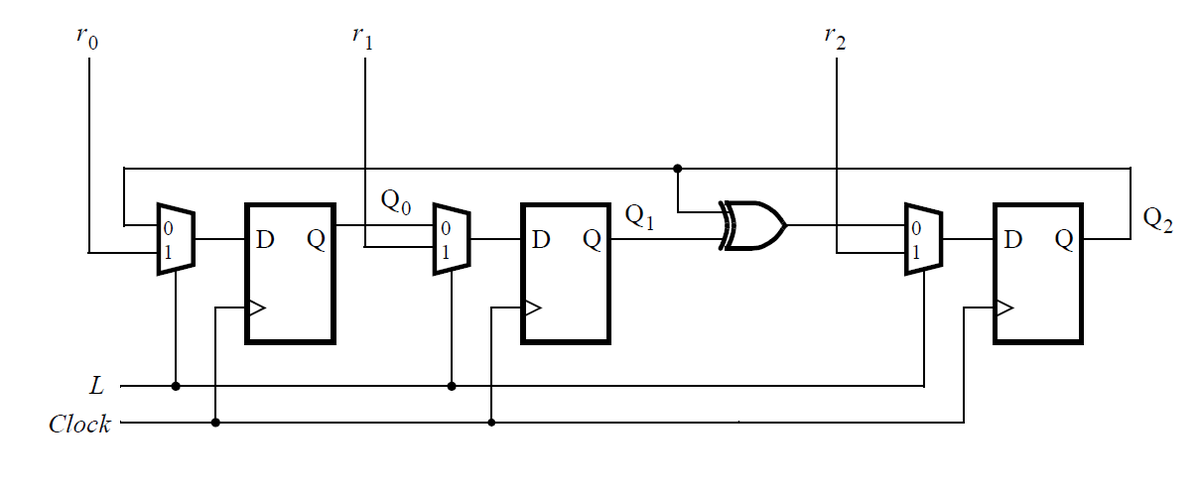

题目5:组合触发器电路,包括一个触发器和多路复用器。Mt2015 muxdff

考虑下面的顺序电路:

假设您要为此电路实现分层 Verilog 代码,使用具有触发器和多路复用器的子模块的三个实例化。为此子模块编写一个名为top_module的 Verilog 模块(包含一个触发器和多路复用器)。

模块声明

module top_module ( input clk, input L, input r_in, input q_in, output reg Q);

分析:该电路是3位的移位寄存器,构成了一个扭环形计数器。据题意可知代码如下:

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

always@(posedge clk)

begin

if(L==0)

Q <= q_in;

else

Q <= r_in;

end

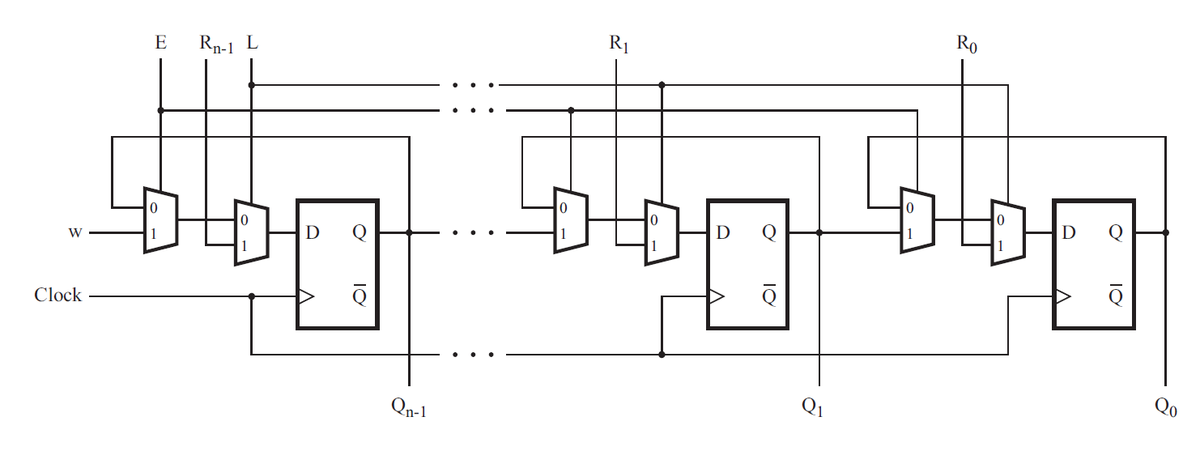

endmodule题目6:n位移位寄存器:Exams/2014 q4a

考虑下面所示的n位移位寄存器电路:

为该电路的一个阶段编写一个名为top_module的Verilog模块,包括触发器和多路复用器。

模块声明

module top_module (

input clk,

input w, R, E, L,

output Q

);

其中代码编写如下:

module top_module (

input clk,

input w, R, E, L,

output Q

);

wire c1,c2;

always@(posedge clk)

begin

if(L==1)

Q <= R;

else

begin

if(E==1)

Q <= w;

else

Q <=Q;

end

end

endmodule最后

以上就是高贵爆米花最近收集整理的关于HDLBITS笔记24:触发器的进阶练习(锁存器、同步/异步复位触发器、数据选择器综合触发器)题目1:Exams/m2014 q4a题目2:Exams/m2014 q4b题目3:Exams/m2014 q4c题目4:Exams/m2014 q4d题目5:组合触发器电路,包括一个触发器和多路复用器。Mt2015 muxdff题目6:n位移位寄存器:Exams/2014 q4a的全部内容,更多相关HDLBITS笔记24:触发器的进阶练习(锁存器、同步/异步复位触发器、数据选择器综合触发器)题目1:Exams/m2014内容请搜索靠谱客的其他文章。

发表评论 取消回复