本来只想做一下序列信号发生器的手撕代码,但是综合之后看了一下生成的原理图,觉得无法理解,就研究了一下。

序列信号发生器很简单,我用移位实现的,代码如下

module xuliexinhao(

input sys_clk, //时钟

input sys_rst_n, //复位,低有效

input [9:0] in, //待输出序列

output reg out //输出

);

reg [9:0] data;

always @(posedge sys_clk,negedge sys_rst_n) begin

if (!sys_rst_n) begin

out <= 0;

data <= in;

end

else begin

out <= data[9];

data <= {data[8:0],data[9]};

end

end

endmodule这个没有什么好说的很简单,再仿真例化一下就行了,就不贴代码了。

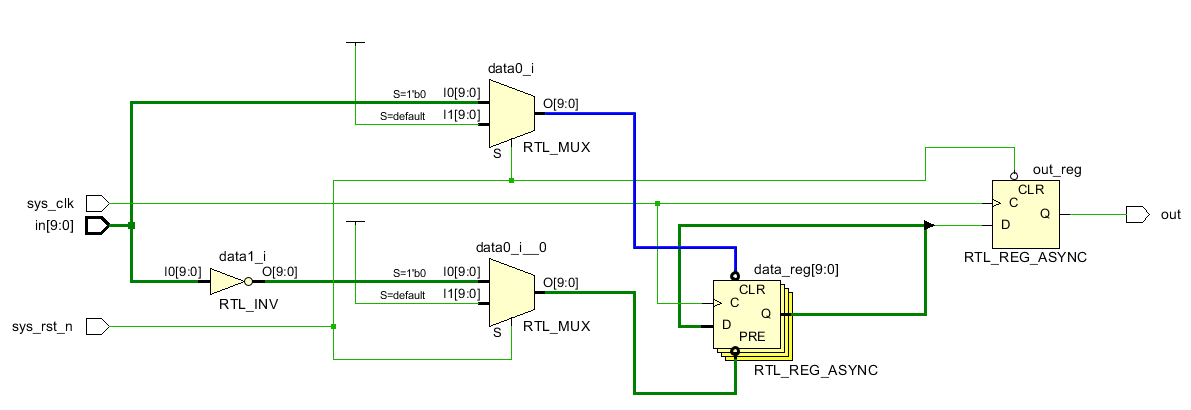

但是这个生成的电路图是这样的

难点在于我不理解异步置位,即data寄存器的PRE引脚,对D触发器的异步置位和异步复位讲解的文章不多,所以就写一下。在这里要知道D触发器特性,CLR是异步复位,PRE是异步置位,都是低电平有效优先级CLR>PRE>clk。

若CLR=0,异步复位有效Q立即输出0,。

若CLR=1,看PRE,如果PRE=0,则异步置位有效,Q=1;(有人说Q=D,我验证之后发现是不对的),如果PRE=1,Q=D。

到这里上面就好理解了。当复位有效信号到达时(异步复位),控制两个二选一选择器。选择器S接的就是复位信号sys_rst_n,如果复位S=0,上面选择器输出是输入信号in,下面选择器输出输入信号的取反~in,输入信号是10位的,所以接10个D触发器。当复位有效时,如果in某一位等于0,那么CLR端 输入就为0,对应的输出Q就为0;如果n某一位等于1,CLR端输入就为1,对应的PRE端输入一定为0(有取反),PRE为0,输出立即置1。这样就实现了复位data=in;

网上对D触发器异步复位和置位讲解的不多,还有讲错的,我也是参考别人的解释,自己得出的结论,若有错误,望批评指正!

最后

以上就是搞怪导师最近收集整理的关于序列信号发生器,之D触发器异步复位和异步置位的全部内容,更多相关序列信号发生器内容请搜索靠谱客的其他文章。

发表评论 取消回复