记得面菊厂的逻辑部时让我用触发器搭一个三分频电路,当时没打上来。

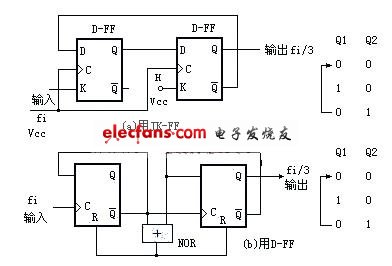

上网查了一下主要有两种方式。

1、JK触发器方式

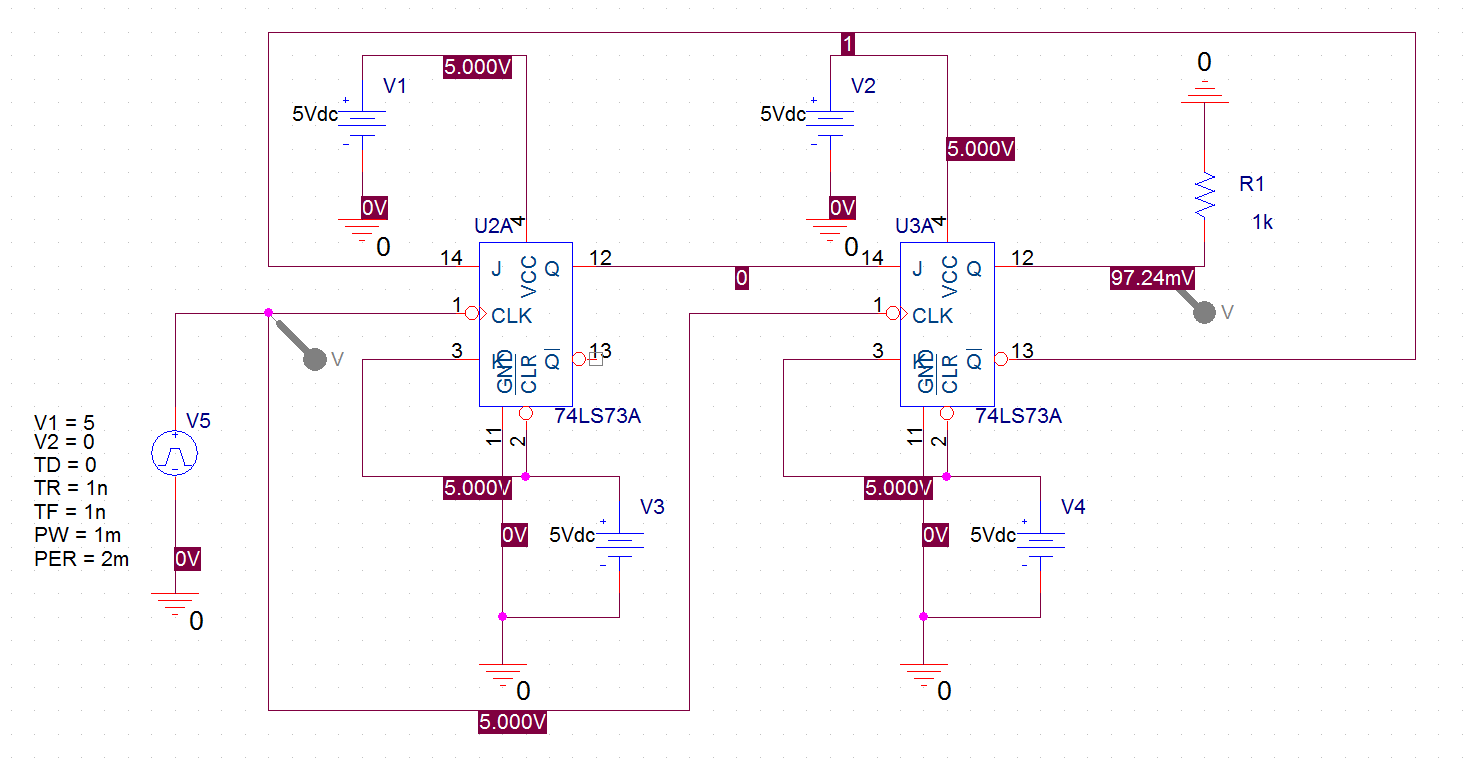

在Pspice中绘制如下:

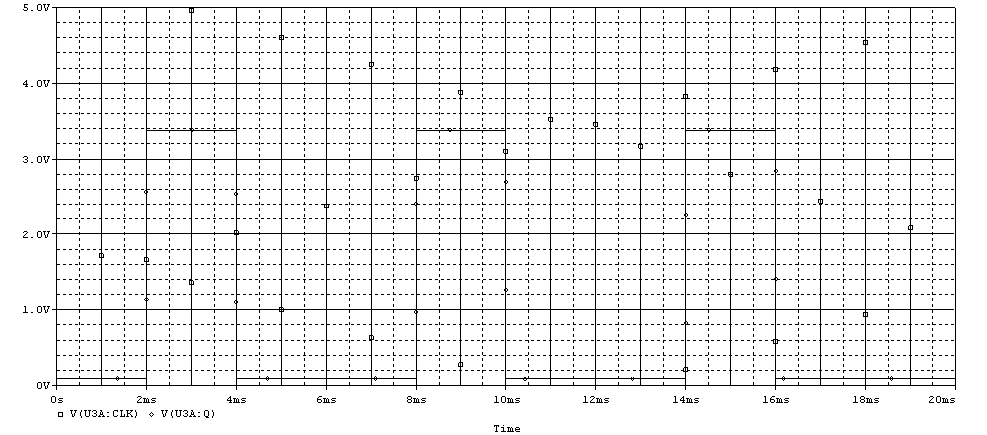

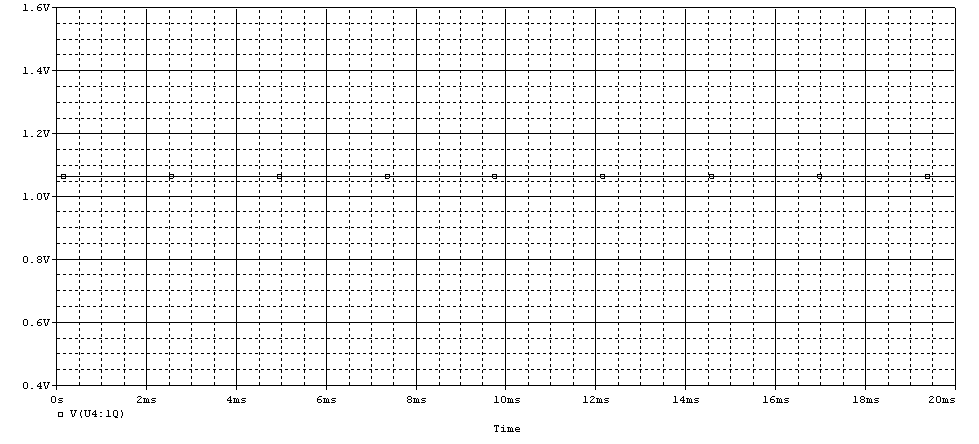

仿真结果如下

在设置脉冲源的时候要尽量缩小上升时间和下降时间,不然会报存在竞争的错误。

逻辑代码:

// 高电平复位,JK触发器

//

module JKFF(

input clk,

input rst,

input J,

input K,

output reg Q,

output NQ

);

always @ (posedge clk or posedge rst)

begin

if (rst)

begin

Q <= 1'b0;

end

else

begin

Q <= J * (~Q) + (~K) * (NQ);

end

end

assign NQ = ~Q;

endmodule

module three_div(

input clk_in,

input rst,

output clk_out

);

wire NQ2,Q1;

JKFF jk1(

.clk(clk_in),

.rst(rst),

.J(NQ2),

.K(1'b1),

.Q(Q1),

.NQ()

);

JKFF jk2(

.clk(clk_in),

.rst(rst),

.J(Q1),

.K(1'b1),

.Q(clk_out),

.NQ(NQ2)

);

endmodule

测试文件

module test(

);

reg clk_in,rst;

wire clk_out;

initial

begin

clk_in = 1'b0;

rst = 1'b0;

#1 rst = 1'b1;

#1 rst = 1'b0;

end

always #5 clk_in = ~clk_in;

three_div my(

.clk_in(clk_in),

.rst(rst),

.clk_out(clk_out)

);

endmodule

可以达到三分频的目的,但是占空比只有1/3.

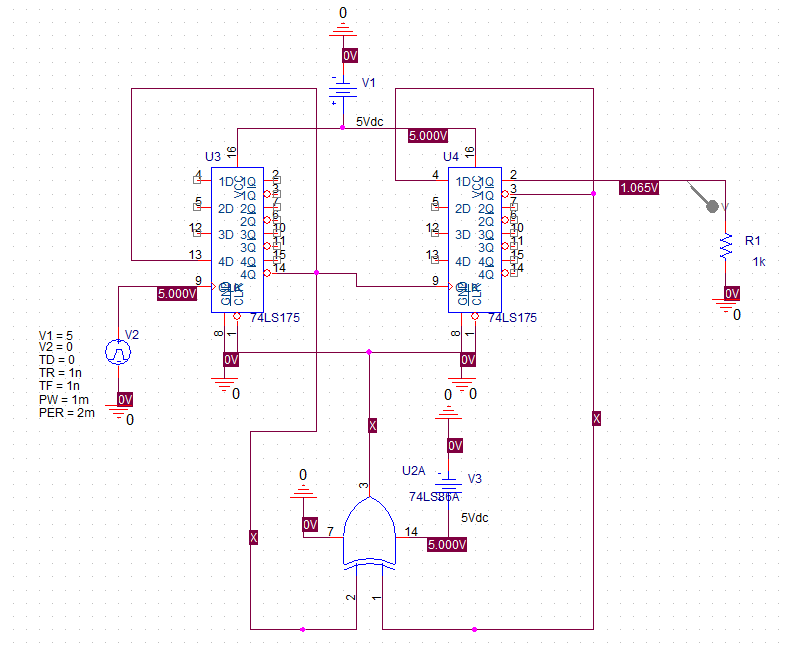

2、D触发器

Pspice

仿真结果

可以看出来结果不对。因为异或门没有初始化电平,输入输出都是不定值。尝试加入延时启动的开关进行初始化但是还是不行,因为复位为低电平触发,一旦两个D触发器的NQ都输出1时,会把两个触发器都锁住,再也没有状态变化。

逻辑仿真结果与此一致。所以用D触发器+异或门的方式是实现不了的。

3、逻辑通过计数实现50%占空比的三分频

逻辑代码

// 低电平复位

//

module tdiv_co(

input clk_in,

input rst,

output reg clk_out

);

reg [2:0] co;//counter

always @ (clk_in or rst)

begin

if (!rst)

begin

clk_out <= 1'b0;

co <= 2'b0;

end

else

begin

co <= co + 2'b1;

if (co == 3'd2)//X分频则为d(X-1)

begin

clk_out <= ~clk_out;

co <= 2'b0;

end

end

end

endmodule

相对来说用逻辑计数能产生任意分频的50%占空比,更合适。

4、类似与状态机

// 低电平复位

//

module state_ma(

input clk_in,

input rst,

output clk_out

);

reg s1,s2;

always @ (posedge clk_in or negedge rst)

begin

if (!rst)

begin

s1 <= 1'b0;

s2 <= 1'b0;

end

else

begin

if ((!s1) && (!s2))

begin

s1 <= 1'b0;

s2 <= 1'b1;

end

else

begin

if ((!s1) && (s2))

begin

s1 <= 1'b1;

s2 <= 1'b0;

end

else

begin

if ((s1) && (!s2))

begin

s1 <= 1'b0;

s2 <= 1'b0;

end

else

begin

s1 <= 1'b0;

s2 <= 1'b0;

end

end

end

end

end

assign clk_out = s1;

endmodule

测试文件

module test(

);

wire clk_out;

reg clk_in,rst;

initial

begin

clk_in = 1'b0;

rst = 1'b1;

#1 rst = 1'b0;

#1 rst = 1'b1;

end

always #5 clk_in = ~clk_in;

state_ma my(

.clk_in(clk_in),

.rst(rst),

.clk_out(clk_out)

);

endmodule

最后

以上就是唠叨月光最近收集整理的关于利用触发器生成三分频的全部内容,更多相关利用触发器生成三分频内容请搜索靠谱客的其他文章。

发表评论 取消回复