随着便携式设备(电池供电)在过去十年间的快速增长,象原来的业界标准 LM340 和 LM317 这样的稳压器件已经无法满足新的需要。这些稳压器使用NPN 达林顿管,在本文中称其为NPN 稳压器(NPN regulators)。预期更高性能的稳压器件已经由新型的低压差(Low-dropout)稳压器(LDO)和准LDO稳压器(quasi-LDO)实现了。

NPN 稳压器(NPN regulators)

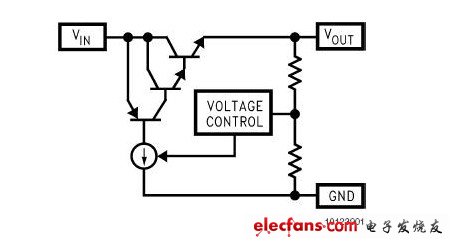

在NPN稳压器(图1:NPN稳压器内部结构框图)的内部使用一个 PNP管来驱动 NPN 达林顿管(NPN Darlington pass transistor),输入输出之间存在至少1.5V~2.5V的压差(dropout voltage)。这个压差为:

Vdrop = 2Vbe +Vsat(NPN 稳压器) (1)

图1

LDO 稳压器(LDO regulators)

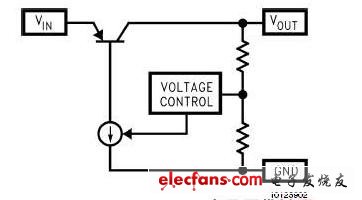

在LDO(Low Dropout)稳压器(图2:LDO稳压器内部结构框图)中,导通管是一个PNP管。LDO的最大优势就是PNP管只会带来很小的导通压降,满载(Full-load)的跌落电压的典型值小于500mV,轻载(Light loads)时的压降仅有10~20mV。LDO的压差为:

Vdrop = Vsat (LDO 稳压器) (2)

图2

准LDO 稳压器(Quasi-LDO regulators)

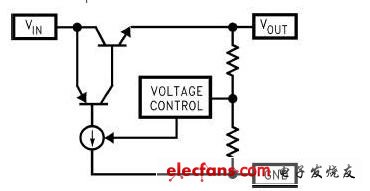

准LDO(Quasi-LDO)稳压器(图3: 准 LDO 稳压器内部结构框图)已经广泛应用于某些场合,例如:5V到3.3V 转换器。 准LDO介于 NPN 稳压器和 LDO 稳压器之间而得名, 导通管是由单个PNP 管来驱动单个NPN 管。 因此,它的跌落压降介于NPN稳压器和LDO之间:

Vdrop = Vbe +Vsat (3)

图3

稳压器的工作原理(Regulator OperaTIon)

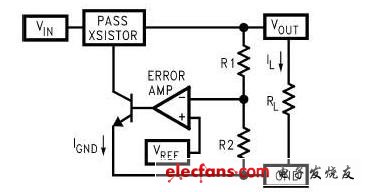

所有的稳压器,都利用了相同的技术实现输出电压的稳定(图4:稳压器工作原理图)。输出电压通过连接到误差放大器(Error Amplifier)反相输入端(InverTIng Input)的分压电阻(ResisTIve Divider)采样(Sampled),误差放大器的同相输入端(Non-inverTIng Input)连接到一个参考电压Vref。 参考电压由IC内部的带隙参考源(Bandgap Reference)产生。 误差放大器总是试图迫使其两端输入相等。为此,它提供负载电流以保证输出电压稳定:

Vout = Vref(1 + R1 / R2) (4)

图4

附加说明带隙基准,

英文Bandgap voltage reference,常常有人简单地称它为Bandgap。最经典的带隙基准是利用一个具有正温度系数的电压与具有负温度系数的电压之和,二者温度系数相互抵消,实现与温度无关的电压基准,约为1.25V。因为其基准电压与硅的带隙电压差不多,因而称为带隙基准。实际上利用的不是带隙电压。有些Bandgap结构输出电压与带隙电压也不一致

性能比较(Performance Comparison)

NPN,LDO和准LDO在电性能参数上的最大区别是:跌落电压(Dropout Voltage)和地脚电流(Ground Pin Current)。跌落电压前文已经论述。为了便于分析,我们定义地脚电流为Ignd (参见图4),并忽略了IC到地的小偏置电流。那么,Ignd等于负载电流IL除以导通管的增益。

NPN 稳压器中,达林顿管的增益很高(High Gain),所以它只需很小的电流来驱动负载电流IL。这样它的地脚电流Ignd也会很低,一般只有几个mA。 准LDO也有较好的性能,如国半(NS)的LM1085能够输出3A的电流却只有10mA的地脚电流。

然而,LDO的地脚电流会比较高。在满载时,PNP管的β值一般是15~20。也就是说LDO的地脚电流一般达到负载电流的7%。

NPN稳压器的最大好处就是无条件的稳定,大多数器件不需额外的外部电容。 LDO在输出端最少需要一个外部电容以减少回路带宽(Loop Bandwidth)及提供一些正相位转移(Positive Phase Shift)补偿。 准LDO一般也需要有输出电容,但容值要小于LDO的并且电容的ESR局限也要少些。

反馈及回路稳定性(Feedback and Loop Stability)

所有稳压器都使用反馈回路(Feedback Loop)以保持输出电压的稳定。反馈信号在通过回路后都会在增益和相位上有所改变,通过在单位增益(Unity Gain,0dB)频率下的相位偏移总量来确定回路的稳定性。

波特图(Bode Plots)

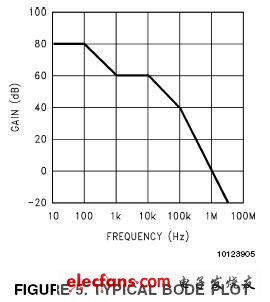

波特图(Bode Plots)可用来确认回路的稳定性,回路的增益(Loop Gain,单位:dB)是频率(Frequency)的函数(图5:典型的波特图)。 回路增益及其相关内容在下节介绍。 回路增益可以用网络分析仪(Network Analyzer)测量。 网络分析仪向反馈回路(Feedback Path)注入低电平的正弦波(Sine Wave),随着直流电压(DC)的不断升高, 这些正弦波信号完成扫频,直到增益下降到0dB。然后测量增益的响应(Gain Response)。

图5

波特图是很方便的工具,它包含判断闭环系统(Closed-loop System)稳定性的所有必要信息。 包括下面几个关键参数:环路增益(Loop Gain),相位裕度(Phase Margin)和零点(Zeros)、极点(Poles)。

回路增益(LOOP GAIN)

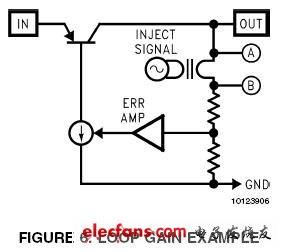

闭环系统(Closed-loop System)有个特性称为回路增益(Loop Gain)。在稳压电路中,回路增益定义为反馈信号(Feedback Signal)通过整个回路后的电压增益(Voltage Gain)。为了更好的解释这个概念,LDO的结构框图(图2)作如下修改(图6:回路增益的测量方法)。

图6

变压器(Transformer)用来将交流信号(AC Signal)注入(Inject)到“A”、“‘B”点间的反馈回路。借助这个变压器,用小信号正弦波(Small-signal Sine Wave)来“调制”(modulate)反馈信号。可以测量出A、B两点间的交流电压(AC Voltage),然后计算回路增益。回路增益定义为两点电压的比(Ratio): Loop Gain = Va / Vb (5)

需要注意, 从Vb点开始传输的信号, 通过回路(Loop)时会出现相位偏移(Phase Shift),最终到达Va点。相位偏移(Phase Shift)的多少决定了回路的稳定程度(Stability)。

反馈(FEEDBACK)

如前所述,所有的稳压器都采用反馈( Feedback)以使输出电压稳定。输出电压是通过电阻分压器进行采样的(图6),并且该分压信号反馈到误差放大器的一个输入端,误差放大器的另一个输入端接参考电压,误差放大器将会调整输出到导通管(Pass Transistor)的输出电流以保持直流电压(DC Valtage)的稳定输出。

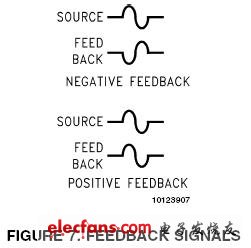

为了达到稳定的回路就必须使用负反馈(Negative Feedback)。负反馈,有时亦称为改变极性的反馈(degenerative feedback),与源信号的极性相反(图7:反馈信号的相位示意图)。

图7

负反馈与源(Source)的极性相反,它总会阻止输出的任何变化。也就是说,如果输出电压想要变高(或变低),负反馈回路总会阻止,强制其回到正常值。

正反馈(Positive Feedback)是指当反馈信号与源信号有相同的极性时就发生的反馈。此时,回路响应会与发生变化的方向一致。显而易见不能达到输出的稳定,不能消除输出电压的改变,反而将变化趋势扩大了。

当然,不会有人在线性稳压器件中使用正反馈。但是如果出现180°的相移,负反馈就成为正反馈了。

相位偏移(PHASE SHIFT)

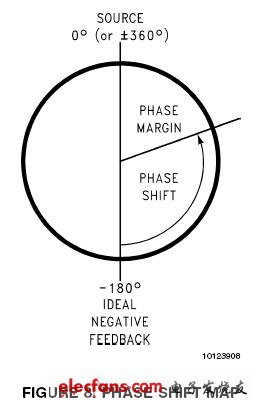

相位偏移就是反馈信号经过整个回路后出现的相位改变(Phase Change)的总和(相对起始点)。相位偏移,单位用度(Degrees)表示,通常使用网络分析仪(network analyzer)测量。理想的负反馈信号与源信号相位差180°(如图8:相位偏移示意图),因此它的起始点在-180°。在图7中可以看到这180°的偏置,也就是波型差半周。

图8

可以看到,从-180°开始,增加180°的相移,信号相位回到零度,就会使反馈信号与源信号的相位相同,从而使回路不稳定。

相位裕度(PHASE MARGIN)

相位裕度(Phase Margin,单位:度),定义为频率的回路增益等 0dB(单位增益,Unity Gain)时,反馈信号总的相位偏移与-180°的差。一个稳定的回路一般需要20°的相位裕度。

相位偏移和相位裕度可以通过波特图中的零、极点计算获得。

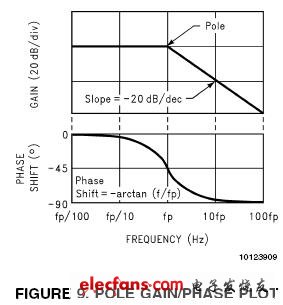

极点(POLES)

极点(Pole)定义为增益曲线(Gain curve)中斜度(Slope)为-20dB/十倍频程的点(图9:波特图中的极点)。每添加一个极点,斜度增加20dB/十倍频程。增加n个极点,n ×(-20dB/十倍频程)。每个极点表示的相位偏移都与频率相关,相移从0到-90°(增加极点就增加相移)。最重要的一点是几乎所有由极点(或零点)引起的相移都是在十倍频程范围内。

注意:一个极点只能增加-90°的相移,所以最少需要两个极点来到达-180°(不稳定点)。

图9

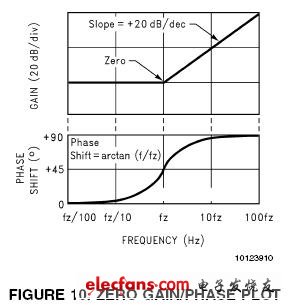

零点(ZEROS)

零点(Zero)定义为在增益曲线中斜度为+20dB/十倍频程的点(如图10:波特图中的零点)。零点产生的相移为0到+90°,在曲线上有+45°角的转变。必须清楚零点就是“反极点”(Anti-pole),它在增益和相位上的效果与极点恰恰相反。这也就是为什么要在LDO稳压器的回路中添加零点的原因,零点可以抵消极点。

图10

波特图分析

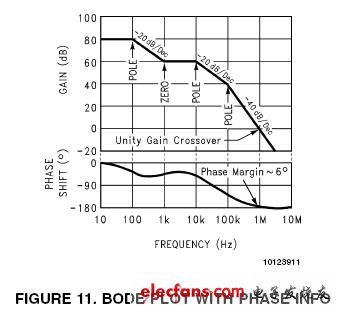

用包含三个极点和一个零点的波特图(图11:波特图)来分析增益和相位裕度。

图11

假设直流增益(DC gain)为80dB,第一个极点(pole)发生在100Hz处。在此频率,增益曲线的斜度变为-20dB/十倍频程。1kHz处的零点使斜度变为0dB/十倍频程,到10kHz处斜度又变成-20dB/十倍频程。在100kHz处的第三个也是最后一个极点将斜度最终变为-40dB/十倍频程。

图11中可看到单位增益点(Unity Gain Crossover,0dB)的交点频率(Crossover Frequency)是1MHz。0dB频率有时也称为回路带宽(Loop Bandwidth)。

相位偏移图表示了零、极点的不同分布对反馈信号的影响。为了产生这个图,就要根据分布的零点、极点计算相移的总和。在任意频率(f)上的极点相移,可以通过下式计算获得: 极点相移 = -arctan(f/fp) (6)

在任意频率(f)上的零点相移,可以通过下式计算获得: 零点相移 = -arctan(f/fz) (7)

此回路稳定吗?为了回答这个问题,我们根本无需复杂的计算,只需要知道0dB时的相移(此例中是1MHz)。

前两个极点和第一个零点分布使相位从-180°变到+90°,最终导致网络相位转变到-90°。最后一个极点在十倍频程中出现了0dB点。代入零点相移公式,可以计算出该极点产生了-84°的相移(在1MHz时)。加上原来的-90°相移,全部的相移是-174°(也就是说相位裕度是6°)。由此得出结论,该回路不能保持稳定,可能会引起振荡。

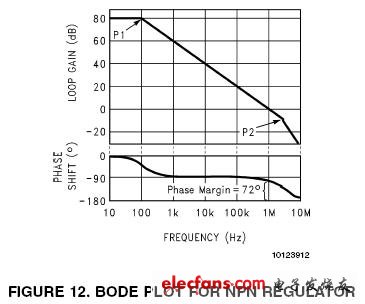

NPN 稳压器补偿

NPN 稳压器的导通管(见图1)的连接方式是共集电极的方式。所有共集电极电路的一个重要特性就是低输出阻抗,意味着电源范围内的极点出现在回路增益曲线的高频部分。

由于NPN稳压器没有固有的低频极点,所以它使用了一种称为主极点补偿(dominant pole compensation)的技术。方法是,在稳压器的内部集成了一个电容,该电容在环路增益的低频端添加了一个极点(图12:NPN稳压器的波特图)。

图12

NPN稳压器的主极点(Dominant Pole), 用P1点表示, 一般设置在100Hz处。100Hz处的极点将增益减小为-20dB/十倍频程直到3MHz处的第二个极点(P2)。在P2处,增益曲线的斜率又增加了-20dB/十倍频程。P2点的频率主要取决于 NPN 功率管及相关驱动电路, 因此有时也称此点为功率极点(Ppower pole)。另外,P2点在回路增益为-10dB处出现,也就表示了单位增益(0dB)频率处(1MHz)的相位偏移会很小。

为了确定稳定性,只需要计算0dB频率处的相位裕度。

第一个极点(P1)会产生-90°的相位偏移,但是第二个极点(P2)只增加了-18°的相位偏移(1MHz处)。也就是说0dB点处的相位偏移为-108°,相位裕度为72°,表明回路非常稳定。

需要两个极点才有可能使回路要达到-180°的相位偏移(不稳定点),而极点P2又处于高频,它在0dB处的相位偏移就很小了。

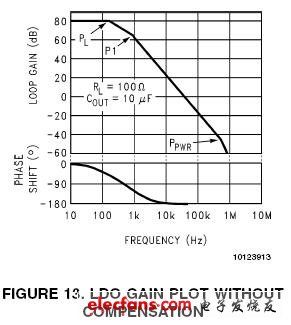

LDO 稳压器的补偿

LDO稳压器中的PNP导通管的接法为共射方式(common emitter)。它相对共集电极方式有更高的输出阻抗。由于负载阻抗和输出容抗的影响在低频程处会出现低频极点(low-frequency pole)。此极点,又称负载极点(load pole),用Pl表示。负载极点的频率由下式计算获得:

F(Pl) =1 / (2π × Rload × Cout) (8)

从此式可知,LDO不能通过简单的添加主极点的方式实现补偿。为什么? 先假设一个5V/50mA的LDO稳压器有下面的条件,在最大负载电流时,负载极点(Pl)出现的频率为:

Pl = 1 / (2π × Rload × Cout)=1/(2π × 100 × 10-5)=160Hz (9)

假设内部的补偿在1kHz处添加了一个极点。由于PNP功率管和驱动电路的存在,在500kHz处会出现一个功率极点(Ppwr)。

假设直流增益为80dB。在最大输出电流时的负载阻值为RL=100Ω,输出电容为Cout =10uF。

使用上述条件可以画出相应的波特图(如图13:未补偿的LDO增益波特图)。

图13

可以看出回路是不稳定的。极点PL和P1每个都会产生-90°的相移。在0dB处(此例为40kHz),相移达到了-180°为了减少负相移(阻止振荡),在回路中必须要添加一个零点。一个零点可以产生+90°的相移,它会抵消两个低频极点的部分影响。

因此,几乎所有的LDO都需要在回路中添加这个零点。该零点一般是通过输出电容的等效串联电阻(ESR)获得的。

使用 ESR 补偿 LDO

等效串联电阻(ESR)是电容的一个基本特性。可以将电容表示为电阻与电容的串联等效电路(图14:电容器的等效电路图)。

图14

输出电容的ESR在回路增益中产生一个零点,可以用来减少负相移。零点处的频率值(Fzero)与ESR和输出电容值密切相关:

Fzero = 1 / (2π × Cout × ESR) (10)

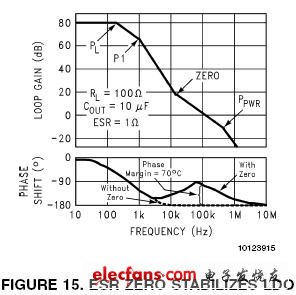

再看上一节的例子(图13),假设输出电容值Cout =10uF,输出电容的ESR = 1Ω。则零点发生在16kHz。图15的波特图显示了添加此零点如何使不稳定的系统恢复稳定。

图15

回路的带宽增加了,单位增益(0dB)的交点频率从30kHz移到了100kHz。到100kHz处该零点总共增加了+81°相移(Positive Phase Shift)。也就是减少了极点PL和P1造成的负相移(Negative Phase Shift)。 极点Ppwr处在500kHz,在100kHz处它仅增加了-11°的相移。累加所有的零、极点,0dB处的总相移为-110°。也就是有+70°的相位裕度,系统非常稳定。

这就解释了选择合适ESR值的输出电容可以产生零点来稳定LDO系统。

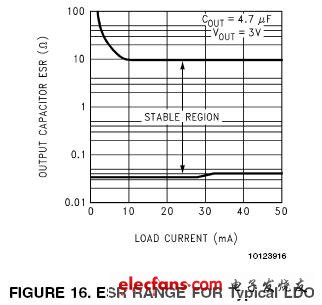

ESR 和稳定性

通常所有的LDO都会要求其输出电容的ESR值在某一特定范围内,以保证输出的稳定性。 LDO制造商会提供一系列由输出电容ESR和负载电流(Load Current)组成的定义稳定范围的曲线(图16:典型LDO的ESR稳定范围曲线),作为选择电容时的参考。

图16

要解释为什么有这些范围的存在,我们使用前面提到的例子来说明ESR的高低对相位裕度的影响。

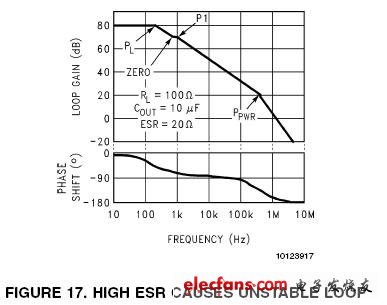

高ESR

同样使用上一节提到的例子,我们假设10uF输出电容的ESR增加到20Ω。这将使零点的频率降低到800Hz(图17:高ESR引起回路振荡的波特图)。

图17

降低零点的频率会使回路的带宽增加,它的单位增益(0Db)的交点频率从100kHz 提高到2MHz。 带宽的增加意味着极点 Ppwr 会出现在带宽内(对比图15)。分析图17波特图中曲线的相位裕度,发现如果同时拿掉该零点和P1或PL中的一个极点,对曲线的形状影响很小。也就是说该回路受到-90° 相移的低频极点和发生-76° 相移的高频极点Ppwr共同影响。

尽管有 14° 的相位裕度,系统可能会稳定。但很多经验测试数据显示,当ESR >10Ω时,由于其它的高频极点的分布(在此简单模型中未表示)很可能会引入不稳定性。

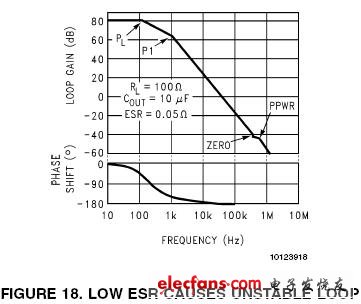

低ESR

选择具有很低的ESR的输出电容,由于一些不同的原因也会产生振荡。继续沿用上一节的例子,假定10uF输出电容的ESR只有50mΩ,则零点的频率会变到320kHz(图18:低ESR引起回路振荡的波特图)。

图18

不用计算就知道系统是不稳定的。两个极点P1和PL在0dB处共产生了-180°的相移。如果要系统稳定,则零点应该在0dB点之前补偿正相移。然而,零点在320kHz处,已经在系统带宽之外了,所以无法起到补偿作用。

输出电容的选择

综上,输出电容是用来补偿LDO稳压器的,所以选择时必须谨慎。基本上所有的LDO应用中引起的振荡都是由于输出电容的ESR过高或过低。

LDO的输出电容,通常钽电容是最好的选择(除了一些专门设计使用陶瓷电容的LDO,例如:LP2985)。测试一个AVX的4.7uF钽电容可知它在25℃时ESR为1.3Ω,该值处在稳定范围的中心(图16)。

另一点非常重要,AVX电容的ESR在-40℃到+125℃温度范围内的变化小于2:1。铝电解电容在低温时的ESR会变大很多,所以不适合作LDO的输出电容。

必须注意大的陶瓷电容(≥1uF)通常会用很低的ESR(<20mΩ),这几乎会使所有的LDO稳压器产生振荡(除了LP2985)。如果使用陶瓷电容就要串联电阻以增加ESR。大的陶瓷电容的温度特性很差(通常是Z5U型),也就是说在工作范围内的温度的上升和下降会使容值成倍的变化,所以不推荐使用。

准LDO补偿

准LDO(图3)的稳定性和补偿,应考虑它兼有LDO和NPN稳压器的特性。因为准LDO稳压器利用NPN导通管,它的共集电极组合也就使它的输出极(射极)看上去有相对低的阻抗。

然而,由于NPN的基极是由高阻抗PNP电流源驱动的,所以准LDO的输出阻抗不会达到使用NPN达林顿管的NPN稳压器的输出阻抗那样低,当然它比真正的LDO的输出阻抗要低。

也就是说准LDO的功率极点的频率比NPN稳压器的低,因此准LDO也需要一些补偿以达到稳定。当然了这个功率极点的频率要比LDO的频率高很多,因此准LDO只需要很小的电容,而且对ESR的要求也不很苛刻。

例如,准LDO LM1085可以输出高达3A的负载电流,却只需10uF的输出钽电容来维持稳定性。准LDO制造商未必提供ESR范围的曲线图,所以准LDO对电容的ESR要求很宽松。

低ESR的LDO

国半(NS)的两款LCO,LP2985和LP2989,要求输出电容贴装象陶瓷电容一样超低ESR。 这种电容的ESR可以低到5~10mΩ。 然而这样小的ESR会使典型的LDO稳压器引起振荡(图18)。

为什么LP2985在如此低ESR的电容下仍能够稳定工作? 国半在IC内部放置了钽输出电容来补偿零点。这样做是为了将可稳定的ESR的上限范围下降。LP2985的ESR稳定范围是3Ω到500MΩ,因此它可以使用陶瓷电容。未在内部添加零点的典型LDO的可稳定的ESR的范围一般为100mΩ-5Ω,只适合使用钽电容并不适合使用陶瓷电容。

要弄清ESR取之范围上限下降的原因,请参考图15。上文提到,此LDO的零点已被集成在IC内部。因此外部电容产生的零点必须处在足够高的频率,这样就不能使带宽很宽。否则,高频极点会产生很大的相移从而导致振荡。

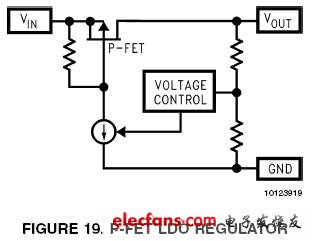

使用场效益管(FET)作为导通管LDO的优点

LDO稳压器可以使用P-FET(P沟道场效应管)作为导通管(图19:P沟道场效应管LDO内部结构框图)。为了阐述使用Pl-FET LDO 的好处,在PNP LDO(图2)中要驱动PNP功率管就需要基极电流。基极电流由地脚(ground pin)流出并反馈回反相输入电压端。因此,这些基极驱动电流并未用来驱动负载。它在LDO稳压器中耗损的功耗由下式计算:

PWR(Base Drive)=Vin × Ibase (11)

图19

需要驱动PNP管的基极电流等于负载电流除以β值(PNP管的增益)。在一些PNP LDO稳压器中β值一般为15~20(与负载电流相关)。此基极驱动电流产生的功耗可不是我们期望的(尤其是在电池供电的低功耗应用中)。P沟道场效应管(P-FET)的栅极驱动电流极小,较好地解决这个问题。

P-FET LDO稳压器的另一个优点,是通过调整场效应管(FET)的导通阻抗(ON-resistance)可以使稳压器的跌落电压更低。 对于集成的稳压器而言,在单位面积上制造的场效应功率管(FET power transistors)的导通阻抗会比双极型开关管(Bipolar ONP Devices)的导通阻抗低。这就可以在更小封装(Packages)下输出更大的电流。

上一页1234全文

本文导航

- 第 1 页:LDO的工作原理详细分析

- 第 2 页:回路增益

- 第 3 页:波特图分析

- 第 4 页:ESR 和稳定性

- LDO的工作原理详细分析 - 全文 - 稳压电源 - 电子发烧友网

最后

以上就是负责手套最近收集整理的关于LDO的工作原理详细分析 - 全文(反馈才能稳定)用到带隙参考源的全部内容,更多相关LDO的工作原理详细分析内容请搜索靠谱客的其他文章。

发表评论 取消回复