实验内容一

使用Veriog - HDL 语言,DE0 FPGA 开发板 按照如下要求设计一个计数器电路 。

功能描述

在 DE0 开发板的 最右侧 的 HEX LED 数码管上,进行计数并用十进制数进行显示。计数器特征如下

只能使用一个50MHz的时钟信号,不要有计数器分频的信号作为时钟

该计数器在电路复位后会循环的从0值递增计数到最大值,计数最大值是一个循环变化的过程,计数器复位之后,第一次计数最大值是6,然后是7、8、9,然后计数最大值又变成6,如此往复循环, 计数数值变化的时间间隔是1秒 ,计数过程如下所示:

| 0 1 … 6 | 0 1… 7 | 0 1 … 8 | 0 1 … 9 | 0 1 … 6 | …… |

|---|

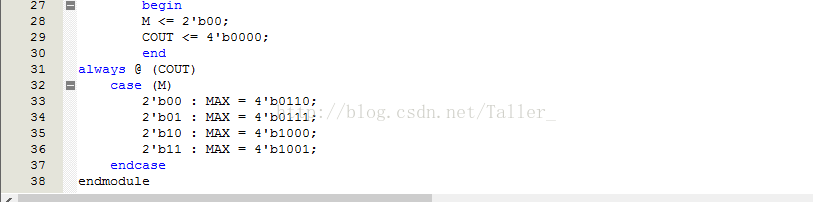

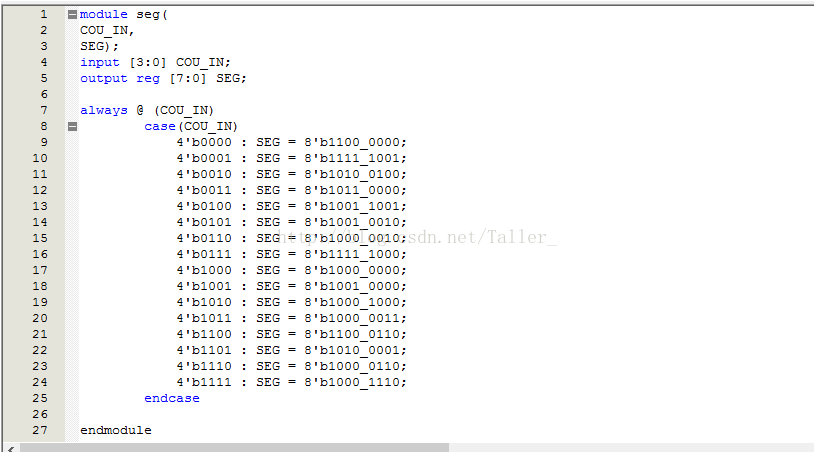

由于上一个实验已经在Quartus上模拟了这次实验要实现的功能,所以在这次的重点在于把他下载到硬件上来实现,所以首先我们要产生一个1s的时钟信号,接下来对这1s的时钟信号进行计数,分别完成0-6,0-7,0-8,0-9,0-6的循环操作,把他们的输出经过译码器变成硬件上能显示的数字,在数码管上显示出来。

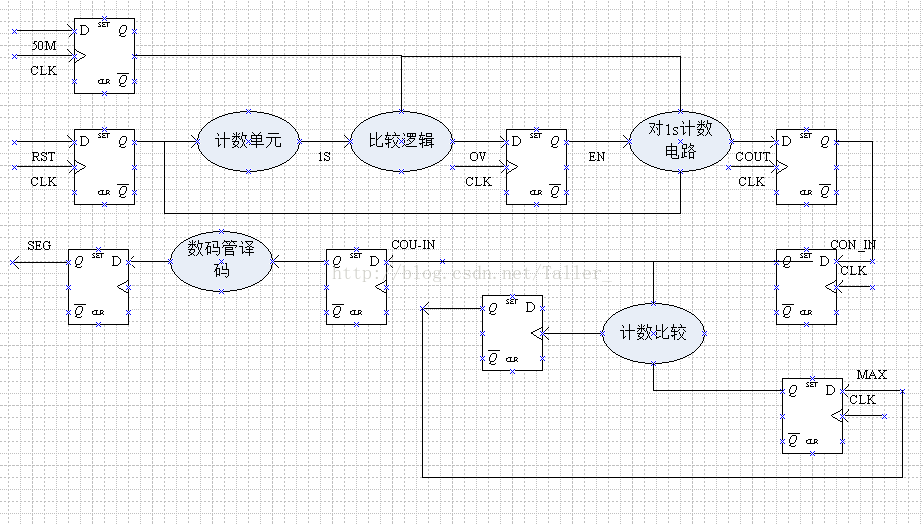

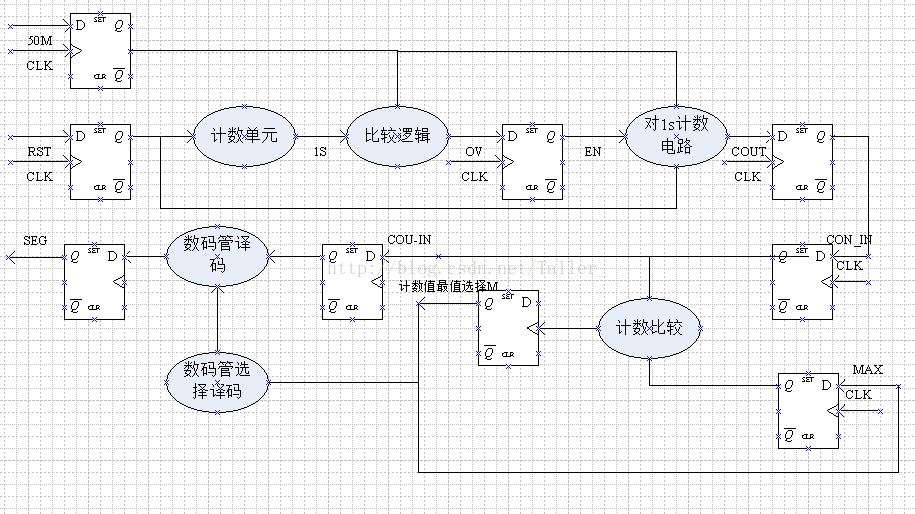

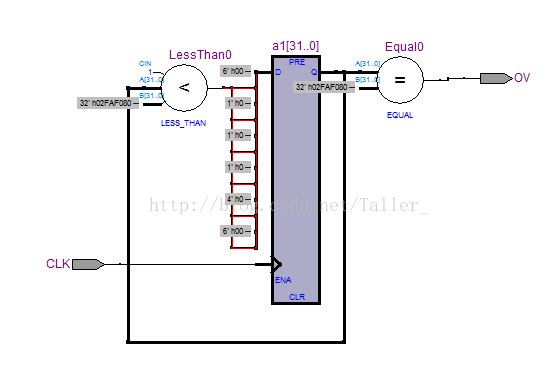

1、手工绘制的RTL图

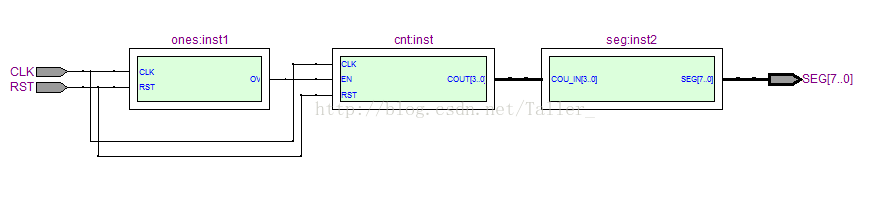

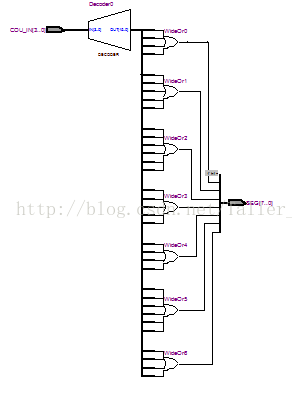

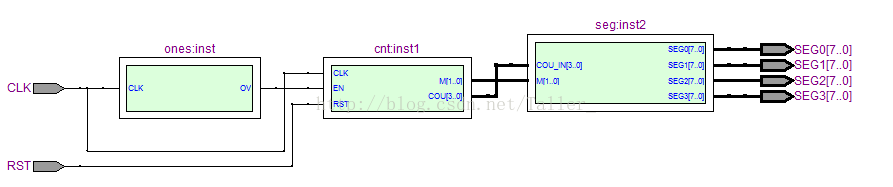

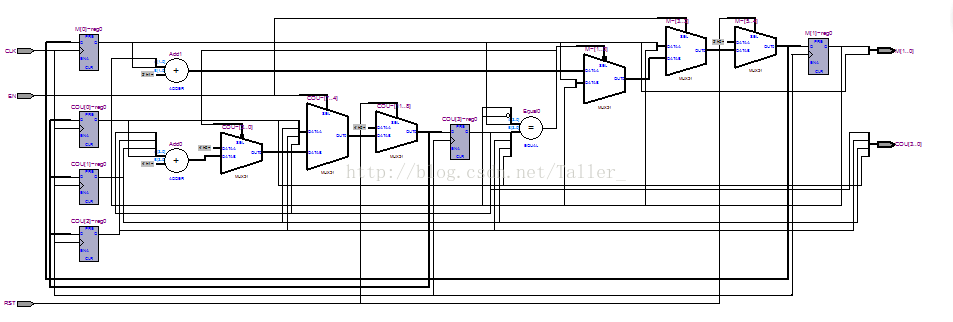

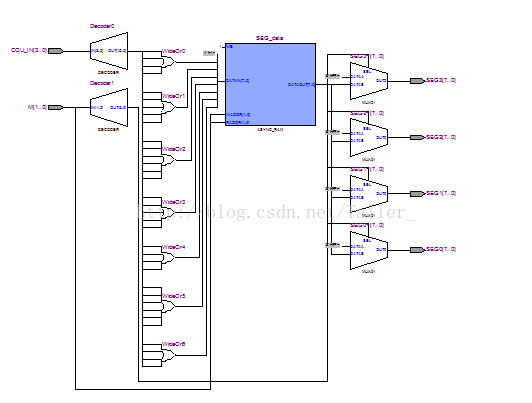

2、Quartus扫描生成的电路RTL图

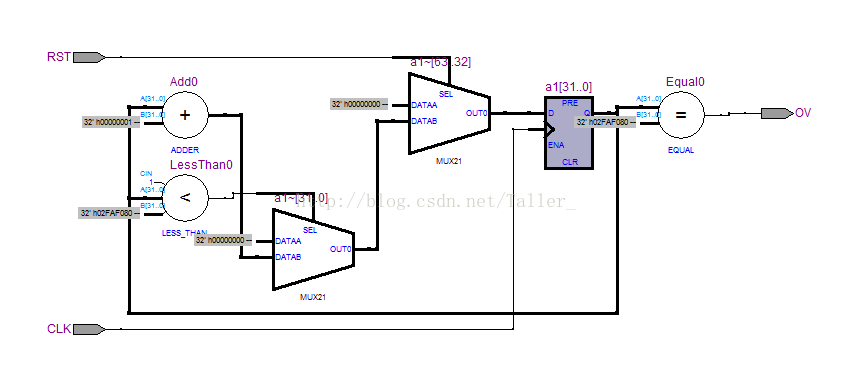

总体RTL图及各部分电路RTL图

3、SignalTap截图

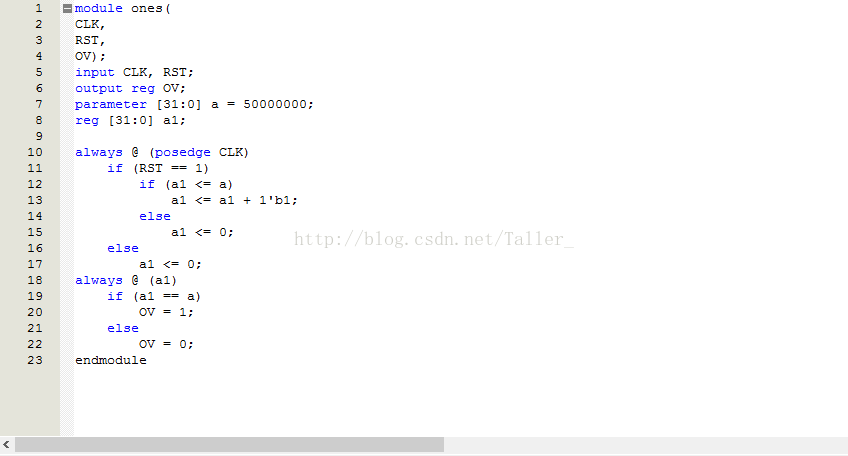

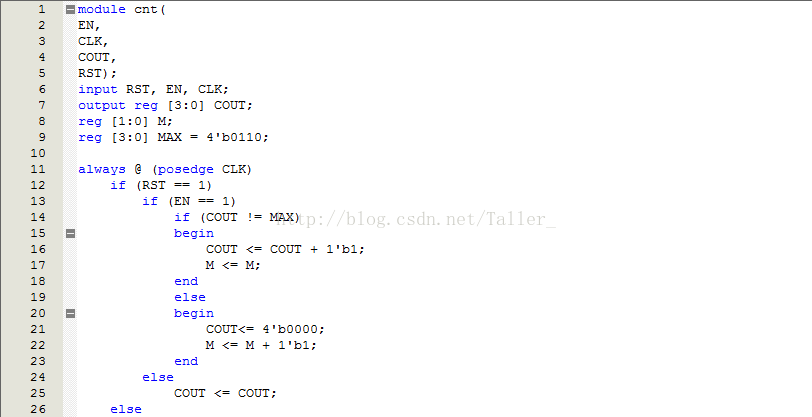

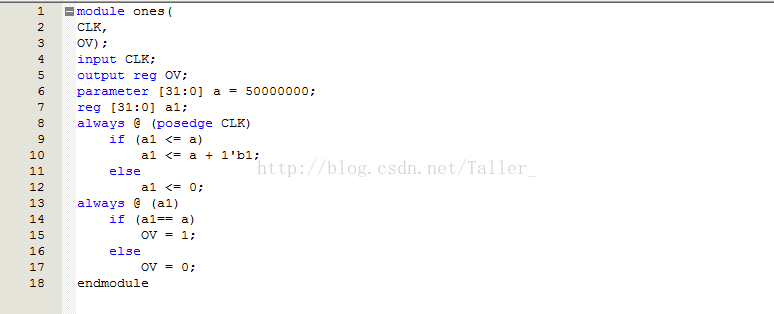

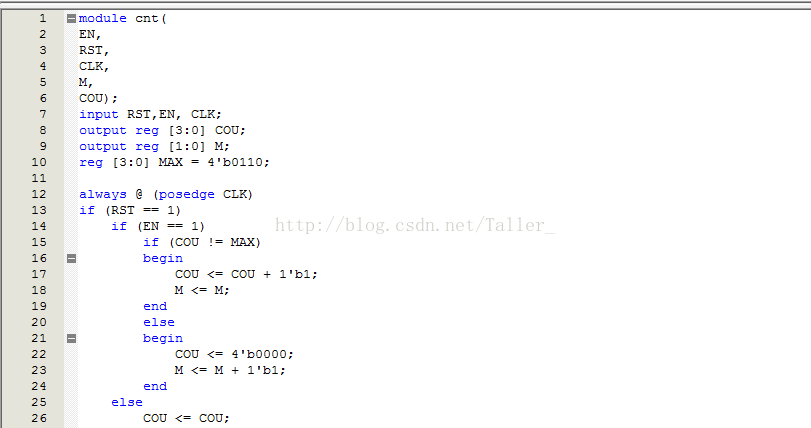

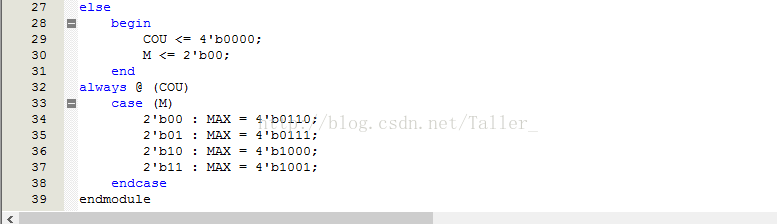

4、源代码

基准电路/计数单元/译码电路

实验内容二

在 DE0 开发板的 从左到右 的 4个HEX LED 数码管上,进行计数并用十进制数进行显示。计数器特征如下

- 只能使用一个50MHz的时钟信号,不要有计数器分频的信号作为时钟

- 系统复位后全部HEX LED熄灭

- 左1 LED,显示 0、1、2 ~6 ,然后熄灭

- 左2 LED,显示 0、1、2 ~7 ,然后熄灭

- 左3 LED,显示 0、1、2 ~8 ,然后熄灭

- 最右侧 LED,显示 0、1、2 ~9 ,然后熄灭

- 然后再开始左1 LED, 显示 0、1、2~6 如此一直循环。

- 所有情况下,计数数值变化的时间间隔是1秒

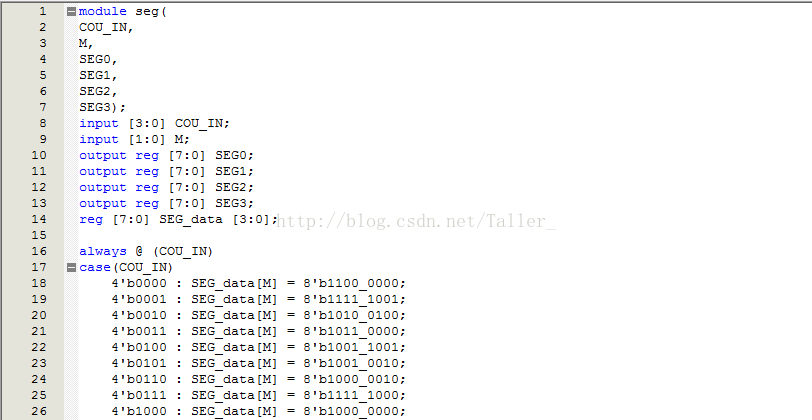

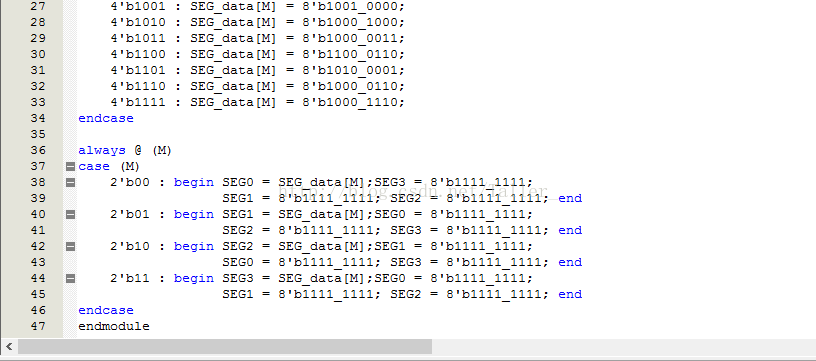

和实验一相比,实验二将在一个数码管上现实的数字变成了显示在四个数码管上,这样我们就需要增加译码器的数量,从一个变成四个。我们加入对译码器的选择就可以方别满足在不同数码管上显示数字。

1、手工绘制的RTL图

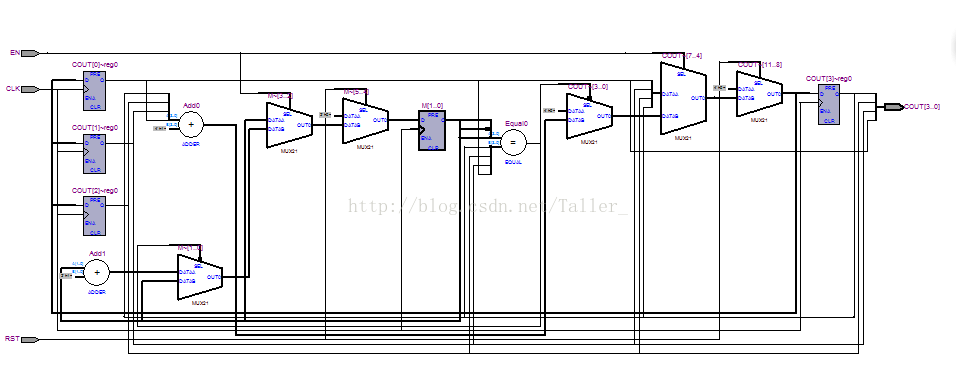

2、Quartus扫描生成的电路RTL图

总体RTL图和各部分RTL图

3、源代码

最后

以上就是粗犷黑裤最近收集整理的关于计数器 FPGA 电路实验 作业的全部内容,更多相关计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复